Логический анализатор

Иллюстрации

Показать всеРеферат

ЛОГИЧЕСКИЙ АНАЛИЗАТОР, содержащий первый и второй цифроаналоговый преобразователи, осциллограф , к входу подсвета которого подключен щуп, выходы первого и второго цифро-аналоговых преобразователей соединены соответственно с входами вертикального и горизонтального отклонения луча осциллографа, отличающийся тем, что, с целью повышения производительности контроля, В него введены счетчик, шифратор, переключатель, первый и второй мультиплексоры , выходы которых соединены соответственно с входами первого и второго цифро-аналоговых преобразователей , подвижный контакт переключателя соединён с шиной нулевого потенциала , неподвижные контакты переключателя соединены соответственно с инверстными входами шифратора, первый выход которого соединен с адресным входом первого мультиплексора, второй и третий выходы шифратора соединены соответственно с адресными входамивторого мультиплексора, вход синхронизации и начальной установки логического анализатора соединены со счетным входом и входом установки в ноль соответственно счетчика и контролируемой схемы, информационные входы логического анализатора соединены соответственно с инi формационными входами контролируемой схемы и второй группой информаци л онных входов второго мультиплексора, выходы контролируемой схемы соединены соответственно с первой группой информационных входов первого муль§ типлексора и с третьей группой информационных входов второго мультиплексора , группа контрольных точек контролируемой схемы соответственно с второй группой информационных входов первого мультиплексора и четвертой группой информационных входов второго мультиплексора, щуп подклю05 чен к соответствующей контрольной Э) точке контролируемой схемы.

СОЮЗ СОВЕТСНИХ

СО(.1ИАЛИСТИЧЕСН1)1Х

РЕСПЮЛИН (19) (11) А з(59 G 06 F 11100

ГОСУДАРСТВЕННЫЙ ИОМИТЕТ СССР

ПО ДЕЛИЮ ИЗОБРЕТЕНИЙ И ОтНРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ й. а424)Р2 ";

) - (21) 3507738/18-24 (22) 27.09.82 (46) 30.08.84. Бюл. В 32 (72) М.А.Гладштейн, В.М.Комаров и Н.А.Шубин .(71) Рыбинский авиационный технологический институт (53) 681.3(088.8) (56) 1. Никитюк Н Н. Микропроцессоры и микро-ЭВМ.

2. Соботка 3., Старн Я. Микропроцессорные системы, М, Энергоиздат, 1981, с. 438-44 1(прототип). . (54)(57) ЛОГИЧЕСКИЙ АНАЛИЗАТОР, содержащий первый и второй цифроаналоговый преобразователи, осциллограф, к входу подсвета которого подключен щуп, выходы первого и второго цифро-аналоговых преобразователей соединены соответственно с входами вертикального и горизонтального отклонения луча осциллографа, о т л и ч аю шийся тем, что, с целью повышения производительности контроля, в него введены счетчик, шифратор, переключатель, первый и второй мультиплексоры, выходы которых соединены соответственно с входами первого и второго цифро-аналоговых преобразователей, подвижный контакт переключателя соединен с шиной нулевого по) тенциала, неподвижные контакты переключателя .соединены соответственно с инверстными входами шифратора, первый выход которого соединен с адресным входом первого мультиплексора второй и третий выходы шифратора соединены соответственно с адресными входами второго мультиплексора, вход синхронизации и вх(1д начальной установки логического анализатора соединены со счетным входом и входом установки в ноль соответственно счетчика и контролируемой схемы, информационные входы логического анализатора соединены соответственно с информационными входами контролируе" мой схемы и второй группой информационных входов второго мультиплексора, выходы контролируемой схемы соединены соответственно с первой группой информационных входов первого мультиплексора и с третьей группой информационных входов второго мультиплексора, группа контрольных точек рф, контролируемой схемы соответственно

I с второй группой информационных входов первого мультиплексора и четвертой группой информационных входов второго мультиплексора, .щуп подключен к соответствующей контрольной точке контролируемой схемы.

1111166 кения луча осциллографа, введены счетчик, шифратор, переключатель, первый и второй мультиплексоры, выход ды которых соединены соответственно с входами первого и второго цифро-аналоговых преобразователей, подвижный контакт переключателя соединен с шй ной нулевого потенциала, неподвижные контакты переключателя соединены

t0 соответственно с инверсными входами шифратора, первый выход которого соединен с адресным входом первого мультиплексора, второй и третий выходы шифратора .соединены соответственно с адресными входами второго мультиплексора, вход синхронизации и вход начальной установки логического анализатора соединены со счетным входом и входом установки

2р в ноль соответственно счетчика и контролируемой схемы, информационные входы логического анализатора соединены соответственно с информационными входами контролируемой схе25 мы и второй группой информационных входов второго мультиплексора, выходы контролируемой схемы соединены соответственно с первой группой информационных входов первого мультиплексора и стретьей группой информационных входов второго мультии плексора, группа контрольных точек контролируемой схемы соединена соответственно с второй группой информационных Входов nepBoro Mym THплексора и четвертой группой информационных входов второго мультиплексора, щуп подключен к соответствующей контрольной точке контролируе4 мой схемы.

Изобретение относится к области вычислительной техники и может быть использовано для контроля цифровых устройств.

Известны логические анализаторы, содержащие оперативное запоминающее устройство и электронно-лучевую трубку 1,12.

Недостатком таких анализаторов является низкая производительность контроля цифровых устройств, обусловленная возможностью представления информации лишь в виде временных диаграмм.

Наиболее близким по технической сущности к изобретению является логический анализатор, содержащий пос. ледовательно соединенные пороговые схемы по числу бит входной последовательности,N триггеров и N запоминающих устройств, блок управления пороговыми схемами,цифро-аналоговые преобраэова тели (ЦАП) и осциллограф, причем первые входы пороговых элементов являются информационными входами анали затора, выход блока управления поро» говыми элементами соединен с вторыми входами пороговых схем, вход

"Пуск" логического анализатора соеди нен с входом установки в ноль триггеров, а синхровход соединен с такто выми входами триггеров и управляющим входами запоминающих устройств, выхо ды которых соединены соответственно с входами цифроаналоговых преобразователей, выходы которых соединены с входами осциллографа и являются выхо дами устройства Г21.

Недостатком известного логическог анализатора является низкая произво" дительность контроля, так, совместныи анализатор нескольких временных диаграмм, необходимый для определения,, например, последовательности входных или выходных сигналов, при количестве сигналов более трех становится зат-, 45 руднительным.

Цель изобретения — повьппение про-. изводительности контроля цифровых устройств.

Поставленная цель достигается тем, что в логический анализатор, сбдержащий первый и второй цифроаналоговые преобразователи, осциллограф, к входу подсвета которого подключен щуп, выходы первого и второго 55 цифро-аналоговых преобразователей соединены соответственно с входами вертикального и горизонтального откло"

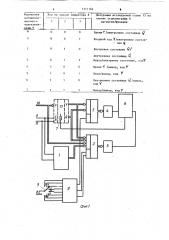

На фиг. 1 представлена блок-схема логического анализатора; на фиг. 2— примеры диаграмм, получаемых с его помощью при контроле некоторых цифровых схем: а — диаграмма время-выход четырехразрядного двоичного счетчика; сà — диаграмма вход-выход комбинационного преобразователя кода

8-4-2-1 в код 2-4-2-1, 2; Ь вЂ” диаграмма выход-выход для автомата

Уилкса.

Устройство содержит счетчик 1, первый и второй мультиплексоры 2,3, первый и второй ЦАП 4,5, осциллограф 6, щуп 7, шифратор 8, переключатель 9, группу информационных входов 10, вход 11 синхронизации и вход 12 начальной установки.

111 1166

Логический анализатор работает следующим образом, Режим работы его задается переключателем 9, в соответствии с положением которого на выходе шифратора

8 формируется код управления. Значе-. ние первого разряда кода поступает на управляющий вход первого мульти-, плексора 2, а.второго и третьего раз-. рядов — на управляющие входы второго мультиплексора 3. Мультиплексор

2 пропускает на вход первого ЦАП 4 код выходного сигнала или код состояния группы контрольных точек кон-. тролируемой схемы 13, в соответствии с которым ЦАП 4 формирует сигнал вертикальной развертки осциллографа 6. Мультиплексор 3 пропускает на вход второго ЦАП 5 код с выхода счетчика 1 или код с группы информацион4 ных входов 10 устройства, или код состояния группы контрольных точек схемы 13, или код выходного сигнала схемы 13, в соответствии с каждым из которых ЦАП 5 формирует сигнал горизонтальной развертки осциллографа 6.

Таким образом, на экране осциллографа могут отображаться в виде точек ,следующие диаграммы исследуемой схемы 13, представленные в таблице.

Режимы, отмеченные знаком, эффективно используют при большой размерности кодов выходного сигнала и группы контрольных точек, причем младшие разряды кодов поступают на второй мультиплексор 3, а старшие — на первый мультиплексор 2 ° .

При проведении анализа контролируемая схема 13 находится в рабочем режиме, на нее поступают рабочие входные сигналы, сигнал синхронизации и сигнал запуска. Эти сигналы обеспечиваются системой, частью которой является контролируемая логическая схема.

Сигнал запуска периодически сбрасывает в исходное состояние схему 13 и счетчик, заставляя их всякий раз работать, начиная с. исходного состояния. Выбирая определенный режим отображения, оператор имеет возможность получить на экране осциллографа 6 требуемую диаграмму. По характеру отображаемой диаграммы можно судить о правильности работы контролируемой схемы, а также по искажению диаграмм производить диагностику неисправностей.

Диаграммы на экране-.осциллографа 6 предстаавляют собой набор точек, расположенных в углах координатной: сетки, которые могут подсвечиваться.

Примеры схем и получаемые при этом диаграммы показаны на фиг. 2 (здесь п =4). Координаты точек указаны в шестнадцатиричной системе счис5

1О также с использованием шупа сократить время на диагностику и локализацию неисправностей.

55 ления.

По таким диаграммам, оценивая расположение точек по отношению к координатной сетке, можно оценить пра15 вильность работы контролируемой схемы.

Для определения значения конкретного сигнала по отклонению луча в данном устройстве используется канал

20 подсвета луча, а выбор исследуемого сигнала производится щупом 7 осциллографа (см. третью диаграмму, где в качестве исследуемого сигнала микропрограммного автомата Уилкса выбран

25 один из сигналов М и по яркости свечения точек можно определить, каким адресом микрокоманды соответствует уровень "1", а каким уровень "О", Это позволяет определить логические значения различных сигналов по отношению к входным, выходным комбинациям или внутреннему состоянию схемы.

Таким образом, сравнивая диаграмму, полученную с реальной схемы, с эта-— лонной, можно не только установить правильно ли функционирует схема но

Э и диагностировать неисправность. Это значительно снижает трудоемкость работ по анализу работы сложных вычис40 лительных устройств, а следовательно повышает производительность их контроля, Особенно эффективно применение таких устройств для анализа микропроцессорных систем.

45 Использование предлагаемого устройства позволяет наблюдать на экране осциллографа 8 типов диаграмм, обладающих в и раз большей информативностью, чем временные диаграммы (здесь и разрядность мультиплексора, реально З п 8) . Высокая информатив» ность предложенного анализатора позволяет более чем в и раз сократить время анализа исследуемой схемы, а

Время 6 /внутреннее состояние

Внутренее состояние Я/

Время 1 /выход, код Y

exxon/ss mmoop, swoop У

0 Выход/выход, код

Йопохеиия

9L"емипоэи июнного переключа .хаи 2.

S 1111166 а

Код на выходе шифратора 8 Диаграмма исследуемой схемы 13 HB.

Входной код Х/внутреннее состояние Я внутреннее состояние Я

Выход/внутренее состояние, код .

Внутреннее состояние Ц /выход, код Y

lllll66 с ч» с»- ъ» з ь а а»»»ъ » ъ»»» ч»ь »е

ВНИИПИ Заказ 6311/39

Тнраа 698 Подписное

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4