Преобразователь напряжения в частоту

Иллюстрации

Показать всеРеферат

ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ В ЧАСТОТУ, содержащий компаратор, элемент И-НЕ, интегратор, первьй вход которого является входом устройства ,, a выход подключен к входу ком-паратора , генератор тактовой частоты, первьй триггер, выход которого подключен к первому входу элемента И-НЕ, источник эталонного тока,и коммутатор , выход которого подключен к второму входу интегратора, отличающийся тем, что, с целью повышения точности, в него введены два элемента И, второй, третий и четвертый триггеры, элемент задержки. одновибратор, и реверсивный переключатель , причем первый вход первого элемента И подключен к выходу генератора тактовой частоты, выход первого элемента И через первый триггер подключен к первому входу второго элемента И, выход которого через второй триггер подключен к второму входу элемента И-НЕ, выход которого подключен к управлякнцему входу коммутатора, и через элемент задержки - к счетному входу третьего триггера, выход компаратора подключен к R-входам третьего и четвертого триггеров и является выходом устройства, первый выход третьего триггера подключен к второму входу второго элемента И и к управлякнцему входу реяерсивного переключателя, второй выход третьего триггера через одновибратор подключен к S-входу четвертого триггера, выход которого подключен к второму входу первого элемента И, a источник эталонного тока через реверсивный переключатель подключен к аналоговому входу коммутатора. ND СЛ СО

СОЮЗ СОВЕТСНИХ

ВСВЕВЕ

РЕСПУБЛИК..Я0„„1111

369 Н 03 К 13/20

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н PBTOPCNOMV СВЕЕЕТВВСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3543409/18-21 (22) 19.01.83 (46) 30.08.84. Бюл. Р 32 (72) В.И. Волков, А.В.Голубев, А.Г.Петров и Е.ВВШумаров (53) 681.325(088.8) (56) 1. Авторское свидетельство СССР

В 738156, кл. Н 03 К 13/20, 1980.

2. "Radio fernsehen elektronik", 1977, М 15, с. 509, рис. 6а. (54)(57) ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ

В ЧАСТОТУ, содержащий компаратор, элемент И-НЕ, интегратор, первый вход которого является входом устройства,, а выход подключен к входу ком-паратора, генератор тактовой частоты, первый триггер, выход которого подключен к первому входу элемента И-НЕ, источник эталонного тока,и коммутатор, выход которого подключен к второму входу интегратора, о т л ич а ю шийся тем, что, с целью повьппения точности, в него введены два элемента И, второй, третий и четвертый триггеры, элемент задержки, одновибратор, и реверсивный переключатель, причем первый вход первого элемента И подключен к выходу генера-. тора тактовой частоты, выход первого элемента И через первый триггер подключен к первому входу второго элемента И, выход которого через второй триггер подключен к второму входу элемента И-НЕ, выход которого подключен к управляющему входу коммутатора, и через элемент задержки — к счетному входу третьего триггера, выход компаратора подключен к R-входам третьего и четвертого триггеров и является выходом устройства, первый выход третьего триггера подключен к второму входу второго элемента И и к управеняющему входу реверсивного переключателя, второй выход третьего триггера через одновибратор подключен к S-входу четвертого триггера, выход которого подключен к второму входу первого элемента И, а источник эталонного тока через реверсивный переключатель подключен к аналоговому входу коммутатора.

1111253

Изобретение относится к области информационно-измерительной техники, в частности к преобразователям напряжения в частоту, и может быть использовано в системах управления с аналого-цифровым преобразованием информации. Известен преобразователь напряжения в частоту, содержащий интегратор, компаратор, два триггера, генератор 1О тактовых импульсов, два логических элемента совпадения, два источника опорного напряжения и два ключа Н1.

Непостатком такого устройства является невысокая точность преобразования.

Наиболее близким по технической сущности к предлагаемому является преобразователь напряжения в частоту, содержащий интегратор, выход которого 2р через компаратор подключен к D-входу триггера, выход которого. подключен к управляющему входу коммутатора,и первому входу элемента И-НЕ, генератор тактовой частоты, выход которого

Ъ подключен к второму входу элемента И-НЕ и счетному входу триггера, источник эталонного тока, подключенный через коммутатор к входу интегратора С23.

Недостатком известного устройства является низкая точность из-за влияния нестабильности задержек срабатывания триггера и коммутатора на эталонный интервал времени.

Цель изобретения — повьипение точности, Поставленная цель достигается тем, что в преобразователь напряжения в частоту, содержащий компаратор, эле- 4О мент И-НЕ, интегратор, первый вход которого является входом устройства, а выход подключен к входу компаратора, генератор тактовой частоты, первый триггер, выход которого подклю- 4 чен к первому входу элемента И-НЕ, источник эталонного тока и коммутатор, выход которого подключен к второму входу интегратора, введены два элемента И, второй, третий и четвертый триггеры, элемент задержки, одновибратор H реверсивный переключатель,. причем первый вход первого элемента -И подключен к выходу генератора тактовой частоты, выход первого эле мента И через первый триггер подключен к первому входу второго элемента И, выход которого через второй триггер подключен к второму входу элемента И-НЕ, выхоД которого подключен к управляющему входу колМутатора и через элемент задержки к счетному входу третьего триггера, выход ком- паратора подключен к R-входам третьего и четвертого триггеров и является выходом устройства, первый выход третьего триггера подключен к второму входу второго эЛемента И и к управляющему входу реверсивного переключателя, второй выход третьего триггера через .одновибратор подключен к S-аходу четвертого триггера, выход которого подключен к второму входу первого элемента И, а источник эталонного тока через реверсивный переключатель подключен к аналоговому входу коммутатора.

Г"

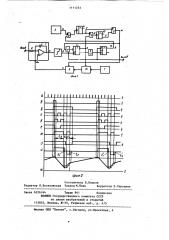

На фиг. 1 представлена структурная схема устройства; на фиг. 2 временные диаграммы, поясняющие работу устройства.

Устройство содержит интегратор 1, первый вход которого является входом устройства, а выход подключен к входу компаратора;2, генератор 3 тактовой частоты, первый триггер 4, выход которого подключен к первому входу элемента И-НЕ 5, коммутатор 6, источ-! ник 7 эталонного тока, выход коммутатора 6 подключен к второму входу интегратора 1, два элемента И 8 и 9, второй триггер 10, элемент 11 задержки, третий триггер 12, одновибратор 13, четвертый триггер 14 и реверсивный переключатель 15. Первый вход первого элемента И 8 подключен к выходу генератора тактовой частоты 3, выход первого элемента И 8 через первый триггер 4 .подключен к первому входу второго элемента И 9, выход которого через второй триггер подключен к второму входу элемента И-НЕ 5.

Выход элемента И-НЕ 5 подключен к управляющему входу коммутатора 6 . и через элемент задержки 11 к счетному входу третьего триггера 12, выход компаратора 2 подключен к R-входам третьего 12 и четвертого 14 триггеров и является выходом устройства.

Первый выход третьего триггера 12 подключен к второму входу второго элемента И 9 и к управляющему входу реверсивного переключателя 15, второй выход третьего триггера 12 через одновибратор 13 подключен к. S-входу четвертого триггера 14, выход кото(Ф.1111253 рого подключен к второму входу первого элемента И 8. Источник эталонного тока 7 через реверсивный переключатель 15 подключен к аналоговому входу коммутатора 6.

Устройство работает следующим образом.

Под воздействием постоянного входного напряжения U< напряжение на выходе интегратора 1 нарастает линейно до порога срабатывания компаратора 2 (флг. 2к), который формирует выходной импульс (фиг. 2б), подтверждающий исходное состояние третьего триггера 12 и устанавливающий четвертый триггер 14 в исходное состояние (фиг. 2в). Генератор 3 вырабатывает тактовую частоту (фиг. 2а),поступаю- щую на вход управляемого делителя, образованного первым и вторым элементами И 8 и 9, первым 4 и вторым 10 триггерами. Четвертый триггер 14, устанавливаясь в исходное состояние, разрешает прохождение тактовых импульсов через первый элемент И 8, и на выходах первого 4 и второго 10 триггеров появляются импульсы, соответствующие деленной тактовой частоте (фиг. 2г,е). На выходе элемента И-НЕ 5 по спаду первого триггера 4 начинает формироваться эталонный временной интервал t (фиг. 2ж). В момент, когда при дальнейшем счете на выходах первого 4 и второго 10 триггеров появляются уровни "1", заканчивается формирование эталонного интервала и на выходе элемента И-НЕ 5 по фронту и спаду первого триггера 4 формируется интервал паузы t (фиг. 2ж). В течение эталонногс интервала времени э открыт коммутатор 6, и ток источника эталонного тока 7 через реверсивный переключатель 15 в положительном направлении проходит на второй вход интегратора. 1, снимая с его конденсатора эталонный заряд. Напряжение на выходе интегратора 1 уменьшается пропорционально эталонному заряду (фиг. 2к) .

Во время интервала паузы t коммутатор 6 закрыт, а третий триггер 12 срабатывает по сигналу элемента И-HE 5, задержанному элементом 11 г задержки, и через переключатель 15 меняет полярность источника 7 (фиг. 2з, и). Одновременно второй элемент И 9 запрещает прохождение импульсов на вход второго триггера 10 (фиг. 2ж) . Поэтому следующий импульс с выхода первого триггера 4 проходит через элемент И-НЕ 5 и образует (корректрирующий интервал йк (фиг. 2ж, и), в течение которого коммутатор 6 открыт и эталонный ток обратного направления проходит на второй вход интегратора 1, увеличи- вая заряд его конденсатора и выход1О ное напряжение (фиг. 2 и, к). По окон чании корректирующего интервала закрывается коммутатор 6, с задержкой обратно срабатывает третий триг» гер 12-и через реверсивный переключатель 15 восстанавливае; исходную полярность подключения источника эталонного тока 7. При этом одновибратор 13 формирует короткий импулвс, 20 сбрасывающий четвертый триггер 14, который через первый элемент И 8 закрывает вход управляемого делителя (фиг. 2в,г) .Далее процесс пбвторяется.

Таким образом,в предлагаемом

25 устройстве начало и конец каждого из временных интервалов (фиг. 2 и) протекания эталонного тока на вход интегратора 1 определяются срабатыванием одних и тех же элементов:

3р первого элемента И 8, первого триггера 4, элемента И-НЕ 5 и коммутатора 6. Если, например, нестабильность задержки заднего фронта приведет к увеличению эталонного интервала tу (моменты „, tq на фиг. 2и),то соответствующее увеличение эталонного заряда компенсируется в течение корректирующего интервала t<, поскольку tz увеличивается на то же время, 4О что и t®, но полярность эталонного тока при этом меняется (моменты tg fg на фиг. 2 и; пунктир на фиг. 2 к) .

Рассмотренная составляющая погрешнос.ти не влияет на выходную частоту пре45 образователя.

На основании изложенного передаточная функция преобразователя:

Ц

-вы р . 3. (t„) где К вЂ” входное сопротивление интегратора 1;

? — ток источника 7.

Использование изобретения позволит устранить влияние задержек срабаты5 вания логических элементов и коммутатора и повысить точность преобразователя, особенно для больших коэффициентов преобразования и, соответственно,малых эталонных интервалов времени.

3 131253 фМР. 1

Составитель В.Пешков

Редактор Л.Веселовская Техред И.Надь Корректор Е.Сирохман

Заказ 6326/44 Тираж 861 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", r.Óæãîðîä, ул.Проектная, 4