Адаптивное дуплексное устройство для передачи и приема фазоманипулированных сигналов

Иллюстрации

Показать всеРеферат

СООЗ СОВЕТСКИХ .

Og

РЕСПУБЛИК (19) 01) За)) Н 04 4 27 18

1 )- »: ор

ОГ)ИСАНИЕ ИЗОБРЕТЕНИЯ " -;::- 1

К ABTOPGHOMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ HOMHTET СССР

ПО ДЕЛАМ ИЭОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3614468/18-09 (22) 30.06.83 (46) 30.08.84. Бюл. У 32 (72) В.Б.Малинкин (71) Новосибирский электротехнический институт связи им. Н.Д.П )урцева (53) 621.394.14(088.8)

Ф (56) 1.. Чепиков А.М. и др. Передача дискретной информации по кабелям ГТС.

М., "Связь", 1979, с. 22.

2. Stanley А. Mhite. An adaptive

Electronic Hybrid Transformers

IREE Transaction on Co unicationsp

1972, Песember, У6, р. 1184-1188 (прототип). (54)(57) АДАПТИВНОЕ ДУПЛЕКСНОЕ УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА ФАЗОМАНИПУЛИРОВАННЦХ СИГНАЛОВ,. содержащее источник сообщения, информационный выход которого соединен с входом кодера, выход которого соединен с входом передатчика, выход которого подключен к входу входного согласующего .блока, выход которого соединен с первым входом вычитателя, и приемник, выход которого подключен к входу получателя сообщения, о т л и— ч а ю щ е е с я тем, что, с целью. повышения скорости передачи,в устройство введены первый н второй .накопители, сумматор и ключ, выход которого соединен с первым входом второго накопителя, выход которого подключен к первому входу сумматора, второй вход которого соединен с выходом вычитателя, первый вход которого соединен с первым входом первого накопителя, второй. вход которого подключен к выходу кодера и к второму входу второго накопителя, выход сумматора подключен к входу приемника и к первому входу ключа, второй вход которого соединен с управляющим выходом источника сообщения, выход первого накопителя соединен с вторым входом вычитателя, причем первый и второй накопители содержат первые коммутаторы, линии задержки и вторые коммутаторы, первые входы которых подключены к выходам соответствующих линий задержки, входы которых соеди,нены с выходами первых коммутаторов, вторые входы которых соединены с вторыми входами вторых коммутаторОв и являются вторыми входами первого и второго накопителей, первыми входами которых являются первые входы первых коммутаторов, а выходами пер) ного и второго накопителей являются выходы вторых коммутаторов.

11112

Изобретение относится к электро" связи и может быть использовано в системах для передачи информации с фазовой модуляцией.

Известно устройство для дуплексной передачи данных, выполненное в виде эквивалентной мостовой схемы, где в одну диагональ моста включен передатчик, а в другую — приемник ь13.

В этом устройстве разделение сиг- 10 налов передатчика и приемника возмож- но при идеальна. сбалансированных сопротивлениях плеч мостовой схемы.

Из-за разброса параметров коммутируемого канала связи не удается полностью сбалансировать мостовую схему, поэтому сигналы собственного передатчика проникают в приемник, снижая помехоустойчивость последнего, что является недостатком устрой- 20 ства.

Наиболее близким к изобретению является адаптивное дуплексное устройство для передачи и приема фазоманипулированных сигналов, содержащее источник сообщения, информационный выход которого соединен с входом кодера, выход которого соединен с входом передатчика, выход которого

30 подключен к входу входного согласующего блока, выход которого соединен с первым входом вычитатателя, и приемник, выход которого подключен к входу получателя сообщения !2.1.

Однако это устройство обладает недостаточной скоростью передачи.

Цель изобретения — повышение скорости передачи.

Поставленная цель достигается тем, что в адаптивное дуплексное устройст40 во для передачи и приема фазоманипулированных сигналов, содержащее источник сообщения, информационный выход которого соединен с входом кодера, выход которого соединен с входом пере

4„ атчика, выход которого подключен входу входного согласующего блока, выход которого соединен с первым входом вычитателя, и приемник, выход которого подключен к входу получате- 50 ля сообщения, введены первый и вто.рой накопители, сумматор и ключ, выход которого соединен с первым входом второго накопителя, выход которого подключен к первому входу суммато- 5> ра, второй вход которого соединен с выходом вычитателя, первый вход которого соединен с первым входом

59 а первого накопителя, второй вход которого подключен к выходу кодера и к второму входу второго накопителя, выход сумматора подключен к входу приемника и к первому входу клю- ча, второй вход которого соединен с управляющим выходом источника сообщения, выход первого накопителя соединен с вторым входом вычитателя, причем первый и второй накопители содержат первые коммутаторы, линии задержки и вторые коммутаторы, первые входы которых подключены к выходам соответствукицих линий за-. держки, входы которых соединены с выхбдами первых коммутаторов, вторые входы которых соединены с вторыми входами вторых коммутаторов и являются вторыми входами пе вого и второго накопителей, первыми входами которых явю тются первые входы первых коммутаторов, а выходами первого и второго накопителей являются выходы вторых коммутаторов.

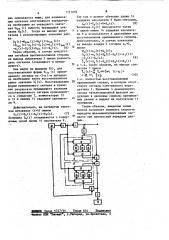

На чертеже изображена структурная электрическая схема предлагаемого устройства.

Устройство содержит передатчик 1, вычитатель 2, приемник 3, кодер 4, входной согласующий блок 5, первый накопитель 6, сумматор 7, ключ 8, второй накопитель 9, источник 10 сообщения, получатель 11 сообщения, первые коммутаторы 12, вторые коммутаторы 13, линии 14 задержки.

Устройство работает следующим образом.

Поток логических нулей и единиц преобразуется в кодере 4 в перекодированный сигнал, при этом три двоичные символа преобразуются в соответствукнцие два символа троичной системы счисления (Ъ4 Ь Ъь- »а4 а )

Ъ1 6 10, 1) а б (0,1,2j . В соответствии с каждым символом а„ передатчик 1 формирует фазоманипулированный сигнал по закону п (е) =п,см?®„ (t- ;)+ 4+а р3,(1) где бд — частота гармонического колебания;

- текущий момент времени; Я вЂ” начальная фаза передатчика; — i-й временной ичтервал формирования ФМ сигнала.

Сигнал с выхода передатчика 1 поступает в канал связи и одновременно во входной согласующий блок 5, в котором производится преобразова1111259

Таким образом, на выходе вычитате- ля 2 результирующее значение равно п 1 (t) =п,,„ (t) -n„(t)=0 . Так компенсиру:тся сигнал собственного передатчика, а вместо прежнего значения

n (t), которое хранилось в одной линии 14 задержки, вводится новое значение n„. »(t). Новое значение и; „ (t) храниться в одной линии 14 задержки до передачи очередного символа а + =0 5 и т.д. Так как сигналы собственного передатчика 1 n(t) взяты непосредственно из канала связи,. то n(t) в конечном счете определяется входными

/ параметрами Z „(t) канала связи.

Параметры Z« (t) можно считать постоянными относительно двух передаваемых символов а; и а, поэтому npoz+» изводится полная компенсация сигналов собственного передатчика 1 независимо от параметров канала связи, а устройство адаптируется под параметры Z „ (t) . Естественно, что перед началом работы предлагаемое устройст5$ ние поступающего сигнала к удобному виду для дальнейшей обработки.

Сигнал с выхода входного согласующего блока 5 поступает одновременно на один из входов вычитателя 2 5 и на первый вход первого накопителя 6. Первый накопитель 6 производит запоминание входной информации, при этом его коммутатор 12 коммутирует поступающие сигналы на одну 1ð из линий 14 задержки в соответствии с величиной а„. Таким образом, если а„=О, то первый коммутатор 12 подключает выход входного согласующего блока 5 к входу одной линии 14 задержки, а второй коммутатор 13 подключает выход одной линии 14 задержки к входу вычитателя 2. Таким образом, в одной линии 14 задержки всегда будет .храниться образец передавае- 2О мого сигнала n (t), в другой линии 14 задержки — образец n„(t), в последующей линии 14 задержки — n<(t).

В случае передачи очередного символа а =0 сигнал собственного передатчи- ?5 ка 1 на первом входе вычитателя 2 равен

n;+„ (t) àîåt СИ (t-Е, )+ q, l . (2)

По сигналу и, =.0 подключается выход первой линии 14 задержки и на второй вход вычитателя 2 выводится содержимое одной линии 14 задержки, хранящееся до этого момента п,(t) =n, sLuo (t-t; )+ фД. (3) во необходимо обучить под параметры канала связи, которое заключается в том, что кодер 4 по сигналу от оконечного оборудования данных выдает поочередно символы а, а„, а и вводится по соответствующим сигналам а; в соответствующие линии 14 задержки.

Принимаемый сигнал в момент обучения должен отсутствовать, при этом линии 14 задержки накопителя 9 в момент обучения обнуляются. Обнуление перечисленных линий 14 задержки накопителя:производится с помощью ключа 8 путем передачи нуля на первый вход коммутатора 12 накопителя 9.

Работа предлагаемого устройства в случае присутствия принимаемого сигнала.

Пусть на противоположной стороне имеется аналогичный кодер 4 и передатчик 1, формирующий фазоманипулированный сигнал

1 (t) =Ч„со А> (t t; )+ (,+С -3 (4) где Ч - амплитуда передаваемого сигнала;

«(» — начальная фаза передатчика противоположной стороны;

Qzjeazj- сигнал на выходе кодера противопьложной стороны.

В общем случае a;(t) =С;(t+zt), . где h,Š— временной сдвиг между двумя последовательностями на выходе собственного кодера 4 и кодера противоположной стороны 0

Сигнал на выходе входного согпасующего блока 5 представляется суммой двух сигналов: передаваемого n;(t) и принимаемого S (t) поэтому

M„(t) Ä(t)+S,(t), (5) 1111259

Полдысыое роектыая, 4

ДНИЫПН За как описывалось выые, для компенсации сигналов собственного передатчика. необходимо as очередного значения Mg (t) вычесть предыдущее значение Mg(t). Тогда на выходе вычи-, 5 тателя 2 результирующее значение равно

Э (с) И1,,„. (е)-И;(с)=п1„, (t)+

+8;,» (t) „(t)-S; (t) = ()+8 (t)

„. () 8; (t) 8,„() S„(t) (6) 1о

Таким образом, в случае присутствия сигналов противоположной стороны на выходе вычитателя 2 имеем разность двух сигналов (очередного и предыдущего).

Как видно as формулы (6), для восстановления формы 8;,< {t) принимаемого сигнала на (Ьк.)-м интервале необходимо знать восстановленное

I ранее значение S (t). Восстановление 20 формы принимаемого сигнала и хране,ние результата:.предыдущего значения восстановленного сигнала производится в сумматоре 7, коммутаторах 12 и 13 и линиях 14 задержки накопите- 25 ля 9.

Действительно, на четвертом тактовом интервале (i=4) имеем

Dr+ (t) 8 (t) Sg (t) S@(t (7)

Величина S+(t) складывается с содержимым одной линии 14 накопителя 9.

Так как в момент обучения линии 14 задержки накопителя 9 были обнулены, I. (t)=S<(t)+0=8 (t) . (8)

Величина S„(t) фиксируется затем в одной линии 14 задержки накопителя 9 и используется в дальнейшем для восстановления принимаемого сигнала.

Действительно, в случае появления на выходе кодера 4 сигнала а =.О, имеем

M (t) „{t)+S (t);

D (t) nq (t)+S+(t) -8» (t) -n„(t) =

=8 (е.)-S (t); (9) э {") 8+ {") 8 е(")+8ч() н т.д. Таким образом, на выходе сумматора 7 имеем

7.;(с)=Д v, зЬ . (t-tt)+

+ » +C„- 2 ), (Io) т.е. полностью восстановленный принимаемый сигнал, в котором отсут— ствуют сигналы собственного передатчика 1. Приемник 3 демодулирует сигнал трехпозиционной фазовой модуляции в двоичные символы принимаемых данных и выдает их получателю 11 сообщения.

Таким образом, введение новых блоков позволяет повысить скорость передачи фазоманипулированных сигналов при дуплексной передаче данных.