Логический пробник

Иллюстрации

Показать всеРеферат

1. ЛОГИЧЕСКИЙ ПРОБНИК, содержащий эталонную микросхему, соединенную логическими выводами с первыми входами соответствующих элементов сравнения, соединенных вторыми входами с первыми клеммами для подключения контролируемой микросхемы, 1 ыходы элементов сравнения соединены с соответствующими входами элемента ИЛИ, соединенного выходом с первым входом первого RS-триггера, соединенного вторым входом через переключатель с второй клеммой для подключения контролируемой микросхемы и с первым выводом питания эталонной микросхемы, выходом - через индикатор с третьей клеммой для подключения контролируемой микросхемы и с вторым выводом питания эталонной микросхемы, отличающийся тем, что, с целью расширения функциональных возможностей пробника, в него введены анализаторы, вторые триггеры, элементы И, диоды, причем первые входы всех элементов И соединены с вторыми входами соответствующих элементов сравнения, выходы через соответствующие диоды - с первыми входами соответствующих элементов сравнения, с первыми входами соответствующих анализаторов, выходы которых соединены с первыми входами соответствующих вторых триггеров, вторые входы которых соединены с входной клеммой пробника, а выходы с вторыми входами соответствующих элементов И. 2. Логический пробник 1, отличающийся тем, что анализатор (Л содержит первый резистор, соединенС ный первым выводом с входом анализатора , вторым выводом - с первым выводом второго резистора, второй вывод которого соединен через третий резистор с общей шиной пробника, а непосредственно - с входом первого порогового элемента, соединенного выходом с первым входом элемента запрета, соединенного вторым входом через второй пороговый элемент с вторым выводом первого резистора, выход элемента запрета соединен с выходом анализатора.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (19) (11) (, ;1) G 01 R 31/28

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ ф(IP< (1Ц)Щ1 Л

ОПИСАНИЕ ИЗОБРЕТЕНИЯ 13

Н ABTOPCHOMY СВИДЕТЕЛЬСТВУ Б (21) 3605796/18-21 (22) 15.06.83 (46) 07.09.84. Бюл. ¹ 33 (72) 10.А. Джагаров,, О.С ° Манукян, Н.В. Масловский и Т.А. Хананашвили (53) 621.317.729(088.8) (56) 1 ° Авторское свидетельство СССР № 483633, кл. С 01 R 31/28, 1973 (прототип). (54)(57) 1. ЛОГИЧЕСКИЙ ПРОБНИК, содержащий эталонную микросхему, соединенную логическими выводами с первыми входами соответствующих элементов сравнения, соединенных вторыми входами с первыми клеммами для подключения контролируемой микросхемы, выходы элементов сравнения соединены с соответствующими входами элемента

ИЛИ, соединенного выходом с первым входом первого RS -триггера, соединенного вторым входом через переключатель с второй клеммой для подключения контролируемой микросхемы и с первым выводом питания эталонной микросхемы, выходом — через индикатор с третьей клеммой для подключения контролируемой микросхемы и с вторым выводом питания эталонной микросхемы, отличающийся тем, что, с целью расширения функциональных возможностей пробника, в него введены анализаторы, вторые триггеры, элементы И, диоды, причем первые входы всех элементов И соединены с вторыми входами соответствующих элементов сравнения, выходы через соответствующие диоды — с первыми входами соответствующих элементов сравнения, с первыми входами соответствующих анализаторов, выходы которых соединены с первыми входами соответствующих вторых триггеров, вторые входы которых соединены с входной клеммой пробника, а выходы— с вторыми входами соответствующих элементов И.

2. Логический пробник 1, о т л ич а ю шийся тем, что анализатор содержит первый резистор, соединенный первым выводом с входом анализатора, вторым выводом — с первым вы водом второго резистора, второй вывод которого соединен через третий резистор с общей шиной пробника, а непосредственно — с входом первого порогового элемента, соединенного выходом с первым входом элеманта запрета, соединенного вторым входом через второй пороговый элемент с вторым выводом первого резистора, выход элемента запрета соединен с выходом анализатора.

4 1112

Изобретение относится к контрольно-измерительной технике и может быть использовано при контроле микросхем.

Известен логический пробник, содержащий эталонную микросхему, соединенную логическими выводами с первыми входами соответствующих элементов сравнения, соединенных вторыми входами через первые клеммы 1О для подключения контролируемой микросхемы с соответствующими логическими выводами контролируемой микросхемы, выходы элемента сравнения соединены с соответствующими входами 15 элемента ИЛИ, соединенного выходом с первым входом перрого R5-òðèããåðà, соединенного вторым входом через переключатель с второй клеммой для подключения контролируемой микросхе- 20 мы и с первым выводом питания эталонной микросхемы, выходом — через ин-дикатор со второй шиной питания, с третьей клеммой для подключения контролируемой микросхемы и с вто- 25 рым выводом питания эталонной микросхемы (1) .

Недостатком известного устройства являются ограниченные функциональные возможности, обусловленные тем, что устройство не может автоматически определять по эталону принадлежность вывода микросхемы кд входу или выходу.

Цель изобретения — расширение 3$ функциональных возможностей логического пробника.

Поставленная цель достигается тем, что в логический пробник, содержащий эталонную микросхему, соединен- 4О ную логическими выводами с первыми входами соответствующих элементов сравнения, соединенных вторыми входами с первыми клеммами для подключения контролируемой микросхемы, вы- 4$ ходы элементов сравнения соединены с соответствующими входами элемента ИЛИ, соединенного выходом с первым входом первого15 -триггера, соединенного вторым входом через пере- $п ключатель с второй клеммой для подключения контролируемой микросхемы, и с первым выводом питания эталонной микросхемы, выходом — через индикатор с третьей клеммой для под- $$ ключения контролируемой микросхемы и с вторым выводом питания эталонной микросхемы, введены анализаторы, 327 2 вторые триггеры, элементы И, диоды, причем первые входы всех элементов И соединены с вторыми входами соответствующих элементов сравнения, выхо" ды через соответствующие диоды - с первыми входами соответствующих элементов сравнения, с первыми входами соответствующих анализаторов, выходы которых соединены с первыми входами соответствующих вторых триггеров, вторые входы которых соединены с входной клеммой пробки" ка, а выходы - со вторыми входами -соответствующих элементов И.

Кроме того, анализатор содержит первый резистор, соединенный первым выводом с входом анализатора, вторым выводом - с первым выводом второго резистора, второй вывод которого соединен через третий резистор с общей шиной пробника, а непосредственно— с входом первого порогового элемента, соединенного выходом с первым входом элемента запрета, соединенного вторым входом через второй пороговый элемент с вторым выводом первого резистора, выход элемента запрета соединен с выходом анализатора.

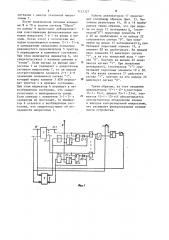

На фиг. 1 показана схема пробника; на фиг. 2 - схема анализатора.

Логический пробник для проверки микросхемы 1 содержит элементы 2-1"

2-п сравнения, элемент 3 ИЛИ, первый R5-триггер 4, переключатель 5, индикатор 6, эталонную микросхему 7, вторую клемму 8 для подключения контролируемой микросхемы, входную клемму 9, третью клемму 10 для подключения контролируемой микросхемы 1, первые клеммы 11-1-11- и для подключения контролируемой микросхемы 1, вход

12 анализатора, элементы 13-1 — 13-П.И, первый резистор 14, вторые триггеры 15-1 — 15-п, второй резистор 16, анализаторы 17-1 - 17-п, третий резистор 18, первый 19 и второй 20 пороговые элементы, элемент 21 запрета, выход 22 анализатора, диоды

23-1 — 23-п.Логические выводы эталонной микросхемы соединены со входами соответствующих элементов 2-1 — 2-h сравнения, соединенных вторыми входами через первые клеммы 11-1 — 11-и для подключения контролируемой микросхемы 1 с соответствующими логическими выводами контролируемой микросхемы 1. Выходы элементов сравнения 2-1 — 2-п. соединены с соответ1112327

55

3 ствующими входами элемента 3 ИЛИ, соединенного выходом с первым вхо.дом первого05-триггера 4, соединенного вторым входом через переключатель 5 с второй клеммой 8 для подключения контролируемой микросхемы 1, соединенной с первым выводом питания эталонной микросхемы 7, выходом — через индикатор б с третьей клеммой 10 для подключения контро- >0 лируемой микросхемы 1 и с вторым выводом питания эталонной микросхемы 7, Первые входы всех элементов

13-1 — 13-и И соединены со вторыми входами соответствующих элементов t5

2-1 - 2-о,сравнения, выходы через соответствующие диоды 23-1 — 23-и соединены с первыми входами соответст". вующих элементов 2-1 — 2- и сравнения, с первыми входами соответствующих 20 анализаторов 17-1 - 17-п, выходы которых соединены с первыми входами соответствующих вторых триггеров

15-1 — 15-п, вторые входы которых соединены с входной клеммой пробни- 25 ка, а выходы — со вторыми входами соответствующих элементов 13-1—

13"!! И.

В анализаторе первый резистор 14

,соединен первым выводом со входом З0

12 анализатора, вторым выводом — с первым выводом второго резистора

16, второй вывод которого соединен через третий резистор 18 с общей . шиной пробника, а непосредственно—

I со входом второго порогового элемента 20, соединенного вторым выходом с первым входом элемента 21 запрета, соединенного вторым входом через первый пороговый элемент 19 40 со вторым выводом первого резистора 14, выход элемента 21 запрета соединен с выходом 22 анализатора.

Логический пробник работает следующим образом. 45

В работе используется следующая особенность логических микросхем: при подаче на микросхему питания без подачи входных воздействий на ее выводах, являющихся входами, появляется потенциал ц, промежуточный м по величине между потенциалами логического нуля Оо и логической еди-, ницы О! . На вь.водах же, являющихся ее выходами, устанавливаются потекциалы, соответствующие логическому нулю или логической единице, т.е.00 или О, . При этом Uc a U c 0

Появление потенциала обусловлено индукционными процессами, полями статического заряда и паразитными связями внутреннего монтажа микросхемы, а ere величина для данной серии микросхем практически стабильна.

Устанавливается эталонная микросхема 7, идентичная контролируемой микросхеме 1. К вывоцам питания схемы 1 подключаются клеммы 8 и 10, На клемму 9 подается сигнал "Сброс ", устанавливающий триггеры 15-1 — 15-11 в нулевые состояния. Пусть, например, первый функциональный вывод микросхемы 7 является входом, Тогда ,потенциал Ц,возникающий на этом выводе, поступает на вход анализатора 17-1, на выходе которого в этом случае появляется сигнал "1", который переводит триггер 15-1 в единичное состояние. Сигнал "1" с прямого выхода триггера 15-1 будет постоянно действовать (до подачи сигнала

"Сброс" ) на вход элемента 13-1 И.

Тем самым открывается доступ логическому сигналу, действующему на первом выводе микросхемы 1 через клемму 11-1, элемент 13-1 И, диод

23-1 на соответствующий вход микросхемы 7. Таким образом, входной сигнал И, поступающий на вход микросхемы 1, поступит и на вход микросхемы 7. При этом изменение сигнала на выходе анализатора 17 не приводит к изменению состояния триггера 15 и, следовательно, не нарушает установившейся связи входов схем 7 и 1, На выходах же элемснта 2-1 сравнения сокр- няется сигнал "0".

Если же какой-либо вывод микросхемы является выходом, то происходит следующее. Пусть для определенности клемма 11,-и микросхемы 1 и аналогичный вывод микросхемы 7 являются выходом. В этом случае на этих выводах появляется потенциал Ио или И, На выходе анализатора 17-tt сохраняется сигнал "0". Поэтому триггер

15-!! также останется в нулевом состоянии. Элемент 13- tt H окажется закрытым. Поэтому сигналы, поступающие с выходов микросхем 1 и 7, поступают на разные входы элемента

2=й-сравнения, который производит их сравнение. Диоды 23-1 и 23- и в этом случае предохраняют входы элементов 13-1,13-й И от воздействия

1112327 сигналов с выхода эталонной микросхемы 7.

После подключения питания клеммами 8 и 10 и подачи сигнала "Сброс" на клемму 9 происходит автоматическая классификация функциональных выводов микросхем 7 и I на входы и выходы. После этого к логическим выводам подключаются клеммы 11-1 — 11-П и однократным замыканием нормально разомкнутого переключателя 5 триггер

4 переводится в единичное состояние.

При этом включается индикатор 6, что свидетельствует о наличии питания и

"земли". Если сигнал на выходе микросхемы 1 не совпадает с аналогичным сигналом микросхемы 7, то на выходе соответствующего элемента 2-1 — 2-tl сравнения появляется сигнал "1", который через элемент 3 ИЛИ переводит триггер 4 в нулевое состояние.

При этом индикатор 6 перейдет в невозбужденное состояние, что свидетельствует о неисправности схемы.

Если сигналы с элементов 2-1 — 2- п сравнения не поступают, то индикатор 6 остается в возбужденном состоянии, что свидетельствует об исправности микросхемы 1.

Работа анализаторов t7 происходит следующим образом (фиг. 2). Величины резисторов 14, 16 и 18 подбираются таким образом, что при подаче на вход 12 потенциала 0> (логический"0") пороговые элементы !9 и 20 не срабатывают и на выходе 22 сохраняется сигнал "0". При появлении на входе 12 потенциала0 0 сра" батывает пороговый элемент 19, а элемент .20 не срабатывает. На прямой вход элемента 21 действует сигнал

"1", а на его инверсный вход — сигнал "0". Поэтому на выходе 22 появляется сигнал "1". При появлении потенциала 0, (логическая "1") срабатывают пороговые элементы 19 и 20.

На оба входа элемента 21 действует сигнал "1", поэтому на его выходе 22

20 действует сигнал "0"

Таким образом, за счет введения анализаторов 17-1 — 17- п,триггеров

15-1 — 15-п, диодов 23-1 — 23-0, элементов 13-1 — 13- и И обеспечивается автоматическое обнаружение входов и выходов контролируемой микросхемы, что расширяет функциональные возможности устройства.

1112327

Составитель В. Дворкин

Редактор П. Коссей ТехредМ. Тепер Корректор А. Фоври

Заказ 6454/32 Тираа 710 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", r .. Ужгород, ул. Проектная, 4