Сигнатурный анализатор

Иллюстрации

Показать всеРеферат

СИГНАТУРНЬЙ АНАЛИЗАТОР, содержащий счетчик, счетный вход которого является входом синхронизации устройства, группу элементов И и первую группу триггеров, причем прямой выход каждого из п разрядов счетчика соединен с первымвходом соответствующего элемента И группы, выход каждого элемента И группы соединен со счетным входом соответствующего триггера первой группы, выходы которых образуют первую группу информационных выходов устройства, инверсный выход старшего разряда счетчика соединен с первым входом (п+1)-го элемента И группы, установочный вход устройства соединен с R-входом счетчика и входами синхронизации триггеров первой группы, первая группа входов сигнатур устройства соединена соответственно с информационными входами триггеров первой группы, отличающийся тем, что, с целью расширения его функциональных возможностей за счет контроля параллельных потоков данных, в него введены регистр, блок сравнения и вторая группа триггеров, причем первая группа информационных входов устройства соединена соответственно с первой группой входов блока сравнения , выход которого соединен с вторыми входами элементов И группы, группа входов вектора заданного вида устройства соединена соответственно с информационными входами регистра, выходы которого соединены, соответственно с второй группой входов блока сравнения, вторая группа входов сигнатур соединена соответственно с информационными входами триг-i геров второй группы, выходы которых образуют вторую группу информационных выходов устройства, установочный вход устройства соединен с входами синхронизации триггеров второй-, группы и регистра, первая группа информационных входов устройства соединена с соответствующими счетнь ми входами триггеров второй группы.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК

351> G 06 F 11/16

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

2,

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3535284/ 18-24 (22) 10. 01. 83 (46) 07.09.84. Бюл, М 33 (72) E.Ä. Баран, С.О. Веселовский и В.И, Рабинович (71) Новосибирский электротехнический институт (53) 681.3(088,8) (56) 1. Кирьянов К.Г. К теории сигнатурного анализа. — "Техника средств связи. Сер, Радиоизмерительная техника", M., 1980, вып. 2(27), с, 29-30.

2. Авторское свидетельство СССР

В 962962, кл. G 06 F 11/16, 1981 (прототип). (54)(57) СИГНАТУРНЫЙ АНАЛИЗАТОР, содержащий счетчик, счетный вход которого является входом синхронизации устройства, группу элементов И и первую группу триггеров, причем прямой выход каждого из и разрядов счетчика соединен с первым входом соответствующего элемента И группы, выход каждого элемента И группы соединен со счетным входом соответствующего триггера первой группы, выходы которых образуют первую группу информационных выходов устройства, инверсный выход старшего разряда счетчика соединен с первым входом (и+1)-го элемента И группы, установочный вход устройства соединен с R-входом счет-

„.SU 1112366 A чика и входами синхронизации триггеров первой группы, первая группа входов сигнатур устройства соединена соответственно с информационными входами триггеров первой группы, отличающийся тем, что, с целью расширения его функциональных возможностей за счет контроля параллельных потоков данных, в него введены регистр, блок сравнения и вторая группа триггеров, причем первая группа информационных входов устройства соединена соответственно с первой группой входов блока сравнения, выход которого соединен с вторыми входами элементов И группы, g группа входов вектора заданного вида устройства соединена соответственно с информационными входами регистра, выходы которого соединены соответственно с второй группой вхоФ дов блока сравнения, вторая группа входов сигнатур соединена соответственно с информационными входами триг» геров второй группы, выходы которых образуют вторую группу информацион, ных выходов устройства, установочный вход устройства соединен с входами синхронизации триггеров второй группы и регистра, первая группа информационных входов устройства соединена с соответствующими счетны- ми входами триггеров второй группы.

111236б дов 14.

Изобретение относится к контрольно-измерительной технике и может быть использовано при наладке, контроле и диагностике сложных цифровых устройств.

Известен сигнатурный анализатор, содержащий формирователь строба, первый и второй буферные регистры, регистр сдвига с обратными связями через сумматор по модулю два, дешифратор, блок памяти, генератор импульсов опроса, компаратор и блок индикации f1) .

Однако данное устройство не позволяет получать сигнатуры, указывающие, в каких разрядах входных двоичных векторов произошли ошибки, а также контролировать заданные векторы.

Наиболее близким по технической сущности к предлагаемому является сигнатурный анализатор, содержащий счетчик, счетный вход которого является синхронизационным входом устройства, группу элементов И и группу триггеров, причем первые входы всех элементов И группы объединены и являются первым информационным входом устройства, выход каждого элемента И группы соединен со счетным входом соответствующего триггера группы, выходы которых образуют группу информационных выходов устройства, единичный выход каждого разряда счетчика соединен с вторым входом соответствующего элемента И группы, нулевой выход старшего разряда счетчика соединен с вторым входом соответствующего элемента И группы, установочный вход устройства соединен с входом R счетчика и входами синхронизации всех триггеров группы, информационные входы устройства соединены с входами D соответствующих триггеров группы (21 .

Однако известное устройство предназначено лишь для контроля одномерных последовательностей и не может использоваться для контроля параллельных потоков данных.

Цель изобретения — расширение функциональных возможностей за счет контроля параллельных потоков данных.

Поставленная цель достигается тем, что в сигнатурный анализатор, содержащий счетчик, счетный вход ко- торого является, входом синхронизации устройства, группу элементов И и первую группу триггеров, причем прямой выход каждого из и разрядов счетчика соединен с первым входом соответствующего элемента И группы, 5 1выход каждого элемента И группы соединен со счетным входом соответствующего триггера первой группы, выходы которых образуют первую группу информационных выходов устройства, 1О инверсный выход старшего разряда счетчика соединен с первым входом (n+ 1)-го элемента И группы, установочный вход устройства соединен с

R-входом счетчика и входами синхронизации триггеров первой группы, первая группа входов сигнатур устройства соединена соответственно с информационными входами триггеров первой группы, введены регистр, блок срав20 нения и вторая группа триггеров, причем первая группа информационных входов устройства соединена соответственно с первой группой входов блока сравнения, выход которого соединен

25 с вторыми входами элементов И группы, группа входов вектора заданного вида устройства соединена соответственно с информационными входами регистра, выходы которого соединены соответственно с второй группой входов блока сравнения, вторая группа входов сигнатур соединена соответственно с информационными входами триггеров второй группы, выходы которых образуют втоРую группу инфоРмационных выходов устройства, установочный вход устройства соединен с входами синхронизации триггеров второй группы и регистра, первая группа информацион40 ных входов устройства соединена соответственно со счетными входами триггеров второй группы.

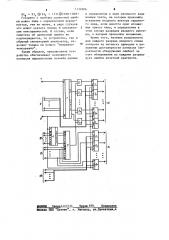

На чертеже представлена блок-схема устройства.

45 Устройство содержит и разрядный двоичный счетчик 1, группу из (и+ 1) элементов И 2, первую группу из (n+1) триггеров 3, r-разрядный регистр 4, блок 5 сравнения, вторую группу из

50 триггеров 6, вход 7 синхронизации устройства, установочных вход 8 устройства, первую группу входов 9 сигнатур, вторую группу входов 10 вектора задания вида, первую группу ин5 формационных Входов 11 ° вторую rpyn пу входов 12 сигнатур, первую группу информационных выходов 13 устрбйства и вторую группу информационных выхо.1 112

S1 =$2 =О, 0101

0111

Как правило, на практике и выбира ется равным r.

Устройство работает следующим образом.

Перед началом работы сигналом логической единицы на входе 8 устройства в триггеры 3 по входам 9 и в триггеры 6 по входам 12 записываются соответственно сигнатуры Sl и S2 контролируемой двоичной последователь- 10 ности Х без ошибок, а в регисгр 4 по входам 10 записывается вектор заданного вида и устанавливается в исходное (нулевое) состояние счетчик 1. !5

Затем на входы 11 устройства подается анализируемая векторная двоичная последовательность Z, а на вход, 7 — импульсы синхронизации.

Двоичный счетчик 1 осуществляет 20 счет синхроимпульсов двоичной последовательности, присваивая тем самым порядковый номер каждому вектору (входному слову) этой последовательности. В случае совпадения вектора 25 на входе 11 с заданным вектором сигнал логической единицы с выхода блока 5 сравнения открывает логические элементы И 2, разрешая прохождение кода, соответствующего порядковому номеру вектора на входе 11 в накапливающий сумматор по модулю два, выполненный на триггерах 3.

Таким образом, после прихода последнего синхроимпульса последователь35 ности векторов на вход 7 устройства в триггерах 3 (выходы 13 устройства) будет храниться результат суммирования по модулю два сигнатуры Sf последовательности без

40 ошибок Х и сигнатуры S анализируемой последовательности Z

$1х О+ представляющий собой сумму по модулю 45 два номеров тактов, на которых произошло искажение заданных векторов.

Одновременно в триггерах 6 сформируется и поступит на выход 14 сумма по модулю два сигнатуры S2> 50 последовательности беэ ошибок Х и сигнатуры $2 анализируемой последовательности Z

Збб 4

В случае, если делается вывод об отсутствии ошибок в векторной двоичной последовательности Z. Если хотя бы одна из сигнатур Sl и $2 не равна нулю, то делается вывод о наличии ошибок.

Предположим, что последовательность без ошибок содержит вектора, соответствующие заданному, на 5, 7 и 13 тактах т.е. на выходе блока 5 сравнения единица появится только на 5, 7 и 13 тактах, тогда $1

0101(з 0111 Q+) 1101 = 1111. Пусть ошибка произошла на 7 такте (искажен седьмой вектор), тогда на этом такте с выхода блока 5 сравнения на входы 12 элементов поступит 0 вместо

1 и Sl = 0101(+) 1101 = 1000 ° Sl

Ф

$1„(+) Sl = 1111Q+ 1000 = 0111.

В случае, если произошло искажение только одного вектора заданного вида, то на первой группе информационных выходов будет находиться двоичный код номера такта, на котором произошло искажение, Единицы на выходе соответствующих триггеров второй группы укажут на те разряды искаженного сло a, в которых произошли ошибки, Отметим, что при любом количестве (от 1 до r) ошибок в одном векторе местоположение вектора определяется однозначно. Если в анализируемой последовательности, поступающей от проверяемого устройства, заданный вектор не встретится, то это будет означать, что ошибки произошли на 5, 7 и 13 тактах, т.е. Sl =$1х .

Аналогично обнаруживается дойолнительное возникновение заданного вектора.

Пусть последовательность без ошибок содержала вектор заданного вида на 5, 7 и 13 тактах, тогда $1 =1111.

Пусть в анализируемой двоичной последовательности возник вектор заданI ного вида на третьем такте, тогда 81

110f

0011

1100

$2 =$2„(+) $2, представляющая собой сумму по модулю. два искаженных символов для каждого разряда входных векторов.

5 111236 я1„= s > „Q+ +s t = t i i Q+ +> < oo = oo > i

Говорить о наличии одиночной ошибки можно лишь с определенной вероятностью, тем не менее, в ряде случаев это может оказать помощь в локализа- 5ции неисправностей. В случае, если гипотеза об одиночной ошибке не подтверждается, то устройство, как и обычный сигнатурный анализатор, отвечает только на вопрос "исправнонеисправно".

Таким образом, предлагаемое устройство обеспечивает возможность контроля параллельных потоков данных ь и определения в виде двоичного кода номера такта, на котором произошло искажение входного вектора заданного вида, если имеется одно искажение такого типа, и определения в этом случае разрядов входного вектора, в которых произошло искажение.

Кроме того, наличие раздельного для каждого разряда входного слова контроля на четность приводит к повышению достоверности контроля (вероятности обнаружения ошибок) за счет обнаружения по каждому разряду всех ошибок нечетной кратности, ЦНПИ Зак з 54бО/34 Ts аж 698 По пксное

R и „2 Е

Филиал ППП Пвтект", r. Укгород, ул.Проектная,4