Устройство для обращения к блокам памяти

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ ОБРАЩЕНИЯ К БЛОКАМ ПАМЯТИ, содержащее регистр адреса, выходы которого подключены к входам дешифратора адреса, и переключатель , выполненный на трансформаторах, одни вторичные обмотки которых соединены по-; следовательно, первые выводы других вторичных обмоток подключены к шине нулевого потенциала, а вторые выводы являются выходами устройства, отличающееся тем, что, с целью упрощения и повышения надежности устройства, в него введены ограничительный элемент и формирователи сигналов, входы которых соедннены с выходами дешифратора адреса, а выходы подключены к выводам первичных обмоток соответствующих трансформаторов, один из выводов ограничительного элемента подключен к первому выводу одной из вторичных обмоток hepBoro трансформатора, другой вывод ограничительного элемента соединен с вторым уводом одной из вторичных обмоток послеД него трансформатора.

СОЮЗ СОВЕТСКИХ

ОРЗ

РЕСПУБЛИК

ОПИСАНИЕ ИЗОБРЕТЕНИф -:

К ABTOPCKOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

IlO ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЬГТ)Ф (21) 3511301/18-24 (22) 12.11.82 (46) 07.09.84. Бюл. № ЗЗ (72) Ю. С. Ермолин (53) 681.327(088.8) (56) 1. Крайзмер Л. П. Быстродействующие ферромагнитные запоминающие устройства, М.-Л., «Энергия», 1964, с. 19.

2. Авторское свидетельство СССР № 446104, кл. G 11 С 7/00, 1973 (прототип) . (54) (57) УСТРОЙСТВО ДЛЯ ОБРАЩЕНИЯ К БЛОКАМ ПАМЯТИ, содержащее регистр адреса, выходы которого подключены к входам дешифратора адреса, и переключатель, выполненный на трансформаторах, одни вторичные обмотки которых соединены по-, следовательно, первые выводы других вторичных обмоток подключены к шине нулевого потенциала, а вторые выводы являются выходами устройства, отличающееся тем, что, с целью упрощения и повышения надежности устройства, в него введены ограничительный элемент и формирователи сигналов, входы которых соединены с выходами дешифратора адреса, а выходы подключены к выводам первичных обмоток соответствующих трансформаторов, один из выводов ограничнтельного элемента подключен к первому выводу одной нз вторичных обмоток

hep8oro трансформатора, другой вывод ограничнтельиого элемента соединен с вторым (ыводом одной из вторичных обмоток послед-" него трансформатора.

l 112405

1О

Изобретение относится к вычислительной технике и может быть использовано при построении запоминающих устройств в качестве адресного блока.

Известно устройство для обращения к блокам памяти, предназначенное для опроса постоянных и односторонних запоминающих устройств и содержащее регистр адреса, выходы которого подключены к входам дешифратора адреса, соединенного с управляющими входами транзисторных ключей, причем через их выходные элементы шины опроса числового блока подключены к шине нулевого потенциала !1).

Однако это устройство содержит большое количество элементов и достаточно сложно, что приводит к увеличению габаритов и стоимости, а также к снижению надежности устройства.

Наиболее близким техническим решением к изобретению является устройство опроса постоянных и односторонних запоминающих устройств, содержащее регистр адреса, выходы которого подключены к входам дешифратора адреса, соединенного с управляющими входами транзисторных ключей, фор мирователь сигнала опроса и трансформаторы, одни из обмоток которых соединены последовательно и подключены к выходу формирователя сигнала опроса, вторые — к переходу коллектор-эмиттер соответствующе го транзисторного ключа, а третьи — к шине нулевого потенциала и соответствующей выходной шине устройства 12) .

Основным недостатком известного устройства является то, что из-за подключения обмоток трансформаторов к переходам коллектор-эмиттер транзисторов ключей они работают в пассивном режиме (не отдают мощность в нагрузку), что приводит к необходимости иметь формирователь опроса, а значит к увеличению габаритов и стоимости, а также снижению надежности устройства.

Мощность формирователя опроса, а также быстродействие и надежность устройства зависят от количества выходов устройства, что сужает область его использования.

Кроме того, известное устройство имеет помехи той же полярности, что и сигнал, на невыбранных выходах устройства, что также снижает быстродействие, надежность и устойчивость его работы.

Целью изобретения является упрощение устройства и повышение его надежности, быстродействия и устойчивости работы, а также устранение зависимости указанных характеристик от количества выходов устройстваа.

Поставленная цель достигается тем, что в устройство для обращения к блокам IIaмяти, содержащее регистр адреса, выходы которого подключены к входам дешифратора

34

50 адреса, и переключатель, выполненный на трансформаторах, одни из вторичных обмоток которых соединены последовательно, первые выводы других вторичных обмоток подключены к шине нулевого потенциала, а вторые выводы являются выходами устройства, введены ограничительный элемент и формирователи сигналов, входы которых соединены с выходами дешифратора адреса, а выходы подключены к выводам первичных обмоток соответствующих трансформаторов, один из выводов ограничительного элемента подключен к первому выводу одной из вторичных обмоток первого трансформатора, другой вывод ограничительного элемента соединен с вторым выводом одной из вторичных обмоток последнего трансформатора.

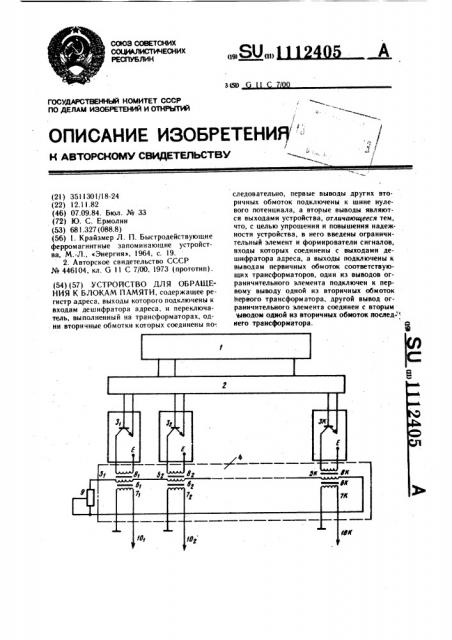

На чертеже изображена структурная схема предложенного устройства.

Устройство для обращения к блокам памяти содержит регистр 1 адреса, дешифратор 2 адреса, формирователи 3» — Зк сигналов (где к — число выходов устройства), переключатель 4, выполненный на трансформаторах 5» — 5„, имеющих обмотки 6» — бк, 7» — 7»» и 8» — 8„, а также ограничительный элемент, выполненный в виде переменного резистора 9. Устройство имеет выходы !0 ! Ок.

Устройство работает следующим образом.

В соответствии с кодом адреса, поступающим на регистр и дешифратор 2, запускаются все, кроме выбранного, формироватеJI II 3.

Предположим, что выбран формирователь 3, он не работает, а формирователи

3», 3,, 34 — 3x работают. При этом по обмоткам 8, 8>, 84 — 8к течет ток, который вызывает появление импульсов электродвижущей силы на обмотках 6», 6>, 64 — бк и 7, 7, 74 — ?к, так как обмотки 6 совместно с резистором 9 образуют замкнутую цепь, то по ней течет ток, который создает падение напряжения на обмотке б трансформатора 5 выбранного формирователя 3 . В результате по обмотке 7 этого выбранного трансформатора 5 течет ток, который в случае равенства сопротивлений нагрузки в обмотках ? в (к — 1) раз больше, чем ток в обмотке 7 остальных трансформаторов, и имеет противоположное направление.

Характеристики предлагаемого устройства не ухудшаются при увеличении количества выходов IO, так как мощность формирователей 3 определяется только величиной нагрузки в обмотке 7.

В предложенном устройстве помеха имеет направление, противоположное сигналу, что позволяет увеличить быстродействие и повысить надежность устройства.! 112405

Составитель В. Рудаков

Редактоо В. Данко Тевред И. Верес .. Корректор М. Демчик

Заказ бб68/36 Тираж 574 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий.

I I 3035, Москва. Ж вЂ” 35, Раушскан наб. ° д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектнаи, 4

Кроме того, с увеличением количества вы ходов устройства (при том же сопротивлении нагрузки) уменьшается мощность, отдаваемая в нагрузку работающими формиро вателямн (т. е. может, быть уменьшена их мощность), что также увеличивает быстродействие, повышает надежность устройства и, кроме того, упрощает его.