Многоканальное оперативное запоминающее устройство

Иллюстрации

Показать всеРеферат

I. /ПНОГОКАНЛЛЬНОЕ ОПЕРАТИВНОЕ ЗАПО/ЦИНАЮЩЕЕ УСТРОЙСТВО по авт. св. № 1088067, отличающееся тем, что, с целью повыи1ения надежности устройства, в него введены первый элемент ИЛИ и дополнительный логический блок, входы которого подключены к одноименным выходам блоков ввода информации, а выход соединен с одним из входов первого элемента ИЛИ, другой вход которого подключен к второму выходу логического блока, причем выходы дополнительного логического блока и первого элемента ИЛИ являются одними из выходов устройства. 2. Устройство но п. 1, отличающееся тем, что дополнительный логический блок содержит элементы И - ИЛИ и второй элемент ИЛИ, выход которого является выходом блока, а входы подключены к выходам элементов И-ИЛИ, входы которых попарно соединены между собой по принципу сочетаний «из К по два (где К - число каналов устройства) и являются входами блока. to . о О)

СОЮЗ COBETCHHX

СОЦ(ИАЛИСТИЧЕСН ИХ

РЕСПУБЛИК з юв G 11 С 1! 00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (61) 1088067 (21) 3559833/! 8- 24 (22) 02.03.83 (46) 07.09.84. Бюл. № 33 (72) B. С. Голоборц(енко (53) 681.327 (088.8) (56) 1. Авторское свидетельство СССP № 1088067, кл. G 1! С 11/00, 1982 (прототип). (54) (57) 1. МНОГОКАНАЛЬНОЕ ОПЕРА

ТИВНОЕ ЗАПОМИНАЮШЕЕ УСТРОЛСТВО по авт. св. № 1088067, отличающееся тем, что, с целью повышения надежности устройства, в него введень(первый элемент

ИЛИ и дополнительный логический блок, входы которого подключены к одноименным

„„SU„„11124Об А выходам блоков ввода информации, а выход соединен с одним нз входов первого элемента ИЛИ, другой вход которого подключен к второму выходу логического блока, причем выходы дополнительного логического блока н первого элемента ИЛИ являются одними нэ выходов устройства, 2. Устройство ((o п. !. отличающееся тем, что дополнительньlH логический блок содер ж ит элементы И вЂ” ИЛ И н второ и элемент ИЛИ, выход которого является выходом блока, а входы подключены к выходам элементов И вЂ” ИЛИ, входы которых попарно соединены между собой по принципу сочетаний «нз К по два» (где К вЂ” число каналов устройства) н являются входами блока.

ll

Изобретение относится к вычислительной технике и предназначено для использования в многопроцессорных и многомашинных вычислительных системах в качестве общей оперативной памяти.

По основному авт. св. № 1088067 извест но многоканальное оперативное запоминающее устройство, содержащее накопитель, формирователи адресных токов, усилители считывания, формирователи информационных сигналов, группы элементов ИЛИ, входной и выходной каналы, распределитель сигналов выходных каналов, селекторы блока ввода данных и логический блок, один из выходов которого является выходом устройства, выходы элементов ИЛИ групп подключены к входам соответствующих формирователей адресных токов, выходы которых подключены к адресным входам накопителя, выходы распределителя сигналов выходных каналов соединены с входами формирователей информационных сигналов, выходы которых подключены к информационным входам накопителя, выходы которого соединены с входами усилителей считывания, первый входной канал содержит первый и второй регистры адреса, первый и второй дешифраторы адреса, выходы которых являются первым и вторым выходами входного канала, и рас-. пределитель сигналов, причем выходы первого и второго регистров адреса подключены к входам распределителя сигналов, первые и вторые выходы входных каналов— к одним из входов элементов ИЛИ групп, первые входы выходных каналов — к выходам усилителей считывания, вторые входы второго и последующих выходных каналов к третьим выходам соответствующих входных каналов, первые выходы выходных каналов — к входам распределителя сигналов выходных каналов, причем первый входной канал содержит три группы элементов И, а выходы первого и второго регистров адреса подключены к первым входам элементов И первой и второй групп, выходы которых соединены с входами первого н второго дешифраторов адреса, выходы распределителя сигналов являются четвертым выходом данного канала и подключены к первым входам элементов И третьей группы, выходы которых являются третьим выходом первого входного канала и подключены к второму входу первого выходного канал а, вторые входы элементов И подключены к третьему входу первого входного канала, третьи входы и четвертые выходы входных каналов — — к первым выходам и первым входам селекторов, вторые выходы селекторов — к входам логического блока, другие выходы которо.го подключены к вторым входам селекторов, третьи входы селекторов — - к выходам соответствующих блоков ввода данных (i j .

Недостатком известного устройства является невысокая точность контроля его при! 2406

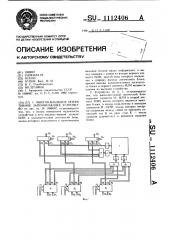

На фиг. 1 и 2 изображена структурная схема устройства; на фнг. 3 — электрическая схема дополнительного логического блока; на фиг. 4 — структурная схема входного канала; на фиг. 5 — структурная схема выходного канала; на фиг. 6 — функциональная схема логического блока; на фиг. 7— электрическая схема селектора; на фиг. 8— электрическая схема блока ввода информации.

Многоканальное оперативное запоминающее устройство (фиг. н 2) содержит накопитель l, формирователи 2 и 2> адресных токов, усилители 3 считывания, формирователи 4 информационных сигналов группы 5, < 5 элементов ИЛИ, входные каналы 6i — 6ф выходные каналы 7, — 7„, распределитель 8

55 оритетов каналов, что снижает надежность устройства. Это обусловлено тем, что контролируются конфликтные обращения. устройств-потребителей (процессоров) н не контролируется правильность установки приоритетов его каналов, в результате чего могут возникать неопределенные ситуации и сбои.

Так при несовпадении кодов адресов на входах устройства и/или при несовпадении кодов на выходах распределителей сигналов

>0 в устройстве не обнаруживается неправильная установка приоритетов каналов. Следует отметить, что в данном случае это и не влияет на работоспособность устройства. Однако при появлении уровня логической единицы на выходе логического блока неясно, возник ли этот уровень только из-за конфликтного обращения процессоров, что не влияет на дальнейшее продолжение работы устройства, или из-за конфликтного обращения процессоров и неправильной установки при20 оритета, что приводит к сбою и требует вмешательства оператора в работу устройства.

Целью изобретения является повышение надежности устройства.

Поставленная цель достигается тем, что в многоканальное оперативное запоминающее устройство введены первый элемент

ИЛИ и дополнительный логический блок, входы которого подключены к одноименным выходам блоков ввода информации, а выход соединен с одним из входов первого элемента ИЛИ, другой вход которого подключен к второму выходу логического блока, причем выходы дополнительного логического блока и первого элемента ИЛИ являются одними из выходов устройства.

При этом дополнительный логический

35 блок содержит элементы И вЂ” ИЛИ и вто-, рой элемент ИЛИ, выход которого является выходом блока, а входы подключены к выходам элементов И вЂ” ИЛИ, входы которых попарно соединены между собой по принципу

40 сочетаний «из К по два» (где К вЂ” число каналов устройства) и являются входами блока.

1112406 сигналов выходных каналов, логический блок 9, селекторы 10< — 10», блоки 11i—

I I«ввода информации, резистор 12, дополнительный логический блок 13 и первый элемент ИЛИ 14, Входные каналы бс — 6» имеют первые 15 — 15«, вторые l6 — 16» и третьи 17r — 17„входы, первые ISi — 18«, вторые

I9< — 19„, третьи 20 — 20« и четвертые 21>—

21и выходы. Выходные каналы 7> — 7« имеют первые 22с — 22x вторые 23с — 23« и третьи 24с — 24« входы и первые 25с — 25«и вторые 26> — 26«выходы. Логический блок 9 имеет входы 27 — 27»,è первые 28> — 28»- и второй 29 выходы. Селекторы IOi — 10» имеют первые 30> — 30» и вторые 31> — 31«и первые 32, вторые 33> — 33„и третьи 34i—

34«входы. Блоки 11> — 11«ввода информации имеют выходы 35 — 35». Блок 13 имеет входы 36 — 36«выходы и выход 37. Выход

38 элемента ИЛИ 14 является одним из выходов устройства. Другим выходом устройства является выход 37 дополнительного логического блока 13. Дополнительный логический блок 13 (фиг. 3) содержит элементы

И вЂ” ИЛИ 39 — 39«и второй элемент ИЛИ

40. Выходы 41 с — 41» элементов И вЂ” ИЛИ

39r — 39«подключены к входам второго элемента ИЛИ 40.

Входной канал 6 (фиг. 4) содержит первый 42с и второй 42с регистры адреса, первый 43r и второй 43с дещифраторы адреса, распределитель 44 сигналов и три группы элементов И 45 †4. Выходной канал 7 (фиг. 5) содержит коммутатор 46, регистр

47 слова и распределитель 48 сигналов канала. Логический блок 9 (фиг. 6) содержит элементы И 49, блоки 50m — 50у,, 50п, 50сс и 50с сравнения и элемент ИЛИ 51. Индексы в обозначении блоков сравнения указывают на сочетания номеров их входов. Например, блок 50» сравнения имеет сочетание на входе из входов 27с и 27э. Селектор

10 (фиг. 7) содержит элементы И 52 и элемент И вЂ” ИЛИ 53. Блок 11 ввода информации (фиг. 8) содержит к-модульный переключатель 54 с зависимой фиксацией и общей кнопкой сброса и резисторы 55> — 55„ и 56.

П редл агаемое устройство работает во многом аналогично известному устройству.

В нем аналогична установка приоритетов каналов, а также полностью совпадают свойстваа раси редел и теле и 44. Поэтому ра бота устройства описывается в двух случаях, охватывающих все интересукгшие нас события: во-первых, несовпадение кодов на выходах распределителей 44 — 44„входных каналов 6r — 6„, как следствие, при несовпадении кодов адресов, поступающих на входы. 15 — 15„и lái — lб„устройства; во-вторых, совпадение кодов адресов каналов или совпадение кодов на выходах распределителей 44i — 44» при несовпадении кодов адресов каналов на входах 15r — 15«и 16: — 16» устройства.

На входы 15 — 15к и Iár — 16« каналов подаются адреса слов, подлежащих произвольной или одновременной обработке (считыванию и/или записи) и максимальное число которых при одновременной обработке равно к-числу входных или выходных каналов устройства.

При несовпадении кодов на выходах рас10 пределителей 44с — 44«и, как следствие, при несовпадении кодов адресов, поступа ющих на входные каналы 6l — 6» устройства (первый случай), входные 6> — 6» и выходные

7l — 7« ка нал ы устройства пол иост ью нез а15 внсимы и позволяют обеспечить одновременно считывание и/или запись до к слов. Поскольку указанные коды не совйадают, то на инверсных выходах всех блоков 50 сравнения (фиг. 6) будут уровни логической едини цы, которые, пройдя элементы И 49 и се20 лекторы 10 — 10„(фиг. 7), поступают на входы элементов И 45, — 45«входных, каналов

6l — б «в качестве разрешающих уровней.

Подробно рассмотрим прохождение сигналов через первые входно" ál и выходной

7 каналы устройства, поскольку прохождение сигналов через все остальные входные и выходные каналы аналогично прохождению через первые.

При поступлении кода адреса на входы

15 и l6> первого входного канала 6 с выхода регистров 42 и 42с (фиг. 4) коды адреса поступают непосредственно на входы распределителя 44 и дешифраторов 43с и

43с адреса через предварительно открытые элементы И 45 н 45с. С выходов дешифра35 торов 43> и 43с адреса через элементы ИЛИ

5> н 5, (фиг. I) сигналы поступают на входы формирователей 2 и 2с. В результате на соответствующих входах накопителя 1 будут выбраны запоминающие элементы, и

40 на входы усилителей 3 поступает первое считанное слово. Распределитель 441 в соответствии с содержимым регистров 42s и 42с подключает усилители 3 через коммутатор

46 к регистру 47r первого выходного канала 7 (фиг. 5). Таким образом, считанное

45 первое слово из накопителя 1 поступает иа информационный выход 26l устройства. Аналогично работают все остальные каналы.

При этом на выходе 29 блока 9 и на выходах

37 и 38 устройства присутствуют уровни логического нуля, свидетельствующие об от50 сутствии сбоев в устр йстве. На выходе 29 блока 9 и на выходе 37 блока 13 будут уровни логического нуля вследствие того, что на все входы 27с — 27„блока 9 и Збс — 36» блока !3 будут поданы несовпадающие коды.

55 Поскольку выходы 29 и 37 блоков 9 и 13 являются одновременно и входами элемен. та ИЛИ 14, то и на выходе 38 этого элемен та будет уровень логического нуля, свиде

Ц 12406 тельствующий об отсутствии сбоев в устрой-. стве.

Прежде чем описывать дальнейшую работу устройства, поясним установку приори тетов каналов.

Установка приоритетов каналов осуществляется, исходя из следующих соображений:

1. Младшему номеру модуля переключателя 54 блока 11 (на фиг. 8 крайний левый) соответствует наивысший приоритет и нарборот. l9

2. Включением требуемого модуля переключателя 54 осуществляется установка при оритета соответствующего канала.

3. Во всех каналах устройства должны быть установлены различные (несовпадающие) приоритеты. Установка одного и того же приоритета хотя бы в двух каналах недопустима, так как в случае совпадения кодов на выходах распределителей 44 данных входных каналов возникает сбой в устройстве. 20

4. Селекторы 10 — 10» под управлением блоков 111 — 11» обеспечивают требуемую перекоммутацию выходов распределителей

44 — 44к входных каналов 6 — 6» на входы

27 — 27 < блока 9 и, следовательно, на входы блоков 50 г, 50m — 50д,к сравнения (для четырехканального устройства — 50<>, 50, 50з ) .

5. При поступлении на входы 27, — 27» блока 9 совпадающих кодов вследствие совкоторый связан с источником питания Engr. g5 через резистор 12.

Прн частичном совпадении кодов адреса н/нли кодов на выходах распределителей 44 падения кодов адреса на входах 15> — 15» и 16 — !бк и/или на выходах распределителей 44> — 44» входных каналов 61 — 6» на выходах 28> — 28»-1 блока 9 появляется к — 1 запрещающих уровней логического нуля.

6. В соответствии с установленной коммутацией входов 271 — 27» к — 1 запрещающих уровней логического нуля с выходов

28> — 28» > блока 9 поступают через селекторы 101 — 10» в соответствующие входные каналы 61 — бк..Тем самым обеспечивается блокировка к — 1 нэ к каналов устройства. При этом единственным незаблокированным каналом будет канал с наивысшим приоритетом. Разрешающий уровень логической единицы для него передается от источника питания Епщ-через резистор 12 (фиг. 2) и элемент И вЂ” ИЛИ 53 (фиг. 7) соответствующего селектора 10.

При полном совпадении кодов адресов, поступающих на входы 15> — !5» и 16> — 1бк и/илн при полном совпадении кодов на выходах распределителей 44 †» всех входных каналов б! — бк только один вполне определенный входной и ему соответствующий выходкой канал будут открыты. Все остальные каналы будут заблокированы. При этом, как было показано, открытым каналом будет тот, 30

50 некоторых входных каналов все остальные каналы открыты и работают независимо друг от друга. Те каналы, в которых произошло совпадение указанных кодов, блокируются за исключением одного — канала с наибольшим приоритетом. При этом на выходе 29 блока 9 появляется уровень логической единицы, свидетельствующий о произошедшем совпадении кодов в устройстве.

Как было указано, при несовпадении кодов иа выходах распределителей 44 †„ и, как следствие, при несовпадении кодов адресов, поступающих на входные каналы 6 — б к (первый случай) входные 6,— 6 н выходные 7 — 7» каналы устройства полностью независимы, и блок 13 и элемент ИЛИ 14 не оказывают никакого влияния на работу устройства.

Блок 13 и элемент ИЛИ 14 с соответствующими связями оказывают влияние на работоспособность устройства только в случае, когда происходит совпадение кодов (полное или частичное), и обеспечивают выявление и локализацию неправильно установленных приоритетов каналов устройства.

Так, если в двух или нескольких каналах неправильно установлены приоритеты, например включены одноименные модули переключателей 54 в соответствующих блоках 11 (например, модули 351 в первом 1li и второом 1 блоках), то один и тот >ке приоритет принадлежит одновременно двум или нескольким каналам (в приведенном примере одинаковый приоритет принадлежит первому 61 и второму 6z каналам). Поэтому при конфликтном (одновременном) обращении процессоров.в эти каналы, т. е. по адресам, коды которых совпадают на выходах распределителей 44 данных каналов, требуемой блокировки каналов не происходит, хотя на выходе 29 блока 9 появляется уровень логической единицы, свидетельствующий о произошедшем в устройстве совпадения кодов: Отсутствие требуемой блокировки каналов приводит к сбою, поскольку все каналы с одинаковым приоритетом остаются разблокированными (в данном примере раэблоки рованными оказываются каналы 6> н 6 ), и поэтому два нли несколько процессоров обращаются по одним и тем же адресам или по адресам, коды которых отличаются перестановкой своих половин (например, коды

0l 1 O1 l 0 и 11100110). Это недопустимо и выявляется блоком 13. Уровни равных приоритетов с выходов блоков 11 (в нашем примере уровни логической единицы с выходов

35 . блоков 111 и 1 lz) подаются на входы

36> — 36» блока 13 (на входы 36> соответственно). В результате на одном нз выходов

41i — 41„элементов И вЂ” ИЛИ 391 — 39„появляется уровень логической единицы (в данном примере на выходе 41 элемента И—

ИЛИ 39> }. Пройдя элемент ИЛИ 40, уро1112406 вень логической единицы появляется на выходе 37 блока 13 и сигнализирует о сбое в устройстве.

Если включены другие одноименные модули переключателей 54 различных блоков

11, то на выходе другого, вполне определенного элемента И вЂ И блока 13 появляется уровень логической единицы, сигнализирующий о сбое в устройстве.

Таким образом, отсутствие уровней логической единицы на выходе 29 блока 9, на выходе 37 блока 13 и на выходе 38 элемента ИЛИ 14 свидетельствует об отсутствии сбоев и совпадений кодов адресов при обращении к устройству. В этом случае все ка- 15 налы устройства работают независимо, обеспечивая произвольную или одновременную обработку информации по к каналам. При наличии уровня логической единицы на выходе 29 блока 9 и, следовательно, на выходе

38 элемента ИЛИ 14 и при отсутствии уров,ня логической единицы на выходе 37 блока

l3 н устройстве имеет место конфликтное обращение процессоров. Приоритет отдается процессору, подключенному к каналу с наивысшим приоритетом. Остальные процессоры временно блокируются, рабо а устройства продолжается. При наличии уровня логической единицы на выходе 37 блока 13 и. следовательно, на выходе 38 элемента ИЛИ

l4 в устройстве имеет место неправчльная установка приоритета каналов, что при конфликтном обращении процессоров может привести к сбою. В этом случае требуется вмешательство оператора в работу устройства.

Технико-эконом ическим преимуществом предложенного устройства по сравнению с известным является способность локализовать неправильно установленные приоритеты и сообщить об этом в систему и или оператору с помощью уровней логической единицы. В конечном итоге это повышает степень автономного и системного контроля и упрощает поиск неисправностей.

1!!2406!

112406

I!! 2406

Фиг. 8

Составитель В. Рудаков

Редактор В. Данко Техред И. Верес - . Корректор О. Тигор

Заказ 6068/36 Тираж 574 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий ! 13035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4