Запоминающее устройство

Иллюстрации

Показать всеРеферат

ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО , содержащее дешифратор адреса слова , выходы которого соединены с числовыми шинами матрицы основных и резервных элементов памяти, разрядные шины которой подключены к одним из входов основных и резервных усилителей соответственно, одни из управляюших входов которых соединены с выходом формирователя управляющих сигналов, а выходы подключены к входам выходного блока, матрицу программируемых элементов памяти, одни из входов которой соединены с выходами регистра адреса разряда и входами деижфратора адреса разряда, а другие входы объединены с входами регистра адреса разряда и являются одними из адресных входов устройства, информационными входами которого являются одни из входов формирователя управляющих сигналов, другие входы которого и управляющие входы выходного блока являются одними из управляющих входов устройства , другими управляющими входами которого являются управляющие входы матрицы программируемых элементов памяти, выходом устройства является выход выходного блока, отличающееся тем, что, с целью повышения быстродействия устройства, в него введены источник опорного напряжения, и две группы формирователей сигналов, причем входы одних из формирователей сигнаi лов подключены к выходам дешифратора адреса разряда, а выходы - к другим управ (Л ляющим входам основных усилителей, входы других формирователей сигналов соединены , с выходами матрицы программируемых элемеитов памяти, а выходы - с другими управляющими входами резервных усилителей , выходы источника опорного напряжения подключены к другим входам основных и резервных усилителей. to ;ib

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„SU„„1112412 з1 ц G 1! С 29/00,t

ОПИСАНИЕ ИЗОБРЕТЕНИЯ /

К ABTOPGHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3600091/18-24 (22) 02.06.83 (46) 07.09.84. Бюл. № 33 (72) Е, А. Верниковский, Э. П. Калошкин, В. К. Конопелько, В. В. Лосев, А. К. Панфиленко, А. И. Сухопаров, П. П. Урбанович и В. lO. фомин (53) 681.327 (088.8) (56) 1. Авторское свидетельство СССР № 877614, кл. G 11 С I I/00, 1980.

2. Авторское свидетельство СССР

¹ 980165, кл. G 11 С Il 00, !981 (прототип) . (54) (57) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО, содержащее дешифратор адреса слова, выходы которого соединены с числовыми шинами матрицы основных и резервных элементов памяти, разрядные шины которой подключены к одним из входов основных и резервных усилителей соответственно, одни из управляющих входов которых соединены с выходом формирователя управляющих сигналов, а выходы подключены к входам выходного блока, матрицу программируемых элементов памяти, одни из входов которой соединены с выходами регистра адреса разряда и входами дешифратора адреса разряда, а другие входы объединены с входами регистра адреса разряда и являются одними иэ адресных входов устройства, информационными входами которого являются одни иэ входов формирователя управляющих сигналов, другие входы которого и управляющие входы выходного блока являются одними из управляющих входов устройства, другими управляющими входями которого являются управляющие входы матрицы программируемых элементов памяти, выходом устройства является выход выходного блока, отличающееся тем, что, с целью повышения быстродействия устройства, в него введены источник опорного напряжения, и две группы формирователей сигналов, причем входы одних нз формирователей сигналов подключены к выходам дешнфратора an- @ реса разряда, а выходы — к другим управляющим входам основных усилителей, входы других формирователей сигналов соединены. с выходами матрицы программируе- Ъ .. ых элементов памяти, а выходы - — с другими управляющими входами резервных усилителей, выходы источника опорного напря- р жения подключены к другим входам основных и резервных усилителей.

1112412

t5

Изобретение относится к вычислительной технике и может быть использовано при изготовлении больших интегральных схем запоминающих устройств с произвольной выборкой информации, имеющих большую площадь кристаллов, где требуется увеличить выход правильно функционирующих изделий с высоким быстродействием.

Известно запоминающее устройство, содержащее матрицу элементов памяти (ЭП), схемы логики обрамления и схемы коррекции, позволяющие исправлять ошибки, вызванные дефектами ЭП, которые расположены в нескольких разрядах матрицы ЭП при наличии такого же числа дополнительных разрядов в матрице !!).

Недостатком этого устройства является низкое быстродействие.

Наиболее близким техническим решением к изобретению является запоминающее устройство, содержащее дешифратор адреса слова, соединенный с числовыми адресными шинами матрицы основных и резервных ЭП разрядные шины которых соединены соответственно с основными и резервными усилителями записи считывания (УЗС), первые управляющие входы которых связаны с выходом схемы управления записью считывани.ем, входами подключенной к шинам выборки кристалла, разрешения записи н входной информации, входы дешифратора адреса разряда соединены с первыми входами матрицы программируемых элементов И, и выходами буферных схем, выходы которых соединены с вторыми входами матрицы программируемых элементов И, третьи входы которой под ключаются к управляющим входам програм мирования, информационный выход основных и резервных УЗС соединен с входом выходного блока, управляющие входы которого подключены к шинам выборки кристалла и разрешения записи, выход выходного блока является выходом устройства (2I.

Недостатками известного устройства являются низкое быстродействие из-за задержек сигналов коррекции в целях запрета обращения к дефектному ЭП основной матрицы, а также сложность устройства.

Целью изобретения является повышение быстродействия устройства.

Поставленная цель достигается тем, что в запоминающее устроиство, содержащее дешифратор адреса слова, выходы которого соединены с числовыми шинами матрицы основных и резервных ЭП, разрядные шины которей подключены к одним из входов основных и резервных усилителей соответственно, одни из управляющих входов которых соединены с выходом формирователя управляющих сигналов, а выходы подключены к входам выходного блока, матрицу программируемых ЭП, одни из входов которой соединены с выходами регистра адреса разряда и входами дешифратора адреса разряда, а другие входы объединены с входами

Регистра адреса разряда и являются одними из адресных входов устройства, информационными входами которого являются одни из входов формирователя управляющих сигналов, другие входы которого и управляющие входы выходного блока являются одними из управляющих входов устройства, другими управляющими входами которого являются управляющие входы матрицы программируемых ЭП выходом устройства выход выходного блока, введены источник опорного напряжения и две группы формирователей сигналов, причем входы одних из формирователей сигналов подключены к выхода м дешифратора адреса разряда, и выходы — к другим управляющим входам основных усилителей, входы других формирователей сигналов соединены с выходами матрицы программируемых ЭП, а выходы— с другими управляющими входами резервных усилителей, выходы источника опорного напряжения подключены к другим входам основных и резервных усилителей.

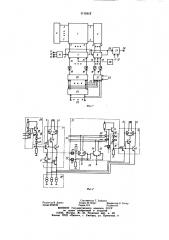

На фиг. изображена функциональная схема предложенного устройства; на фиг. 2— принципиальные схемы наиболее предпочтительных вариантов выполнения усилителей,. формирователей сигналов, матрицы программируемых ЭП н формирователей сигналов.

Предложенное устройство содержит матрицы 1 и 2 основных н резервных ЭП соответственно с числовыми шинами 3, дешифратор 4 адреса олова, разрядные шины 5 и 6 матриц 1 и 2 соответственно, основные 7 и резервные 8 усилители с одними из управляющих входов 9, формирователь !О управляющих сигналов с входами 11 — 13, другие управляющие входы 14 и 15 соответственно усилителей ? и 8.

Устройство содержйт также формирователи 16 и 17 сигналов с входами 18 и 19 соответственно, дешифратор 20 адреса разряда, матрицу 2! программируемых ЭП с управляющими входами 22 и одними из входов 23, регистр 24 адреса разряда с входа- ми 25, источник 26 опорного напряжения и выходной блок 27 с входами 28 н выходом

29. Матрица 21 программируемых ЭП содержит (фиг. 2) плавкие перемычки 30, контактные площадки 3! — 33 запоминающие транзисторы 34 — 37. Формирователь 10 управляющих сигналов содержит управляющие транзисторы 38 и 39, формирователи

16 сигналов — диоды 40 — 42, формирователи 17 сигналов — диоды 43 и 44, усилители 7 и 8 — усилительные транзисторы 45 и 46 соответственно.

Предложенное устройство работает следующим образом.

После изготовления кристалла запоми-нающего устройства (ЗУ) осуществляется его контроль с целью выявления местоположения дефектных ЗП матрицы l. При

1!124!2 установлении адреса дефектного ЭП этот адрес заносится в матрицу 21 посредством пережигания соответствующих плавких свя. зей, т.е. вместо имеющего дефекты ЭП раз ряда матрицы 1 подключаются ЭП матрицы 2. Если этот разряд матрицы 2 содержит дефектные ЭП, то он не используется.

Рассмотрим в качестве примера процесс пережигания плавкой перемычки (фиг. 2) .

Ее пережигание и настройка запоминаю5

1О щего элемента матрицы 21 (транзистор 36), так же как и других запоминающих элементов того же разряда матрицы 21, осуществляется путем подачи соответствующих напряжений на контактные площадки 33 и кода адреса дефектного разряда на входы 25 матрицы 21. Для пережигания перемычки 30 на вход 23 подается низкий уровень потенциала, соответствующий логическому нулю, на площадку 33 — высокий уровень напряжения, достаточный для пережигания перемычки 30. На плошадку 31 подается уровень напряжения, достаточный для отпирания соответствующего транзистора 34 и пережигания перемычки. Уровни напряжения и тока определяются конструкторско-технологически ми особенностями уст- 25 ройства. После пережигания перемычек 30 соответствующий дополнительный разряд матрицы 2 выполняет функции дефектного разряда матрицы 1. Напряжения на контактные площадки 31 — 33 подаются íà sxoды 22. 30

В рабочем режиме (записи или считывания) на площадки 33 внешние сигналы не подаются, и транзисторы 34 и 35 не влияют на работу устройства, так как они отключены от входов 25.

При эксплуатации устройства в режиме записи информации на входы ll — 13 подаются логические сигналы выборки кристалла, разрешения записи и информации соответственно, а на адресные входы — адрес опрашиваемого ЭП. При этом происходит 40 возбуждение выходов дешифраторов 4 и 20 в соответствии с кодом адреса опрашиваемого ЭП. Возбужденная шина 3 дешифратора 4 подключает ЭП матрицы 1 выбранного слова к шинам 5 и в исправный ЭП матри- цы 1, выбираемый сигналом одного из вхо- 45 дов 18 дешифратора 20, происходит запись информации, поступающей по входу 13.

При поступлении адреса дефектного разряда возбуждается один из выходов 18 дешифратора 20 и олин из выходов 19 матрицы 2!. Сигналы с выходов 18 и 19 поступают на соответствующие формирователи 16 и 17.

Однако, поскольку на выходах формирователей 16 и 17 формируется разныи уровень напряжения — на выходе 15 уровень напряжения выше, чем на выходе 14, то включается один из усилителей 8, так как идентичные транзисторы 45 и 46 усилителей ? и 8 образуют токовый ключ с источником 26 в цепи эмиттеров (фиг. 2), и транзистор 46 соответствующего усилителя 8 подключает ток источника 26 к одной из шин 6 в зависимости от записываемой информации, отключив тем самым транзистор 45 соответствующего усилителя 7. Управление источником 26 основано на эффекте перехвата тока тем из транзисторов 45 и 46, на базу которого поступает более высокий уровень напря жения.

При отсутствии дефектных ЭП в опрашиваемом разряде матрицы 1 на выходах 15 формирователей 17 находится низкий уровень сигнала, это обеспечивает подключение источника 26 к шине 5. Режим считывания задается формирователем 10. Сигнал о состоянии опрашиваемого ЭП исправного разряда матрицы 1 поступает с выхода 28 усилителей 7 на выход 29 устройства через блок 27. Если опрашивается дефектный разряд матрицы 1, то происходит обращение к соответствующему ЭГ1 матрицы 2, в которь|й и записывалась считываемая информация.

Обращение к ЭП матрицы 2 обеспечивается теми же условиями, которые разрешили обращение к нему в режиме записи. Усилители 7 и 8 работают в режимах записи и считывания, однако в режиме записи считанная с шин 5 и 6 информация не проходит на выход 29 устройства, так как блок 27 стребируется сигналами на входах 11 и 12. Управление источником 26 осуществляется через усилители 7 и 8 путем подачи сигналов с входов ll — 13.

Таким образом, предлагаемое устройство, как и известное, позволяет производить коррекцию дефектных ЭП в матрицах 1 и 2 при наличии резервных ЭП матрицы 2, но с более высоким быстродействием. Быстродействие предлагаемого устройства выше за счет исключения задержки сигнала, запрещающего обращение к дефектному 3ll путем блокировки соответствующего усилителя, что привело также к упрощению устройства.

lll24l2

77

1Z а

Фиг. 1

Фиг. Р

Составитель Т. Зайцева

Редактор В. Данко Техред И. Верес Корректор О. Тигор

Заказ 6068/36 Тираж 574 Подписное

ВНИИПИ Государственного комитета СССР по делам нэобретеннй и открытий

1l3035, Москва, Ж вЂ” 36, Раушская наб., д, 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4