Двоичный делитель частоты @ типа

Иллюстрации

Показать всеРеферат

ДВОИЧНЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ ИЛ ТИП.Л, содержащий четыре 11-р-п-транзистрра, два р-п-р-транзистора Н инжектирующий р-Пр-транзистор, база первого п-р-п-транзистора соединена с тактовым входом устройства, коллекторы первого и второго р-п-р-транзисторов соединены соответственно с базами третьего и второго п-р-п-транзисторов, база третьего п-р-п-транзистора подключена к первому коллектору второго п-р-п-транзистора, второй коллектор которого соединен с ба:юй четвертого п-р-п-транзистора, первый коллектор которого соединен с эмиттером первого р-п-р-транзистора, эмиттер инжектирующего р-п-р-транзистора соединен с шиной питания, а его соответствующие коллекторы - соответственно с эмиттерами р-п-р-транзисторов и базой первого п-р-птранзистора , базы всехр-п-ри эмиттеры п-р-п-транзисторов соединены с обшей umной , второй коллектор четвертого п-р-птранзистора - с выходом устройства, отличающийся тем, что, с целью увеличения быстродействия и упрощения, в него введен пятый п-р-п-транзистор, база которого соединена с третьим коллектором четвертого и первым коллектором третьего п-р-птранзистора , второй коллектор которого соединен с базой второго и первым коллектором первого п-р-п-транзисторов, второй (Л кол,1ектор первого п-р-п-транзистора подключен к базе третьего п-р-п-транзистора, база четвертого п-р-п-транзистора соединена с первым коллектором пятого п-р-птранзистора , второй коллектор которого соединен с эмиттером второго р-п-р-траизистора , соответствуюшие коллекторы инжектируюшего р-п-р-транзистора соединены соответственно с базами второго, третьего, четвертого и пятого п-р-п-транзисторов.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (11) 3 (59

OllHCAHHE ИЗОБРЕТЕНИЯ

Н АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

flO ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЬП1Ф (2I) 3608019/18-21 (22) 17.06.83 (46) 07.09.84. Бюл. № 33 (72) Ю. И. Рогозов, А. В. Глоба, Ю. М. Срывкин и А. Н. Головченко (7l) Таганрогский радиотехнический институт им. В. Д. Калмыкова. (53) 621.375.083 (088.8) (56) 1. Аваев Н. А. Дулин В. Н. Наумов К). Е

Большие интегральные схемы с инжекционным питанием. М., «Советское радио», 1977, с. 182, рис. 5.15.

2. Авторское свидетельство СССР

М 815870, кл. Н 03 К 3/286, 1980 (прототип). (54) (57) ВОИЧНЪ|И ДЕЛИТЕЛЬ ЧАС-

fOTbl И Л ТИПА, содержащий четыре п-р-п-транзистора, два р-п-р-транзистора н инжектируюгций р-п р-транзистор, база первого п-р-и-транзистора соединена с тактовым входом устройства, коллекторы первого и второго р- и-р-транзисторов соединены соответственно с базами третьего и второго п-р-п-транзисторов, база третьего n-p-n-транзистора подключена к первому коллектору второго п-р-п-транзистора, второй коллектор которого соединен с базой четвертого п-р-п-транзистора, первый коллектор которого соединен с эмиттером первого р-п-р-транзистора, эмиттер инжектирующего р-п-р-транзистора соединен с шиной питания, а его соответствукгщие коллекторы ° — соответственно с эмиттерами р-п-р-транзисторов и базой первого п-р-птранзистора, базы всех р-п-р- и эмиттеры п-р-п-транзисторов соединены с общей шинойй, второ и коллектор четвертого и- р- птрянзисторя — с выходом устройства, отличающийся тем, что, с целью увеличения быстродействия и упрощения, в него введен пятый п-р-п-транзистор, база которого соединена с т(н тьим коллектором четвертого и первым коллектором третьего и-р-птранзистора, второй коллектор которого соединен с базой второго и первым коллектором первого п-р-п-транзисторов, второй коллектор первого п-р-и-транзистора под- / ключен к базе третьего п-р-п-транзистора, база четвертого п-р-п-транзистора соеди- С непа с первым коллектором пятого п-р-птранзистора, второй коллектор которого Я соединен с эмиттером второго р-п-р-транзистора, соответствующие коллекторы инжектирующего р-п-р-транзистора соединены соответственно с базами второго, третьего, четвертого и пятого п-р-п-транзисторов.

lll2533

Изобретение относится к импульсной технике и предназначено для построения больших интегральных схем (БИС) обработки и хранения информации.

Известен JK-триггер И Л типа, который работает как двоичный делитель частоты, содержащий две бистабильные ячейки памяти, четыре элемента обратной связи, обеспечивающие взаимосвязь между бистабильными ячейками памяти. Схема выполнена на девяти. п-р-п-транзисторах, к базам которых подключены источники тока (l (.

Недостатком данного делителя являет ся сложность, что приводит к большой пло- э щади, занимаемой устройством на крнстал-, ле, большому количеству используемых транзисторов, величине контактных окон и длине межсоединеннй..

Наиболее близким по технической сущностии к изобретению явл яется двоичный делитель частоты .И Л типа, содержащий четыре п-р-п-транзистора, четыре р-п-ртранзистора и инжектирующий р-п-р-транзистор, база первого п-р-я-транзистора сое- 25 динена с тактовым входом устройства, коллекторы первого и второго р-п- р-тра нз исторов .соединены соответственно с базами третьего и второго п-р -п-транзисторов, база третьего п-р-п-транзистора подключена к первому коллектору второго п-р-п-транзистора, второй коллектор которого соединен с базой четвертого п-р-п-транзистора, первый коллектор которого соединен с эмиттером первого р-п-р-транзистора, эмиттер инжектирующего р-п-р-транзистора соединен с шиной, питания, а его соответствующие коллекторы — с эмиттерами первого и второго р-и-р-транзисторов и базой и-р-итранзистора, базы всех р-II-p- и эмиттеры п-р-п-транзисторов соединены с общей шиной, второй коллектор четвертого tl- p- fl- 40 транзистора — с выходом, третий коллектор — с базой второго Il-p-п-транзистора, коллектор третьего II-p-A-транзистора подключен к второму тактовому входу и эмиттеру третьего р-п-р-транзистора, коллектор которого подключен к базе четвертого п-р-итранзистора и коллектору четвертого и-р-и транзистора, эмиттер которого соединен с первым коллектором первого и-р-п-транзистора, второй коллектор которого подключен к эмиттеру второго р-п р-транзис- $0 тора (2(, Недостатками известного двоичного ъ делителя частоты И Л типа являются низкое быстродействие и сложность. Низкое быстродействие вызвано использованием переинжектирующих р-п-р-транзисторов, быстродействие которых в два раза меньше скорости переключения и-р-и-транзисторов.

Цель изобретения — увеличение быстро-. действия двоичного делителя частоты И Л типа и его упрощение.

Поставленная цель достигается тем, что в двоичный делитель частоты И Л типа, содержащий четыре п-р-п-транзистора, ) ва р-п-р- транзистора и инжектирующий р-п-р-транзистор, база первого п-р-п-транзистора соединена с тактовым входом устройства, коллекторы первого н второго р-п-р. транзисторов соединены соответственно с базами третьего н второго и-р-h-транзисторов, база третьего п-р-и-транзистора подключена к первому коллектору второго п-р-п-транзистора, второй коллектор которого соединен с базой четвертого п-р-п-транзистора, первый коллектор которого соединен с эмиттером первого р-п-р-транзистора, эмиттер инжек тирующего р-п-р-транзистора соединен с шиной питания, а его соответствующие кол.лекторы — соответственно с эмиттерами р-п-р-транзисторов и базой первого п-р-итранзистора, базы всех р-и-р- и эмиттеры п-р-п- транзисторов соединены с общей шиной, второй коллектор четвертого и-р-птранзистора — с выходом устройства, введен пятый n-p-n-транзистор, база которого соединена с третьим коллектором четвертого и первым коллектором третьего и-р-итранзистора, второй коллектор которого соединен с базон второго и первым коллектором первого п-р-п-транзисторов, второй .коллектор первого и-р-и-транзистора подключен к базе третьего п-р-п-транзистора, база четвертого п-р-п-транзистора соединена с первым коллектором пятого п-р-итранзистора, второй коллектор которого соединен с эмиттером второго р-и-р-транзистора, соответствующие коллекторы и нжектир уюгцего р- и-р-транзистора соединены соответственно с базами второго, третьего, четвертого и пятого п-р-п-транзисторов.

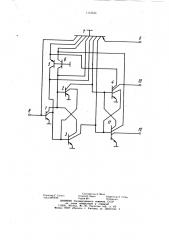

На чертеже представлена электрическая принципильная схема предложен ного делителяя.

Двоичный делитель частоты И Л типа содержит четыре и-р-и-транзистора 1 — 4, два р-и-р-транзистора 5 и 6 и инжектируюший р-п-р-транзистор 7, база первого п-р-птранзистора l соединена с тактовым входом 8 устройства, коллекторы первого н.второго р-п-р-транзисторов 5 и 6 соединены соответственно с базами третьего и второго п р п-транзисторов 3 и 2, база третьего п-р-п-транзисторов 3 и 2, база третьего

n-p-n-транзистора 3 подключена к первому коллектору второго и-р-п-транзистора 2, ; второй коллектор которого соединен с базой четвертого п-р-п-транзистора, первый коллектор которого соединен с эмиттером первого р-и-р-транзистора 5, эмиттер инжектирующего р-и-р транзистора 7 соединен

;1112533 с шиной 9 питания, а его соответствующие коллекторы — соответственно с эмиттерами р-и-р-транзисторов 5 и 6 и базой первого п-р-п-транзистора 1, базы всех р-п-ртранзисторов 5 — 7 и эмиттеры п-р-п-транзисторов 1 — 4 соединены с общей шиной, второй коллектор четвертого п-р-п-транзистора 4 с выходом 10 устройства, база пятого п-р-п-транзистора 11 соединена с третьим коллектором четвертого 4 и первым коллектором третьего 3 п-р-п-транзисторов, второй коллектор которого соединен с базой второго 2 и первым коллектором первого 1 п-р-п-транзисторов, второй коллектор первого п-р-п-транзистора l подключен к базе третьего п-р-и-транзистора

3, база четвертого п-р-и-транзистора 4 соединена с первым коллектором пятого п-р-птранзистора 5, второй коллектор которого .соединен с эмиттером второго р-и-р-транзистора 6, соответствующие коллекторы

Мнжектирующего р-и-р-тра нзнстор а 7 соединены соответственно с базами второго 2, третьего 3, четвертого 4, и пятого 11 п-р-итранзисторов, третий коллектор пятого

- п-р-п-транзистора подключен к инверсному выходу 12 устройства.

Схема устройства основывается на идентичности параметров п-р-п-транзисторов

2,3. Под идентичностью параметров понимается равенство их входных емкостей (Се х=С ) и идентичности напряжений отпирания (V q =Ц,т,) . В этом случае время отпирания каждого из транзисторов

2 и 3 зависит от величины отпирающего тока (t = ). Изменяя значения отпи-! реющих токов, можно добиться необходимого переключения транзисторов 2 н 3 триггер а.

Пусть до прихода тактового импульса высокого логического уровня транзистор

2 закрыт, транзистор 3 открыт. В этом случае ток, инжектирующий транзистором 7 в эмиттеры транзисторов 5 и 6, равный величине 1, отбирается через коллектор открытого транзистора 4 и не отбирается закрытым транзистором II. В этом случае базовый ток транзистора 3 равен величине

1, а базовый ток транзистора 2 — 1 где 1 — ток, инжектируемый транзистором 7 непосредственно в базы транзисторов2и3.

По гриходу тактового импульса, тран-зистор I открывается, отбирая через свои коллекторы базовые токи транзисторов 2 и 3, которые запираются. Запирание транзисторов 2 и 3 не вызывает изменения состояния транзисторов 4 и 11, а следовательно, базовых токов транзисторов 2 и 3. По окончании тактового импульса транзисторы 2 и 3 начинают отпираться различными по величине токами, причем базовый ток транзистора 2 больше, чем базовый ток транзистора 3. Следовательно, быстрее открывается транзистор 2, останавливая.проиесс отпирания транзистора 3 и переводя транзистор 4 в противоположное состояние.

25 Изменение состояния транзисторов 4 и 11 приводит к соответствующему изменению базовых токов транзисторов 2 и 3. В этом .случае базовый ток транзистора 2 равен

1, а базовый ток транзистора 3 — 1 +1 .

По окончании следующего тактового импульса схема изменяет свое состояние на противоположное.

Технико-экономический эффект изобретения заключается в увеличении его быстродействия н улучшения фактора технологического качества, что позволяет повысить

35 производительность устроиств, построенных на его основе, и уменьшить площадь, занимаемую на.кристалле.!! l 2533

Составитель А. Янов

Редактор С. Саенко Техред И. Верес Корректор А. Тягко, Заказ 6074/42 Тираж 86I Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

1!3035, Москва, )K — 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4