Устройство для подавления помех

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ ПОДАВЛЕНИЯ ПОМЕХ, содержащее ограничитель входного сигнала, вход которого соединен с входной шиной, последовательно соединенные резистор и конденсатор интегрирующей цепи и триггер Шмитта, отличающееся тем, что, с целью повыщения его помехоустойчивости , в него введены транзисторный и логический повторители и элемент НЕ, причем выход ограничителя входного сигнала через последовательно соединенные логический повторитель и резистор интегрирующей цепи соединен с входом транзисторного повторителя, выход которого через элемент НЕ соединен с второй обкладкой конденсатора интегрирующей цепи, выход транзисторного повторителя соединен с входом триггера Шмитта, выход которого является выходной щиной устройства. (П Фиг.1

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„SU„, 1112539 з(59 Н 03 5 01

ОПИСАНИЕ ИЗОБРЕТЕНИЯ йй,йй9 Е9 > юг. 1

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

К А ВТОРСКОМ,Ф СВИДЕТЕЛЬСТВУ (21) 3589872/18-21 (22) 11.05.83 (46) 07.09.84. Бюл. № ЗЗ (72) 1О. Н. Оболенцев (71) Специализированная проектно-конструкторская технологическая организация «Росавтоматстром» (53) 683.381 (088.8) (56) 1. Патент ФРГ № 2419521, кл. Н 03 К 5/13, 1980.

2. Авторское свидетельство СССР № 869003, кл. Н 03 К 5/13, 1980 (прототип). (54) (57) УСТРОЙСТВО ДЛЯ ПОДАВЛЕНИЯ ПОМЕХ, содержащее ограничитель входного сигнала, вход которого соединен с входной шиной, последовательно соединенные резистор и конденсатор интегрирующей цепи и триггер Шмитта, отличающееся тем, что, с целью повышения его помехоустойчивости, в него введены транзисторный и логический повторители и элемент НЕ, причем выход ограничителя входного сигнала через последовательно соединенные логический повторитель и резистор интегрирующей цепи соединен с входом транзисторного повторителя, выход которого через элемент НЕ соединен с второй обкладкой конденсатора интегрирующей цепи, выход транзисторного повторителя соединен с входом триггера Шмитта, выход которого является выходной шиной устройства.

1112539

Изобретение относится к импульсной тех никс, в частности к формирователям импул ьсов с пода влением кратковременных помех, и может быть использовано в вычислительной технике и автоматике.

Известно устройство подавления помех содержащее логические элементы НЕ и интегрируюшие цепочки, состоящие из резистора и конденсатора (1).

Недостатками данного устройства являю гся наличие двух интегрирующих цепочек и сложность получения длительных задержек.

Наиболее близким по технической сущности к изобретению является устройство, содержащее последовательно соединенные 15 триггер Шмитта, интегрирующую цепочку, а также схему ограничения входного сигнала, в которую входят диод, резисторы и стабилитроны (2).

Недостатком известного устройства является низкая помехоустойчивость при логической «1» на его входе. Это объясняется различием постоянных времен для зарядной и разрядной цели, так как при закрытом разрядном диоде резистор интегрирующей цепи отключен от входной схемы фор- 2S мирования и выполняет только функцию заряда емкости, а при открытом разрядном диоде образуется цепь разряда емкости, но кроме того должно выполниться условие обеспечения подачи напряжения логического «О» на вход триггера Шмитта. Это З0 условие соблюдается только в том случае, если резистор, через который разряжается емкость, будет на порядок и более меньше резистора интегрирующей цепи. Тем самым помехоустойчивость для входного сигнала логического «О» и логической «1» сильно отличается.

Цель изобретения — повышение помехоустойчивости устройства.

Поставленная цель достигается тем, что 40 в устройство для подавления помех, содержащее ограничитель входного сигнала, вход которого соединен с входной шиной, последовательно соединенные резистор и конденсатор интегрирующей цепи и триггер Шмит 4

45 та. введены транзисторный и логический повторители и элемент НЕ, причем выход ограничителя входного сигнала через последовательно соединенные логический повторитель и резистор интегрирующей цепи соединен с входом транзисторного повторителя, выход которого через элемент НЕ соединен с второй обкладкой конденсатора интегрирующей цепи, выход транзисторного повторителя соединен с входом триггера

Шмитта, выход которого является выходной шиной устройства.

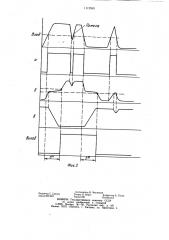

На фиг. 1 представлена функциональная схема устройства подавления помех; на фиг. 2 — временная диаграмма его работы.

Устройство содержит входную шину 1, ограничитель 2 входного сигнала, состоящий из первого резистора 3, соединенного с анодами первого 4 и второго 5 стабилитронов, катод второго стабилитрона через второй резистор 6 соединен с шиной нулевого потенциала и через диод 7 и третий резистор 8 — с шиной источника питания, катод первого стабилитрона соединен с шиной нулевого потенциала, анод диода через логический повторитель 9 и резистор

10 интегрирующей цепи — с первой обклад кой конденсатора 11 интегрирующей цепи и через транзисторный повторитель 12 и элемент НЕ 13 с второй обкладкой конденсатора интегрируюшей цепи, выход транзисторного повторителя через триггер 14

Шмитта соединен с выходной шиной 15.

Устройство работает следующим образом.

Входная схема ограничителя 2 осуществляет согласование поступающего сигнала на входную шину 1 с уровнем входного -напряжения логического повторителя 9. Ограничение входного сигнала по верхнему уровню производится стабилитроном 4, а по нижнему уровню — стабилитроном 5. Ограниченный входной сигнал по верхнему и нижнему уровню выделяется на резисторе 6 и прикладывается к катоду диода 7, а к аноду этого диода через резистор 8 прикладывается напряжение +u

Если на шину 1 устройства приложить положительное напряжение, равное

Ивх-Wa + 14n то диод 7 полностью закрыт и все напряжение +И„через резистор 8 приложено к входу логического повторителя 9, который в свою очередь сформирует сигнал логической «1». Если на вход устройства подать положительное напряжение, равное и <и то вход логического повторителя через диод

7 замкнут на резистор 6, и тем самым на его входе устанавливается напряжение логического «О.

Формирование задержки сигнала в устройстве подавления помех осушествляется интегрирующей R С-цепочкой из резистора 10 и конденсатора 11 логическим элементом НЕ 13 и транзисторным повторителем 12.

Логический элемент НЕ 13 предназначен для подключения обкладки интегрирующего конденсатора 11 к +И„или к общей шине питания, таким образом, при поступлении с логического повторителя сигнала логического «О» или логической «1» перезаряд интегрирующего конденсатора происходит по одним и тем же цепям. Кроме того, в зоне своего переключения логичес1112539 кий элемент НЕ 13 работает как активный интегратор, так как интегрирующии конденсатор 11 через транзисторный повторитель 12 охватывает логический элемент

НЕ 13 отрицательной обратной связью, по этому время задержки будет равно

t=tg+tg, где — время задержки от пассивной интегрирующей RC-цепочки; — время задержки актив2, ного интегратора.

Триггер Шмитта 14 осуществляет формирование выходного логического сигнала, причем уровень переключения его в логическую «1» выше, чем уровень переключения логического элемента НЕ 13, а уровень переключения его в логический «О» ниже.

В исходном состоянии на шину 1 устройства установлен сигнал логического «0», на выходе входной схемы ограничителя 2, логического повторителя 9, транзисторного повторителя 12 и триггер Шмитта 14 устанавливается логический «О», а на выходе логического элемента НЕ 1 3 — логическая «1» (фиг. 2). Направление заряда интегрирующего конденсатора определяется состоянием выходных сигналов логического повторителя 9 и логического элемента НЕ 13. В данный момент интегрирующий конденсатор 11 заряжен положительным напряжением с выхода логического элемента НЕ 13.

При поступлении на шину 1 устройства сигнала логической «1» на выходе логического повторителя 9 устанавливается сигнал логической «1» (фиг. 2 а), выходные сигналы транзисторного повторителя 12, триггера Шмитта 14 и логического элемента НЕ 13 не изменяют своего состояния.

Таким образом, выходы логического повторителя 9 и логического элемента НЕ 13 оказываются в состоянии логической «1», тем самым инте рирующий резистор 10 оказывастс5f пара,псльно покдюченным к интегрир ннцему конденсатору 11, и с этого момента начинал ся процесс разряда этого конденсатора. На выходе транзисторного повторите.lsf напряжение увеличивается, при достиrkcfffflf его уровня срабатывания логического элемента НЕ 13 (фиг. 2 б) начинает действовать отрицательная обратная связь. Работа логического элемента НЕ 13 в режиме активного интегратора (фиг. 2 в) продолжается до тех пор, пока íà его выходе не установится сигнал логического «О». Дальнейший процесс заряда интегрирующего конденсатора 11 продолжается за счет положительного напряжения с выхода логического повторителя 9. Когда напряжение на выходе транзисторного повторителя достигает уровня срабатывания триггера Шмит та 14, происходит его переключение и на выходе устанавливается высокий потенциал логической «1» (фиг. 2).

При поступлении на входную шину 1 устройства сигнала логического «0» процесс формирования его повторяется в обратном порядке. д5 Положительным эффектом предлагаемого устройства является то, что все помехи, которые появляются на фоне полезных сигналов логического «О» или логической «1» с длительностью импульса этой помехи

t, « t,Úт," не пропускаются на выход устройства. Кроме того, подключение интегрирующего конденсатора 11 к выходу логического элемента НЕ 13 позволяет сформировать задержки tz и т о с помощью одного конденсатора, а включение интегрирующего конденсатора 11 через транзисторный повторитель 12 в цепь отрицательной обратной связи логического элемента

НЕ 13 существенно увеличивает эффективность использования интегрирующей цепочки.

1112539

ЮБ/ХОб

Редактор С. Саенко

Заказ 6074/42

Составитель В. Мясников

Техред И. Верес Корректор А. Тяско

Тираж 861 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, ж — 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4