Аналого-цифровой преобразователь

Иллюстрации

Показать всеРеферат

АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ , содержащий последовательно включенные по стоковым выходам двухвыходовые элементы запоминания, к выходу ограниченного переноса каждого из которых подключен вход одновыходового элемента запоминания соответствующего разряда, а к входу двухвыходового элемента запоминания первого разряда через блок выборки входного сигнала подключен источник /входного сигнала, отли.чающийся тем, что, с целью повышения быстродействия и расширения функциональных возможностей преобразователя, в него введены дополнительные двухвыходовые и дополнительные одновыходовые элементы запоминания, при этом вход каждого четного дополнительного .двухвыходовЬго элемента запоминания каждого разряда подключен к стоковому выходу дополнительного двухвыходового элемента запоминания предыдущего разряда, к выходу ограниченного переноса которого через дополнительный одновыходовый элемент запоминания подключен вход нечетного, кроме первого , дополнительного двухвыходового элемента запоминания этого же раз .ряда, вход первого дополнительного двухвыходового элемента запоминания соответствующего разряда подключен к выходу одновыходового элемента запоминания предглдущего разряда, (Л соответствующие гшны выходных сигналов соединены со стоковыми вн ходами ДВУХВЫХОДОВОГО элемента запоминания и дополнительных двухвыходовых элементов последнего разряда, с выходами одновыходового элемента | ;запоминания и дополнительных одновыходовых элементов запоминания пос-j леднего разряда, входы которых подключены к выходам ограниченного пеND реноса соответствующих дополнительЛ ных двухвыходовых элементов запоминания последнего разряда. fs

СО)ОЗ СОВЕТСНИХ

СС)ЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (19) (11):

12549 А

ОПИСАНИЕ ИЗОБРЕ

И ABTOPCHOMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 2974421/18-21 (22) 13.08.80 (46) 07.09.84.Бюл. 9 33 (72) A.Â.Àíäðååâà, A.C .Ïóãà÷åâ, О.Г.Сморыго и В.Я.Стенин (71) Проектно-технологический и научно-исСледовательский институт (53) 681.325(088.8) (56) 1. Mok Т.D., Salama. С.А.Т.

Acharge - transfer-denice logic cell

"Solid-State Electronics", 1974,ч.17

)) 11, рр. 1147-1154.

2. Патент C)GA 9 4136335, кл. 340-347, 23 ° 01.79 (54)(57) АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ, содержащий последовательно включенные по стоковым выходам двухвыходовые элементы запоминания, к выходу ограниченного переноса каждого иэ которых подключен вход одновыходового элемента запоминания соответствующего разряда, а к входу двухвыходового элемента запоминания первого разряда через блок выборки входного сигнала подключен источник, входного сигнала, отли,чающий ся тем. что, с целью повышения быстродействия и расширения функциональных возможностей преобразователя, в него введены дополнительные двухвыходовые и дополнительные одновыходовые элементы запоминания, при этом вход каждого четного дополнительного, двухвыходового элемента запоминания каждого разряда подключен к стоковому выходу дополнительного двухвыходового элемента запоминания предыдущего разряда, к выходу ограниченного переноса которого через дополнительный одновыходовый элемент запоминания подключен вход нечетного, кроме первого, дополнительного двухвыходового элемента запоминания этого we раз ряда, вход первого дополнительного двухвыходового элемента запоминания соответствующего разряда подключен к выходу одновыходового элемента за- цр

Ф поминания предыдущего разряда, соответствующие шины выходных сигналов соединены со стоковыми выходами двухвыходового элемента за- С поминания и дополнительных двухвыхо- довых элементов последнего разряда, с выходами одновыходового элемента

;запоминания и дополнительных одновыходовых элементов запоминания пос-, леднего разряда, входы которых подключены к выходам ограниченного переноса соответствующих дополнительных двухвыходовых элементов запоминания последнего разряда.

1 11 (Изобретение относится к устройствам импульсной техники и предназначено для использования в цифровых из. ,Мерительных приборах, устройствах автоматического управления, в системах сбора и обработки данных.

Известен аналого-цифровой преобразователь последовательного счета на основе приборов с зарядовой свя- зью, содержащий источник входного сигнала, выход которого соединен с входом устройства выборки входного сигнала 2"-1 устройств задержки и запоминания сигнала, где и- число двоичных разрядов преобразователя, все устройства задержки и запоминания сигнала, кроме (2"-1)-ro имеют по два выхода, первый выход каждого устройства задержки и запоминания сигнала, кроме (2"-1)-го, соединен с вхоДом другого устройства задержки и запоминания сигнала, выход устройства выборки входного сигнала сое динен с входом первого устройства задержки и запоминания сигнала, выход (2 -1) -го устройства задержки и запоминания сигнала и вторые выходы остальных устройств задержки и запоминания сигнала соединены с входами

2 -1 устройств выборки выходного кода Г11 .

Недостатком данного преобразователя является большой период квантования входного сигнала, обусловленный большим временем выравнивания заряда между 2 -1 последовательно соединенными устройствами задержки и запоминания сигнала.

Наиболее близким к предлагаемому изобретению по технической сущности и достигаемому результату является аналого-цифровой преобразователь на приборах с зарядовой связью„ содержащий последовательно через согласующие элементы запоминания включенные двухвыходовые элементы запоминания, к выходу ограниченного переноса каждого из которых подключен вход одноныходового элемента запоминания соответствующего разряда, а к входу днухныходового элемента запоминания первого разряда через устройство выборки подключен источник входного сигнала L2).

Недостатком известного преобразователя является низкое быстродействие (большой период квантования) обусловленное необходимостью дополнительного этапа обратного переноса заряда из одновыходового элемента запоми нания в двухвыходоный элемент запоминания в случае, если значение кода данного разряда равно нулю. Поскольку входы управления одновыходовых элементов запоминания всех разрядов объединены, этот этап неизбежен при формировании кода каждого

12549 разряда и повторяется и раз, где и количество разрядов кода.

Быстродействие (период квантования ) известного преобразователя ограничено еще н тем, что интервал

5 времени между двумя выборками преобразуемого входного сигнала обуслонлен временем формирования полного кода одной выборки входного сигнала, поскольку следующая выборка о входного сигнала осуществляется только после завершения формирования значений всех разрядов кода предыдущей выборки входного сигнала.

Цель изобретения — повышение быстродействия и расширение функциональных возможностей преобразователя.

Поставленная цель достигается тем что в аналого-цифровой преобразова-. тель, содержащий последонательно включенные по стоковым выходам двух ныходовые элементы запоминания, к выходу ограниченного переноса каждого из которых подключен вход одно 5 выходового элемента запоминания соответствующего разряда, а к входу днухвыходоного элемента запоминания первого разряда через блок ныборки входного сигнала подключен источник нходного сигнала, введены дополнительные двухвыходовые и дополнительные одновыходовые элементы запоминания, при этом вход каждого четноFo дополнительного двухвыходового элемента запоминания каждого разряда

З5 подключен к стоковому выходу дополни. тельного двухвыходового элемента запоминания предыдущего разряда, к выходу ограниченного переноса которого через дополнительный одноныходо4р вый элемент запоминания подключен вход нечетного, кроме первого, дополнительного двухвыходового элемента запоминания этого же разряда, вход первого дополнительного двухвыходового элемента запоминания соответствующего разряда подключен к выходу.одновыходового элемента запоминания предыдущего разряда, соответствующие шины выходных сигналов соеО динены со стоковыми выходами двухвыходового элемента запоминания и допол нительных двухныходовых элементов последнего разряда, с выходами одновыходового элемента запоминания и дополнительных одновыходовых элементов запоминания последнего разряда, входы которых подключены к выходам ограниченного переноса соответст. вующих дополнительных двухвыходовых элементов запоминания последнего раз.

60 ряда.

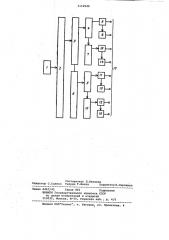

На чертеже представлена стурктурная схема аналого-цифрового преобразователя.

Устройство содержит источник 1

65 входного сигнала, блок 2 выборки вход

1112549 ного сигнала, двухвыходовые элементы 3-5 запоминания, одновыходовые ,элементы 6-8 запоминания, дополнительные двухвыходовые элементы 9-12 запоминания, дополнительные одновы- ходовые элементы 13-16 запоминания, шины 17 выходных сигналов.

Все одно- и двухвыходовые элементы 3-16 запоминания и блок 2 выборки выполнены, например, в виде управляемых тактовыми сигналами конденсаторных ячеек памяти с управляемой зарядовой связью между ними. На выходе ограниченного переноса может быть выполнен потенциальный барьер, ограничивающий перенос заряда. При этом суммарные емкости всех элементов запоминания каждого разряда равны между собой и равны емкости блока 2, т.е. где nt — период управляющих переносом заряда сигналов.

Следовательно, в предлагаемом ана25 лого-цифровом преобразователе происходит преобразование входного сигнала за и периодов управляющих сигналов где n — количество разрядов эквивалентного.двоичного позиционного ко3р да, а, период квантования входного сиг нала равен удвоенному периоду управляющих сигналов t« = 2at

Повышение быстродействия предлага емого преобразователя вдвое достигается за счет ввода дополнительных двух- и одновыходовых элементов запоминания и организацией связей так, что исключается этап обратного переноса заряда из одновыходовых в двухвыходовые элементы запоминания и в и/2 раз за счет одновременного преобразования в код нескольких последовательных выборок входного сигнала.

Процесс кодирования в предлагае45 мом преобразователе сводится к разложению аналогового сигнала на слагаемые заданной величины. Заданием соответствующего ряда весов этих слагаемых может быть осуществлено

50 преобразование с нелинейной передаточной характеристикой, что расширяет функциональные возможности преобразователя.

С2 =С +С =С4+С -+Сч+С =Сз+Са+... +Сл +С„л где Ct — емкость i-го элемента запоминания.

Аналого-цифровой преобразователь работает следующим образом.

До начала преобразования блок 2 осуществляет временную выборку входного сигнала (заряда) q (t, ) в момент времени t . В момейт времени

t с выхода блока 2 на вход двухвыходового элемента 3 поступает входной заряд q „ (t ). Если величина этого заряда йревышает максимальное значение заряда этого элемента, остаток входного заряда с его выхода ovpaниченного переноса поступает через вход на одновыходовый элемент б запоминания. В противном случае весь входной заряд будет в двухвыходовом элементе 3 запоминания.

В момент времени блоком 2 осуществляется очередная временная выбарка входного сигнала (заряда) „ (1 ). В это время заряды со стокового выхода двухвыходового элемента 3 запоминания и выхода одновыходового элемента б запоминания поступают на входы двухвыходовых эле ментов 4 и 9. В этом разряде пере- распределение поступивших зарядов между двухвыходовым элементом 4 и одновыходовым элементом 7, а также двухвыходовым элементом 9 и одновыходовым элементом 13 происходит как и в предыдущем разряде между двухвыходовым элементом 3 и одновыходовым элементом б запоминания.

В момент времени происходит передача зарядов в следующий — третий (в данном примере последний) раз ряд и осуществляется окончательное распределение зарядов, которые в виде параллельного единичного кода преобразуемой выборки входного сигнала q Ä(t ) поступают на шины 17; наличие заряда на соответствующей из шин 17 соответствует логической единице, отсутствие заряда — логичес кому нулю. При синхронном управлении элементов запоминания каждого разряда от генератора периодических управ. лякщих сигналов имеем

20 . 1 — tz,= t2 — Сл = 1л - о=

1112549

Составитель Л.Беляева

Редактор С.Саенко Техред Т.Фанта. Корректор Е.Сирохман

Закаэ 6467/43 Тираж 861 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП"Патент", г. Ужгород ул. Проектная, 4