Коммутатор

Иллюстрации

Показать всеРеферат

КОММУТАТОР, содержащий первый и второй элементы И, два источника напряжения, первый и второй ключевые элементы, выходы которых через резистор соединены с выходом устройства, а управляющие входы - с выходами соответственно первого и .второго элементов И, первые входы которых объединены и являются первой входной шиной устройства, а вторые входы также объединены и являются второй входной шкной устройства, отличающийся тем, что, с целью повышения точности, в него введены два компаратора, первые входы которых соединены с выходом устройства , вторые входы - соответственно с первым входом первого сумматора , первым источником напряжения, первым входом второго сумматора и вторым источником напряжения, при чем входы первого и второго ключевых элементов соединены соответственно с выходами первого и второго сумматоров , вторые входы которых соединены соответственно с выходами первого и второго цифроаналоговых преобразователей , входы которых соединены соответственно с выходами.первого и второго реверсивных счетчиков, вычитающий и суммирующий входы которых соединены соответственно с выходами третьего, четвертого, пятого и шестого элементов И, первые вхо (Л ды которых соединены с выходом генератора импульсов, вторые входы - соответственно через первый и второй элег1енты эадержки с выходами первого и второго элементов И, третий вход третьего элемента И через первый инвертор соединен с третьим входом четвертого элемента Н и с выходом первого компаратора, а третий вход шестого элемента И через второй инверTOD - с третьим входом пятого элемента И и выходом второго компаратора.

СОЮЗ СО8ЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (11) ЗСЮ Н 03 К 17 60! 0 06 Р 11 30

ГОСУДАРСТ8ЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И OTHPblTVN " - - ъ „ ю

ОПИСАНИЕ ИЗОБРЕТЕНИЯ ("

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 3606287/18-21 (22) 17.06.83 (46) 07.09.84. Бил. 9 33 (72) В.A.Ôàáðè÷åâ, А.И.Кондалев, Ю.М.Грешищев и Ю.А.Брайко (71) Ордена Ленина институт кибернетики им. В.М.Глушкова (53) 621.382(088.8) (56) 1. Авторское свидетельство СССР

9 599356, кл. Н 03 К 17/60, 17.10.75.

2 . Эйдукас Д.l0. и др. Измерение параметров цифровых интегральных микросхем. М., "Радио и связь", 1982, с. 266, рис. 620 (прототип). (54)(57) КОММУТАТОР, содержащий первый и второй элементы И. два источника напряжения, первый и второй ключевые элементы, выходы которых через резистор соединены с выходом устройства. а управляющие входы — с выходами соответственно первого и второго элементов И, первые входы которых объединены и являются первой входной шиной устройства ° а вторые входы также объединены и являются второй входной шиной устройства, отличающийся тем, что, с целью повышения точности, в него введены два компаратора, первые входы которых соединены с выходом устройства, вторые входы — соответственно с первым входом первого сумматора, первым источником напряжения, первым входом второго сумматора и вторым источником напряжения, причем входы первого и второго ключевых элементов соединены соответственно с выходами первого и второго сумматоров, вторые входы которых соединены соответственно с выходами первого и второго цифроаналоговых преобразователей, входы которых соединены соответственно с выходами. первого и второго реверсивных счетчиков, вычитающий и суммирующий входы которых соединены соответственно с выходами третьего, четвертого, пятого и шестого элементов И, первые входы которых соединены с выходом генератора импульсов, вторые входы — соответственно через первый и второй С элементы задержки с выходами первого и второго элементов И, третий вход Я третьего элемента И через первый инвертор соединен. с третьим входом четвертого элемента И и с выходом первого компаратора, а третий вход шестого элемента И через второй инвертоо — с третьим входом пятого элемен та И и выходом второго компаратора.

1112560

Изобретение относится к измерительной и вычислительной технике и может быть использовано в устройствах электронной коммутации.

Известен коммутатор, содержащий ключевые элементы и источник напряжения 511 .

Недостатком такого коммутатора является не высокая точность коммутации напряжения.

Наиболее близким техническим решением является коммутатор, содержащий первый и нторой элементы И, два источника напряжения, первый и второй ключевые элементы, выходы кото- 15 рых через резистор соединены с выходом устройства, а управляющие входы— с выходами соответственно первого и второго элементов И, первые входы которых объединены и являются первой 20 входной шиной устройстна, а вторые входы также объединены и являются второй входной шиной устройствас21.

Недостатком известного коммутатора является невысокая точность ком- 75 мутации напряжения в связи с различными величинами остаточных напряжений ключевык элементов.

Цель изобретения — повышение точности коммутатора. 30

Поставленная цель достигается тем, что в коммутатор, содержащий первый и второй элементы И, два источника напряжения, первый и второй ключевые элементы, выходы которых через резистор соединены с выходом устройства, а упранляющие входы — с выходами соответственно первого и второго элементов И, первые входы которых объединены и являются первой входной шиной устройства, а вторые 40 входы также объединены и являются зторой входной шиной устройства, вве ены два компаратора, первые входы которых соединены с выходом устройства, вторые входы — соответственно с 45 первым входом первого сумматора, перным источником напряжения, первым входом второго сумматора и вторым источником напряжения, причем входы первого и второго ключевых элементов соединены соответственно с выходами первого и второго сумматоров, вторые входы KQTophIx соединены соответственно с выходами первого и второго цифроаналоговых преобразователей, входы которых соединены соответственно с выходами первого и второго ренерсивных счетчиков, вычитающий и суммирующий входы которых соединены соответственно с выходами третьего, четвертого, пятого и шестого элементов И, первые входы которых соединеHhI с выходом генератора импульсов, вторые входы — соответственно через первый и второй элементы задержки с выходами первого и второго элементов 65

И, третий вход третьего элемента И через первый инвертор соединен с третьим входом четвертого элемента И и с выходом первого компаратора, а третий вход шестого элемента И вЂ” через второй инвертор — с третьим входом пятого элемента И и с выходом второго компаратора.

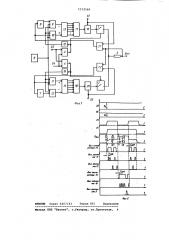

На фиг. 1 представлена функциональная схема коммутатора; на фиг, 2 временная диаграмма его работы.

Коммутатор содержит первый 1 и второй 2 ключевые элементы, первый

3 и второй 4 элементы И, резистор 5, первый 6 и второй 7 инверторы, генератор 8 импульсов, третий 9, четвертый 10, пятый 11 и шестой 12 элементы И, первый 13 и второй 14 реверсивные счетчики, первый 15 и второй

16 элементы задержки, первый 17 и второй 18 цифроаналоговые преобразователи, первый 19 и второй 20 сумматоры, первый 21 и второй 22 компараторы, первая 23 и вторая 24 входные шины, первый 25 и второй 26 источники напряжения.

Выходы первого 1 и второго 2 ключевых элементов через резистор 5 соединеиы с выходом устройства, а управляющие входы — с выходами соответственно первого 3 и второго 4 элементов

И, первые входы которых являются первой входной шиной 23 коммутатора. а вторые входы — второй входной шиной

24.

Первые входы первого 21 и второго

22 коммутаторов соединены с выходом устройства, вторые входы — соответственно с первым входом первого сумматора 19, первым источником 25 напряжения и первым входом второго сумматора 20, вторым источником 26 напряжения.

Входы первого 1 и второго 2 ключевых элементов соединены соответственно с выходами первого 19 и второго 20 сумматоров, вторые нходы которых соединены соответственно с выходами первого 17 и второго 18 цифроаналоговых преобразователей, входы которых соединены соответственно с выходами первого 13 и второго 14 реверсивных счетчиков, вычитающий и суммирующий входы которых соединены соответственно с выходами третьего

9, четвертого 10 и пятого 11, шестого 12 элементов И, первые входы которых соединены с выходом генератора 8 импульсов, вторые входы — соответственно через первый 15 и второй 16 элементы задержки с выходами первого 3 и второго 4 элементов И, третий вход третьего элемента И 9 через первый инвертор 6 соединен с третьим входом четвертого элемента

И 10 и с выходом перного компаратора

21, а третий вход шестого элемента И

12 соединен через нторой иннертор

1112560

7 с третьим входом пятого элемента

И 11 и с выходом второго компарато. ра 22.

Коммутатор работает следующим образом (фиг. 2).

При появлении на первой шине 23 логической "1" и при наличии логической "1" на второй шине 24, на выходе первого элемента И 3 устанавливается потенциал, соответствующий логическому "0", а на выходе второго 0 элемента И 4 устанавливается потенциал логической "1". При этом второй ключевой элемент 2 открывается и на выход коммутатора поступает напряжение Um + ц — дЛ . Это напряжение l5 на входе второго компаратора 22 сравнивается с входным напряжением

Если U„+ U< — aU с U„, то на выходе второго компаратора 22 устанавливается логическая "1", которая пос- р тупает на один вход пятого элемента

И 11 и второго инвертора 7. Логичес . кий "0" с выхода первого инвертора 6 запрещает прохождение импульсов с генератора 8 импульсов на вычитающий вход второго реверсивного счетчика

14. Уровень логической "1" с выхода второго элемента И 4, пройдя через второй элемент 16 задержки, разрешает занесение импульсов генератора 8 импульсов на суммирующий вход второго реверсивного счетчика 14. Одновременно уровень логического "0" с выхода первого элемента И.З, пройдя через первый элемент 15 задержки, запрещает прохождение импульсов З5 генератора 8 импульсов на суммирующий и вычитающий вход первого реверсивного счетчика 13.

Код с второго реверсивного счетчика 14, поступая на второй цифроана- 4О логовый преобразователь 18 ;фиг. 2), увеличивает напряжение на его выходе.

Это напряжение. U на втором сумматоре 20 суммируется с напряжением и на выходе коммутатора устанав- 45 лйвается напряжение U„ + Бцдп

На входе второго компаратора 22 сравнивается напряжение (tJ+ + U *q — aUq )

f — 1 и Uk . Если (UH + ВОАТ Л2 > Нн то на выходе второго компаратора 22 формируется логический "0", который инвертируется вторым инвертором 7 и разрешает .прохождение импульсов reнератора 8 импульсов на вычитающии вход второго реверсивного счетчика

14. Второй цифроаналоговый преобразователь 18 формирует напряжение

4"„ д (Ц,щ . Второй компаратор 22 опять сравйивает напряжения 0и +

Ч2 акр и U„. В зависимости от знака разности сравниваемых напряжений на выходе второго компаратора 22 формируется либо логическая "1", либо логический "0". Этот процесс повторяется до тех пор, пока на первую шину 23 поступает логический "0".

Тогда первый ключевой элемент 1 откроется, а второй ключевой элемент

2 закроется и,коррекция выходного уровня коммутатора 0 осуществляется так же как и для случая коммутации напряжения U„ . На выходах сумматоров 19 и 20 устанавливаются напряжения U + 0„, и U + U+p<,, которые позволяют компенсировать остаточное напряжение U„ H U ключевых элементов 1 и 2.

При подаче на вторую шину 24 логического "0" на выходе элементов И

3 и 4 устанавливается логический "0", который закрывает ключевые элементы

1 и 2 и запрещает прохождение импульсов генератора 8 на суммирующие и вычитающие входы реверсивных счетчиков 13 и 14. Коммутатор находится в выключенном состоянии.

Частота следования импульсов генератора 8 выбирается такой, что время прихода следующего импульса генератора 8 больше суммы времени установления напряжения на выходе ключевого элемента, времени срабатывания компаратора, реверсивного счетчика с цепями управления, цифроаналогового преобразователя и сумматора. В этом случае погрешность коррекции выходного напряжения коммутатора не превыша ет единицы кванта, так как за цикл

1 коррекции код в реверсивном счетчике изменяется на единицу младшего разряда.

Технический эффект от использова» ния предлагаемого коммутатора заключается в повышении точности коммутирующего напряжения за счет автоматической компенсации величины остаточного напряжения ключевых элементов.

ВНИИПИ Заказ 6467/4 3 Тираж 861 Поднисное

Филиал ППП "Патент", r.Óêãîðîä, ул.Проектная, 4