Многопороговый логический элемент

Иллюстрации

Показать всеРеферат

МНОГОПОРОГОВЬШ ЛОГИЧЕСКИП ЭЛЕМЕНТ по авт.св. № 936427, отличающийся тем, что, с целью ; п / расширения функциональных возможностей путем исключения прохождения тактирующих импульсов на выходную клемму , в него дополнительно введен инвертор , вход которого подключен к выходу линейного сумматора, выход соединен с третьим входом логического элемента И и с клеммой признака окончания ре 1изации переключательной функции, ретий вход логического элемента И-ПЕ соединен с клеммой сигнала начала реализации переключательной функции.

12 4 А

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (l9l (ill

SU (51) Н 03 К 19/02

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

И ABTOPCWOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

fl0 ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТ1Ф (61) 936427 (1) 3580261/18-21 (22) 18.04.83 (46) 07.09.34. Бюл, N 33 (72) И.А. 11альянов (71) Омский политехнический институт (53) 621.374(088.8) (56) 1. Авторское свидетельство СССР

Ó 936427, кл. Н 03 К 19/02, 1980. (54)(57) МНОГОПОРОГОВЬЙ ЛОГИЧЕСКИ11

ЭЛЕМЕНТ по авт.св. М 936427, о т л ич а ю шийся тем, что, с целью расширения функциональных возможностей путем исключения прохождения тактирующих импульсов на выходную клемму, в него дополнительно введен инвертор, вход которого подключен к выходу линейного сумматора, выход соединен с третьим входом логического элемента И и с клеммой признака окончания ре изации переключательной функции, .ретий вход логического элемента И-НЕ соединен с клеммой сигнала начала реализации переключательной функции.

4 11125

Изобретение относится к автомати-, ке и вычислительной технике, в частности к элементам пороговой логики

По основному авт.св. У 936427 известен многопороговый логический элемент, содержащий линейный суммаТор состОящий из ВхОдных диодов и резисторной матрицы, подключенной через разделительные диоды к первому входу логического элемента И-НЕ, 10 который образует дискриминатор, и резисторы, определяющие пороги срабатывания, В элемент введены суммирующий счетчик, соединенный с дешифратором, и логический элемент И, выход которого соединен с выходной клеммой многопорогового логического элемента, первый вход элемента И соединен с выходом логического элемента И-НЕ и со счетным входом суммирующего счетчика, второй вход подключен к выходу младшего разряда суммирующего счетчика, выходы дешифратора через резисторы, определяющие пороги срабатывания, подключены к первому входу логи-25 ческого элемента И†HE, второй вход которого соединен с клеммой тактирующих импульсов Ц .

Недостатком известного многопорогового логического элемента является то, что тактирующие импульсы поступают на выходную клемму многопорогоного логического элемента в моменты времени, когда на выходе младшего разряда суммирующего счетчика присут35 ствует сигнал логической единицы.

Кроме того, подобный элемент может быть использован только в синхронных схемах, в которых при наличии последовательно соединенных многопороговых

40 логических элементов каждый последующий многопороговый логический элемент должен начинать свою работу лишь после того, как и предыдущем многопороговом логическом элементе с наибольшим числом порогов срабаты45 вания на клемму тактирующих импульсов поступает М импульсов, где M— число порогов срабатывания элемента.

Это сужает функциональные возможности, исключает возможность применения подобного многопорогового логического элемента в схемах, где к его выходу должны подключаться другие логические устройства, содержащие элементы памяти, а также в асинхронных схемах 55 цифровых устрбйств.

Цель. изобретения — расширение функциональных возможностей путем исключения прохождения тактирующих импульсов на выходную клемму, т.е, обеспечение возможности использования многопорогового логического элемента в асинхронных схемах, а также в схемах, где к его выходу подключаются другие логические устройства, содержащие элементы памяти.

Поставленная цель достигается тем, что в многопороговый логический элемент, содержащий линейный сумматор, состоящий из входных диодов, резисторной матрицы и разделительных диодов, выход линейного сумматора подключен к первому входу логического элемента

И-НЕ, образующего дискриминатор, весовые резисторы, счетчик, дешифратор и элемент И, выход которого соединен с выходной клеммой многопорогового логического элемента, первый вход элемента И соединен с выходом логического элемента И-НЕ и со счетным входом суммирующего счетчика, второй вход подключен к выходу младшего разряда суммирующего счетчика, выходы дешифратора через весовые резисторы подключены к первому входу логического элемента И-HE второй вход которого соединен с клеммой тактирующих импульсов, выходы суммирующего счетчика соединены с соответствующими входами дешифратора, дополнительно введен инвертор, вход которого подключен к выходу линейного сумматора, выход соединен с. третьим входом логического элемента

И и с клеммой признака окончания реализации переключательной функции, третий вход логического элемента

И-НЕ соединен с клеммой сигнала начала реализации переключательной функции.

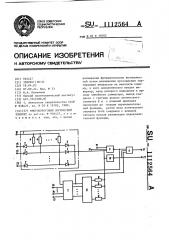

На чертеже приведена структурная схема многопорогового логического элемента.

Многопороговый логический элемент содержит линейный сумматор 1, состоящий из входных диодов 2, разделительных диодов 3 и весовых резисторов

4, образующих резистивную матрицу, дискриминатор на логическом элементе

И-HE 5, весовые резисторы 6, определяющие порог срабатывания дискримина" тора, суммирующий счетчик 7, дешифратор 8 и трехвходовой логическии элемент И 9. Каждая пара диодов 2 и 3 линейного су|.,".,атора в точках, объеди няющих их аноды„ через резисторы 4, определяющие вес входов., подключена

3 1112 к положительному полюсу источника 10 питания. Катоды диодов 3 объединены и подсоединены к первому входу логического элемента И-НЕ 5 и через резисторы 6 — к выходам дешифратора 8.

Входы дешифратора 8 соединены с выходами суммирующего счетчика 7, младший разряд которого соединен еще с одним входом логического элемента И 9. Второй вход элемента И 9 сое- ð динен с выходом логического элемента

И-НЕ 5 и со счетным входом суммирующего счетчика 7. Выход элемента И 9 подключен к выходной клемме 11 многопорогового логического элемента.

Второй вход логического элемента

И-НЕ 5 соединен с клеммой 12 тактирующих импульсов. На входные клеммы

13 линейного сумматора 1 поступают входные переменные многопорогового логического элемента. Входы 14 являют ся информационными входами суммирующего счетчика 7. Вход 15 является входом предварительной записи информации в двоичный счетчик. Вход инвертора 16 подключен к выходу линейного сумматора 1, выход — к третьему входу логического элемента И 9 и к клемме 17 сигнала окончания реализации переключательной функции.

Третий вход элемента И-НЕ 5 подключен к клемме 18 сигнала начала реализации переключательной функции. Источник питания не показан.

Иногопороговый логический элемент

3S работает следующим образом.

Перед подачей входных сигналов в клеммы 13 линейного сумматора 1, в суммирующий счетчик 7 производится запись информации пчтем подачи кола в клеммы 14 и импульса записи на вход 15. Двоичный код, записываемый в суммирующий счетчик 7, определяет количество порогов у многопорогового логического элемента. Положим, что в счетчик 7 записан код 00 ° ..О. Это

45 значит, что число порогов многопорогового логического элемента равно числу резисторов Ь. Двоичный код на выходе суммирующего счетчика 7 опре" выделяет какой из резисторов 6 подклю50 чен через соответствующий выход дешифратора 8 к отрицательному полюсу источника питания. Двоичный код

00...0 на выходах дешифратора 8 обуславливает подключение к отрицательно- му полюсу источника питания резистора 6, определяющего порог срабатывания T» . Код 00...01 вызывает подклю564 4 чение резистора 6, соответствующего порогу срабатывания Т (Т сТ ). После занесения информации в суммирующий счетчик 7 в клеммы 13 поступают входные сигналы, которые в произвольных комбинациях запирают диоды 2 ° Сигналы, поступающие в клеммы 13, в общем случае, могут сниматься с выходов подобных многопороговых логических элементов и приходить в различные моменты времени, в зависимости от момента окончания реализации переключательной функции соответствующим элементом.

Сигналы признаков окончания реализации переключательных функций многопороговыми логическими элементами, связанными с рассматриваемым элементом, поступают в клемму 18. Как только во всех многопороговых логических элементах, связанных с рассматриваемым элементом, переключательная функция реализована, то на клемме 18, связанной с входом элемента И-НЕ 5, появляется сигнал логической единицы.

Если на клеммах 13 линейного сумматора 1 присутствует комбинация входи ных переменных, для которой Е х, H c T ) то ток от. пололлтельного полюса источника 1О питания через резисторы

4 и соответствующие входному коду открытые диоды 3 переключается в цепь резистора 6, соответствующего порогу Т, вызывая на нем падение напряжения, недостаточное для сраба" тывания дискриминатора на логическом элементе И-HE 5. Тактовые импульсы, подаваемые в клемму 12, в этом случае не проходят на счетный вход суммируюшего счетчика 7, состояние которого остается исходным 00...0. Поскольку на выходе младшего разрядЬ суммирующего счетчика 7 присутствует уровень логического нуля,то и на клемме 11 многопорогового логического элемента также присутствует уровень логического нуля. На клемме 17 сигнала окончания реализации переключательной функции присутствует сигнал логической единицы, так как на входе инвертора 16 — низкий уровень напряжения.

Пусть теперь на клеммы 13 линейного сумматора 1 подана комбинация входных переменных, для которой

Т„ :Е:х„ G3; сТ<. В этом случае ток

C-1 от положительного полюса источника

10 питания через резисторы 4 и откры

1112564

Аналогичным образом происходит работа многопорогового логического элемента и при других комбинациях сигналов на клеммах 13 линейного сумматора 1. При этом тактирующие сигналы проходят на счетный вход суммирующего счетчика 7 до тех пор, и пока величина «»„ CD; превосходит

1=1 или равна порогу срабатывания, определяемому кодом, находящимся на сум50

55,тые диоды 3 переключается в цепь резисторов 6, соответствующего порогу Т, вызывая íà ««еМ падение напряжения, достаточное для срабатывания дискриминатора на логическом элементе И-НЕ 5. На выходе инвертора 16 в этом случае присутствует уровень напряжения логического нуля, запрещающий прохождение тактовых импульсов на клемму 11 многопорогового логи!

О ческого элемента через элемент И 9.

Однако тактовые импульсы, подаваемые в клемму 12, проходят на выход элемента 5 и поступают на счетный вход

15 суммирующего счетчика 7. При этом состояние суммирующего счетчика 7 изменяется с 00...0 на 00...01, вызывая, тем самым, изменение порога срабатывания дискриминатора за счет

20 подключения к отрицательному полюсу источника питания резистора 6, определяющего порог срабатывания Т. По2 скольку для поступившей на клемму 13 и 25 комбинации входных сиг««аЛоВ,.«»,CDc.Г.

2«

1=1 то потенциала от протекания тока через резистор 6, соответствующий порогу Т2, становится недостаточно для срабатывания дискриминатора на логическом элементе И-HF. 5 и инвертора 16. Следовательно поступление тактирующих импульсов на вход суммирующего счетчика 7 прекращается, на клемме 17 сигнала окончания реализа- З5 ции логической функции появляется уровень напряжения логической единицы, На клемме t1 многопорогового логического элемента, в этом с. учае, 40 формируется уровень напряжения логической единицы, так как на выходе младшего разряда счетчика 7, выходе элемента И-НЕ 5 и инверторе 16 присутствуют уровни напряжения логической единицы.

45 мирующем счетчике 7. И на выходе инвертора 16, в этих случаях, присутствует уровень напряжения логического нуля, запрещающий прохождение тактовых импульсов на выходную клемму 11 многопорогового логического элемента. На клемме 17 сигнала окончания реализации переключательной функции присутствует сигнал логичесt и кого нуля. Как только величина Е «» «,1 л

1=» становится меньше порога срабатывания, то уровень напряжения на связанных с линейным сигналом 1" входах элемента И-НЕ 5 и инвертора 16

«становится недостаточным для их срабатывания. На вьгходах элемента И-НЕ 5 инвертора 16 и клемме,17 устанавливаются уровни напряжения логической единицы. и

Если величина x» CD больше

1=1

1. четного порога и меньше нечетного, то после прекращения поступления тактирующих импульсов на счетный вход суммирующего счетчика 7, младший разряд последнего устанавливается в нулевое состояние. При этом на выходе многопорогового логического элемента формируется уровень логического нуля. и

Если величина 1«; «,1, поступившая

1 1 на входы линейного сумматора 1 боль,ше нечетного порога, но меньше четного, то после остановки суммирующего счетчика 7 в его младшем разряде находится единица, которая и определяет единичное значение функции на выходе многопорогового логического элемента.

Если перед поступлением входных сигналов на суммирующем счетчике 7 установлен код, отличный от кода

00. ° .О, то многопороговый логический элемент реализует другую переключательную функцию. При этом наименьший порог срабатывания дискриминатора определяется начальным кодом, установленным на счетчике 7.

Укаэанные изменения в структуре многопорогового логического . цемента позволяют расширить его функцио««альные возможности за счет обеспече««ия

1112564

Составитель Л. Петрова

Редактор Н. Бобкова Техред М,Тепер Корректор F.. Сирохман

Заказ 6468/44 Тираж 861 Подписное

ВНИИЛИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент" ° г. Ужгород, ул. Проектная, 4 воэможности его применения в асинхронных схемах, а также в схемах, где к выходу многопорогового логического элемента должны подключаться другие логические устройства, содержащие элементы памяти.