Декодирующее устройство

Иллюстрации

Показать всеРеферат

ДЕКОДИРУЮЩЕЕ УСТРОЙСТВО,содержащее блок фильтров, вход которого соединен с входной шиной, а выходы с входами блока синхронизации и через блок запрета с входами счетчика конт роля ошибок и первого преобразователя , выходы которОго подключены к первым входам блока элементов ИЛИ, выходы которого соединены с последовательными входами блока памяти, последовательные выходы которого подключены к вторым входам блока элементов ИЛИ и входам элементов И, параллельные выходы блока памяти соединены с дами декодера, разрешающий вход которого подключен к выходу счетчика конт-. роля ошибок, а выходы соединены с выходными шинами, первый, второй и третий выходы блока синхронизации соединены соотвественно с входами разрешения счетчика контроля ошибок и элемента И и с тактовым входам блока памяти, отличающееся тем, что, с целью повышения надежности , в устройство введены соединенные последовательно блок сумматоров,элемент памяти, второй преобразователь и S коммутатор, причем выходы первого (/) С преобразователя подключены к первым входам блока сумматоров, вторые входы которого соединены с соответствующими выхода элемента памяти, управляющий вход которого подключен к четвертому выходу блока синхронизации, при этом выходы коммутатора подключены к третьим входам блока элементов ШШ, а разрешающий вход соединен с вьрсодом элемента И.

COOS СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН

0% 01) А

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н ABTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЦПИЙ (21) 3441029/18-21 (22) 18.05.82 (46) 23.09.84. Бюл.¹ 35 (72) А.С.Ибрагимов, С.С.Казанский, А.В.Косолапов и В.В.Широков (71) Ленинградский ордена Ленина электротехнический институт им. В.И.Ульянова (Ленина) (53) 621.394.14 (088.8) (Se) 1.Юргенсон Р.И. Помехоустойчивость цифровых систем передачи телеметрической информации.Л., Энергия

1971, с.186-188.

2.Авторское свидетельство СССР

М- 785993, кл. Н03 К 23/34, 01.11.78. (54)(57) ДЕКОДИРУЮЩЕЕ УСТРОЙСТВО,содержащее блок фильтров, вход которого соединен с входной шиной, а выходы— с входами блока синхронизации и через блок запрета с входами счетчика контроля ошибок и первого преобразователя, выходы которого подключены к пер- . вым входам блока элементов ИЛИ, выходы которого соединены с последовательными входами блока памяти, последовательные выходы которого подключены з(ю Н 03 13 24 Н 03 К 13/34 к вторым входам блока элементов ИЛИ и входам элементов И, параллельные выходы блока памяти соединены с вхо- . дами декодера, разрешающий вход которого подключен к выходу счетчика конт-. роля ошибок, а выходы соединены с выходными шинами, первый, второй и третий выходы блока синхронизации соединены соотвественно с входами разрешения счетчика контроля ошибок и элемента И и с тактовым входом блока памяти, о т л и ч а ю щ е е с я тем, что, с целью повышения надежности, в устройство введены соединенные последовательно блок сумматоров,элемент памяти, второй преобразователь и коммутатор, причем выходы первого преобразователя подключены к первым входам блока сумматоров, вторые входы которого соединены с соответствующими выхода элемента памяти, управляющий вход которого подключен к четвертому выходу блока синхронизации, при этом выходы коммутатора подключены к третьим входам блока элементов

ИЛИ, а разрешающий вход соединен с выходом элемента И.

1115226 2

Изобретение относится к импульсной технике и может быть использовано при передаче и обработке информации, Известно устройство декодирования троичного кода, содержащее блок фильт- ров сигнальных признаков, блок синхронизации, блок взаимного запрета„ два декомбинатора и блок элементов ИЛИ С11

Недостаток данного устройства -невысокая надежность работы из-за большого объема оборудования.

Наиболее близким по технической сущности к изобретению является декодирующее устройство, содержащее блок !5 фильтров, вход которого соединен с входной шиной, а выходы — с входами блока синхронизации и через блок запрета с входами счетчика контроля ошибок и первого преобразователя, выхо- 20 ды которого подключены к первым входам блока элементов ИЛИ, выходы которого соединены с последовательными входами блока памяти, последовательные выходы которого подключены к вто- 25 рым входам блока элементов ИЛИ и входам элемента И, параллельные выходы блока памяти соединены с входами декодера, разрешающий вход которого подключен к выходу счетчика контроля 30 ошибок, а выходы соединены с выходными шинами, первый, второй, и третий выходы блока синхронизации соединены соответственно с входами разрешения счетчика контроля ошибок и элемента И и с тактовым входом блока памяти (21

Недостатком известного устройства является невысокая надежность функционирования, обусловленная невозмож- 40 ностью коррекции искаженного сигнального признака кода и большим числом оборудования.

Цель изобретения — повышение надежности устройства. 45

Поставленная цель достигается тем, что в декодирующее устройство, содержащее блок фильтров, вход которого соединен с входной шиной, а выходы— с выходами блока синхронизации и через блок запрета с входами счетчика контроля ошибок и первого преобразователя, выходы которого подключены к первым входам блока элементов ИЛИ, выходы которого соединены с последователь-55 ными входами блока памяти, последовательные выходы которого подключены к вторым входам блока элементов ИЛИ и входам элемента. И параллельные выходы блока памяти соединены с входами декодера, разрешающий вход которого подключен к выходу счетчика контроля ошибок, а выходы соединены с выходными шинами, первый, второй и третий выходы блока синхронизации соединены соответственно с входами блока разрешения счетчика контроля ошибок и элемента И и с тактовым входом блока памяти, введены соединенные последовательно блок сумматоров, элемент памяти, второй преобразователь и коммутатор, причем выходы первого преобразователя подключены к первым входам блока сумматоров, вторые входы которого соединены с соответствующими выходами элемента памяти, управляющий вход которого подключен к четвертому выходу блока синхронизации, при этом выходы коммутатора подключены к треть. им входам блока элементов ИЛИ, а разрешающий вход соединен с выходом элемента И.

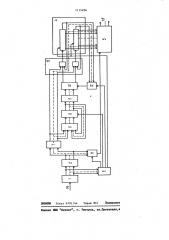

На чертеже представлена функциональная схема предлагаемого декодирующего устройства.

Устройство содержит блок 1 фильтров, блок 2 запрета, блок 3 синхронизации, блок 4 памяти, декодер 5, блок 6 сумматоров, первый преобразователь 7, элемент 8 памяти, второй преобразователь 9, коммутатор 10, счетчик 11 контроля ошибок, элемент И 12, блок

13 элементов ИЛИ, входную (вход) 14 и выходные 15 шины (выходы).

Вход 14 устройства подключен к вхо— ду блока 1 фильтров, выходы которого подключены к входам блока 3 синхронизации и блока 2 запрета, выходы которого соединены с входами счетчика

11 контроля ошибок и первого преобразователя 7. Выходы первого преобразователя 7 подключены к первым входам блока 13 элементов ИЛИ, выходы которого соединены с последовательными входами блока 4 памяти, соответствующие последовательные выходы которого подключены к вторым входам блока 13 элементов ИЛИ и .входам элемента И 12.

Параллельные выходы блока 4 памяти подключены к информационным входам декодера 5,разрешающий вход которого соединен с выходом счетчика ll контроля ошибок.

Первый, второй и третий выходы блока 3 синхронизации подключены соответственно к разрешающим входам счет3 1115 чика 11 контроля ошибок элемента И

l2 и к тактовому входу блока 4 памяти . Блок 6 сумматоров, элемент 8 памяти, второй преобразозатель 9 и коммутатор 1О соединены последовательно, причем выходы первого преобразователя 7 подключены к первым входам блока 6 сумматоров, вторые входы которого соединены с выходами элемента 8 памяти, управляющий вход которого fo подключен к четвертому выходу блока

3 синхронизации. Выходы коммутатора

10 подключены к третьим входам блока 13 элементов ИЛИ, а разрешающий вход — к выходу элемента И 12, 15

Блок 6 сумматоров представляет собой набор сумматоров, предназначенных для йоследоват льного суммирования по модулю К-1 чисел, которые соответствуют номерам сигнальных признаков кода. На элементе 8 памяти реа. лизуется. последовательное суммирование по модулю К-1. Вычисление суммы производится числом, которое является дополнением к числу К-1. Для вы- 25 числения прямого числа исполвзуется второй преобразователь 9.

Устройство работает следующим образом.

На вход блока 1 фильтров сигнальных

ЗО признаков поступает кодовая комбинация шины 14, подлежащая декодированию.

Элементы кодовой комбинации выделяются блоком 1 фильтров и поступают на входы блока 3 синхронизации и блока 2 запрета. С (К вЂ ) — выходов блока 2

35 запрета импульсы первым преобразователем 7 преобразуются в двоичный код с номером принятого сигнального признака и через блок 13 элементов ИЛИ записываются в блок 4 памяти. В блоке О 0

6 сумматоров производится последовательное вычисление суммы по модулю

К-1 поступающих двоичных чисел. Промежуточный результат суммы записывает: ся в элемент 8 памяти в моменты времени поступления импульсов с блока 3

226 4 синхронизации. С выхода элемента 8 памяти результат суммы по модулю К-1 в дополнительном к (К-1)коде поступает на вход первого преобразователя

9, который вычисляет сумму по модулю (К-1) в прямом коде.

При одиночной ошибке в коде полученное число является номером искаженного сигнального признака кода. Место ошибки в коде определяется элементом

И 12, который формирует импульс на входе коммутатора 10. По данному сигналу коммутатор 10 осуществляет восстановление искаженного элемента,кода в блоке 4 памяти, В случае уничтожения двух или более сигнальных признаков кода сбрасывает счетчик 11 контроля ошибок и не разрешает производить общее декодирование декодером 5.

После окончания приема кода блок 3 синхронизации по третьему выходу осу ществляет тактирование блока 4 памяти.

В случае одиночной ошибки в коде в блоке 4 памяти находится значение "0" сигнального признака, которое обнаруживается элементом И 12 на очередном тактовом импульсе блока 3 синхронизации.

В этом случае импульс с выхода элемента И 12 поступает на управляющий вход коммутатора 10, который производит коррекцию искаженного сигнального признака. После и тактов блока синхронизации 3 происходит восстановление информации в блоке 4 памяти.Импульс с первого выхода блока 3 синхронизации, который поступает на вход счетчика 11 контроля ошибок, осуществляет декодирование принятой кодовой комбинации на декодере 5.

Таким образом, введение блока сумматоров, элемента памяти, второго пре. образователя и коммутатора позволяет произвести обнаружение и коррекцию одиночной ошибки в кодах с основанием больше двух, что повышает надежность функционирования декодирующего устройства.

1115226

ВНИИПИ . Заказ 6791/44 Тираж 861 Подаисиое

Филиал ЯПП "Пандект", г. Ужгород, yn,Проектиая,4