Делитель частоты следования импульсов

Иллюстрации

Показать всеРеферат

ДЕЛИТЕЛЬ ЧАСТОТЫ СЛЕДОВАНИЯ ИМПУЛЬСОВ; содержащий источник входных сигналов, два элемента совпадения , вход первого из которых подключен к выходу источника входных сигналов непосредственно, а вход второго - через инвертор, элемент объединения, входы которого соединены с выходами элементов совпадения , блок совпадения, накопительный регистр и кодирующий блок, входы которого соединены с выходами накопительного регистра , а выходы - с входами блока совпадения , выход которого подключен к входу установки в «О накопительного регистра и входу управляющего триггера, отличающийся тем, что, с целью повыщения стабильности работы путем уменьшения флуктуации фронтов выходных импульсов, в него введены два элемента задержки и два дополнительных элемента совпадения, причем первый элемент задержки включен между выходом инвертора и вторым входом первого основного элемента совпадения, второй - между выходом источника входных сигналов и вторым входом второго основного элемента совпадения, первый дополнительный элемент совпадения включен между ин версным выходом управляющего триггера и входом накопительного регистра, второй - между прямым выходом и входом установки в «О управляющего триггера, а вторые входы дополнительных элементов, совпадения соединены с выходом элемента объединения. сд N3 4

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„SU„„1115241 за н 03 К 23/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМ .Ф СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (2! ) 3588573/18-21 (22) 06.05.83 (46) 23.09.84. Бюл. № 35 (72) Б. М. Породин (71) Московский ордена Ленина и ордена

Октябрьской Революции авиационный институт им. Серго Орджоникидзе (53) 621.374.32 (088.8) (56) 1. Авторское свидетельство СССР № 762200, кл. Н 03 К 23/00, 1980.

2. Авторское свидетельство СССР № 725239, кл. Н 03 К 23/00, 1980. (54) (57) ДЕЛИТЕЛЬ ЧАСТОТЫ СЛЕДОВАНИЯ ИМПУЛЬСОВ; содержащий источник входных сигналов, два элемента совпадения, вход первого из которых подключен к выходу источника входных сигналов непосредственно, а вход второго — через инвертор, элемент объединения, входы которого соединены с выходами элементов совпадения, блок совпадения, накопительный регистр и кодирующий блок, входы которого соединены с выходами накопительного регистра, а выходы — с входами блока совпадения, выход которого подключен к входу установки в «О» накопительного регистра и входу управляющего триггера, отличающийся тем, что, с целью повышения стабильности работы путем уменьшения флуктуации фронтов выходных импульсов, в него введены два элемента задержки и два дополнительных элемента совпадения, причем первый элемент задержки включен между выходом инвертора и вторым входом первого основного элемента совпадения, второй— между выходом источника входных сигналов и вторым входом второго основного элемента совпадения, первый дополнительный элемент совпадения включен между инверсным выходом управляющего триггера и входом накопительного регистра, второй— между прямым выходом и входом установки в «О» управляющего триггера, а вторые входы дополнительных элементов совпадения соединены с выходом элемента объединения.

11!524!

10 !

20

Изобретение относится к импульсной технике и может быть использовано в синтезаторах частоты и устройствах синхронизации различных систем управления, автоматики и связи, особенно в тех, где необходимо осуществлять деление частоты на полуцелые числа.

Известные делитель частоты с дробным переменным коэффициентом деления, содержащий счетчик Входных импульсов, выход которого подключен к первому входу счетчика выходных импульсов, выходу устройства и второму входу второго формирователя импульсов, первый формирователь импульсов, первый вход которого через дешифратор соединен с первым выходом счетчика выходных импульсов, а выход через элемент И вЂ” с первым входом элемента ИЛИ, второй вход которого соединен с входом устройства, фазосдвигающий элемент, вход которого соединен с входом устройства, первый выход подключен к третьему входу элемента И, а второй — к второму входу дешифратора, первый вход второго формирователя импульсов соединен с входом фазосдвигающего элемента, а выход — с вторым входом элемента И (11.

Недостатками такого делителя частоты являются неравномерность потока выходных импульсов и сложность.

Наиболее близким по технической сущности к изобретению является делитель частоты следования импульсов, содержащий источник входных сигналов, выход которого соединен непосредственно с входом первого элемента И-НЕ и через инвертор с входом третьего элемента И-НЕ, второй элемент

И-НЕ, входы которого подключены к выходам первого и третьего элементов И-НЕ, а выход соединен с входом накопительного регистра, разрядные выходы последнего через кодирующий блок подключены к входам блока совпадения. выход последнего соединен с входом установки в «О» накопительного регистра и входом управляющего триггера, прямой и инверсный выходы которого подключены к вторым входам первого и третьего элементов И-НЕ соответственно (2).

Недостатком известного устройства является существенная флуктуация моментов появления выходных импульсов, возрастающая с ростом коэффициента деления.

Цель изобретения — повышение стабильности работы путем уменьшения флуктуации фронтов выходных импульсов.

Поставленная цель достигается тем, что в делитель частоты следования импульсов, содержащий источник входных сигналов, два элемента совпадения, вход первого из которых подключен к выходу источника входных сигналов непосредственно, а вход второго через инвертор, элемент объединения. вм>ды которого соединены с выходами

»ломе!Ii,í совпадения, блок совпадения, на25

55 копительный регистр и кодирующий блок, входы которого соединены с выходами накопительного регистра, а выходы — с входами блока совпадения, выход которого подключен к входу установки в <О» накопительного регистра и входу управа яющего триггера, введены два элемента задержки и два дополнительных элемента совпадения, причем первый элемент задержки включен между выходом инвертора и вторым входом первого основного элемента совпадения, второй— между выходом источника входных сигналов и вторым входом второго основного элемента совпадения, первый дополнительный элемент совпадения включен между инверсным выходом управляющего триггера и входом накопительного регистра, второй — между прямым выходом и входом установки в

«О» управляющего триггера, а вторые входы дополнительных элементов совпадения соединены с выходом элемента объединения.

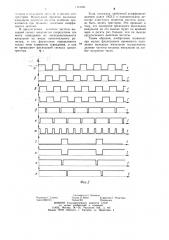

На фиг. 1 представлена структурная схема предлагаемого делителя частоты; на фиг. 2 — временные диаграммы, поясняющие его работу.

Делитель частоты следования импульсов содержит источник.1 входных сигналов, первый 2 и второй 3 элементы совпадения, выход источника входных сигналов подключен непосредственно к первому входу элемента 2 и входам элемента 3 через инвертор 4, элементы 5 и 6 задержки, между выходом инвертора 4 и вторым входом элемента 2 включен элемент 5 задержки, элемент 7 объединения подключен к выходам элементов 2 и 3 совпадения, дополнительные элементы 8 и 9 совпадения, вторые входы которых соединены с выходом элемента

7, первый вход элемента 8 подключен к инверсному выходу управляющего триггера 10, а первый вход элемента 9 — к прямому выходу триггера 10, выход элемента 9 соединен с входом установки в «О» триггера 10 и является выходом всего устройства, выход элемента 8 соединен с входом накопительного регистра 11, представляющего собой двоичный счетчик, состоящий из N последовательно включенных триггеров. Разрядные выходы накопительного регистра 11 через кодирующий блок 12 подключены к блоку 13 совпадения, который может быть выполнен в виде N-входового элемента ИНЕ. Кодирующий блок 12 осуществляет подключение входов блока 13 совпадения к соответствующим разрядным выходам регистра 11 или к своей шине логической «1» в зависимости от требуемого коэффициента деления. Кодирующий блок 12 содержит шину логической «1» и N коммутирующих элементов с двумя входами и одним выходом, в качестве которых могут быть использованы тумблеры, электромеханические реле или электронные ключи. Один из входов такого коммутирующего элемента является входом

55 блока 12, второй <п>дкл к>чс н к iiI Il II< . к>г ической «1», а его выход является выходом блока 12.

Выход блока 13 сов<<адения соединен с входом триггера 10 и входом установки в

«О» накопительного регистра.

Элементы 2,3,8 и 9 совпадения и элемент 7 объединения могут быть выполнены, например, в виде элементов И-НЕ. Элементы 5 и 6 задержки в простейшем случае представляют собой интегрирующую КС-цепочку, при этом наростание фронтон импульсов на соответствующих входах элетов 2,и 3 происходит замедленно, а срабатывание этих элементов происходит с задержкой, определяемой параметрами RCцепочки.

Делитель частоты работает следующим образом.

Входной сигнал (фиг, 2а) типа меандр с выхода источника 1 входных сигналов поступает на вход инвертора 4 и инвертируется им (фиг. 2б). На входы элемента 3 совпадения поступают инвертированный сигнал с выхода инвертора 4 и входной сигнал, задержанный элементом 6 задержки (фиг. 2в). На входы элемента 2 совпадения поступают входной сигнал (фиг. 2а) и сигнал с выхода инвертора 4, задержанный элементом задержки 5 (фиг. 2г) . В результате на выходе элемента 3 получается последовательность коротких импульсов, моменты появления которых соответствуют отрицательному перепаду входного сигнала (фиг. 2а), а на выходе элемента 2 — положительному (фиг. 2е). Элемент 7 формирует из этих двух последовательностей одну (фиг. 2ж), период повторения импульсов которой равен половине периода входного сигнала.

Пусть устройство находится в исходном состоянии. При этом триггер 10 и регистр

11 обнулены. Тогда на первом входе элемента 9 присутствует уровень логического

«О» с прямого выхода (фиг. 2з) триггера 10, а на первом входе элемента 8 — уровень логической «1» с инверсного выхода (фиг. 2и) триггера 10.

Импульсы с выхода элемента 7 проходят через элемент 8 на вход регистра 11 и накапливаются в нем. Когла число импульсов, поступивших в регистр 11, соответствует числу К, установленному в кодирующем блоке, на выходе блока 13 совпадения появляется перепад напряжения (фиг. 2к), который обнуляет регистр 11 и устанавливает триггер 10 в единичное состояние. Длительность импульса на выходе блока 13 определяется суммой задержки выключения триггеров накопительного регистра по входу установки в «О» и задержки включения блока совпадения. Если эта длительность недостаточна для срабатывания триггера 10, она может быть увеличена за счет!

О !

40 вв< дcIIIIя доно;<нит<. . !ьного э. >< <>( ки на входе установки в «(!.:: < <<(I! !

В результате переклю <(вень логического «О», а на входе элемента

9 — уровень логической «!», и (К+ 1)-й им- . пульс с выхода элемента 7 проходит только через элемент 9 на выход делителя частоты (фиг. 2л) и, кроме того, переводят триггер 10 в исходное состояние. После этого на входе элемента 9 устанавливается уровень логическо!.о «О», а на входе элемента 8 — уровень логической, и цикл работы устройства повторяется.

Длительность выходного импульса делителя частоты определяется суммой з;<держки выключения триггера 10 и задержки включения элемента 9. Если эта длптсль ность по тем или иным причинам недостаточна, то она может быть увеличена за счет введения дополнительного элемента задержки между выходом элемента 9 и входом установки в «О» триггера 10 или за счет дополнительного формирования выходного импульса делителя частоты известными методами.

Период повторения выходного сигнала делителя частоты равен 0,5 Т -(К+ !), где

Т вЂ” период повторения входного сигнала.

При этом коэффициент деления составляет 0,5 (К+!).

Таким образом, при изменении установленной с помощью коммутирующего блока емкости регистра 11 от О до К импульсов, коэффициент деления меняется от 0,5 и до

К/2 + 0,5.

Число триггеров и, которое- определяет максимальную емкость накопительного регистра, .определяется из условия

2"> 2 — 1 где щ — максимальный требуемый коэффициент деления делителя частоты.

В известном устройстве выходной сигнал является выходным сигналом накопительного регистра, т.е. последовательного цифрового делителя частоты. В силу независимости флуктуаций выходных сигналов каждого триггера, входящего в регистр, дисперсия временного положения импульсов на выходе такого регистра определяется суммой дисперсий временного положения выходных импульсов каждого триггера.

При одинаковых характеристиках триггеров, составляющих накопительный регистр, дисперсия временного положения сигнала на его выходе в п раз больше, чем та же дисперсия на выходе одного триггера (n — число отдельных триггеров в регистре1

Таким образом, в известном делителе частоты флуктуации фронтов выходHblx импульсов определяются флуктуациями

1115241 г

Составитель С. Клевиов

Реда кто р С. Саеп ко Техред И. Верее Корректор Г. Решетник

Заказ 6657/45 Тираж 861 Поднисное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4

ГИI >ГаЛа В ОГД(.н ИОК> тР>)I IгР(И ЧИСЛОМ ЭТИХ григгсров. Флуктуации фр<нггов выходных импульсов делит(,1я 1а(гогы особенно проHI). l и 1отси 111) II I)(). I b(II If « I I 0 I(I H Я х коэфф ициснта деления, Н предлагаемом д(лнтеле частоты выходной сигнал выделя(тся посредством эле мента совпадения из последовательности импульсов на входе накопительного регистра, и его флуктуации определяются только этим элементом совпадения, а они не превышают флуктуаций сигнала одного триггера... (а,; °

Если, например, требуемый коэффициент деления равен 1023,5 в накопительном регистре известного делителя частоты должно быть десять триггеров. Это приводит к тому, что дисперсия временного положения импульсов на его выходе будет по крайней мере в десять раз больше, чем на выходе предлагаемого делителя частоты.

Таким образом, изобретение позволяет при малых флуктуациях временного положения выходных импульсов осуществлять деление частоты входных импульсов на любое полуцелое число.