Устройство для определения многочлена локаторов стираний при декодировании недвоичных блоковых кодов

Иллюстрации

Показать всеРеферат

1. УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ МНОГОЧЛЕНА ЛОКАТОРОВ СТИРАНИЙ ПРИ ДЕКОДИРОВАНИИ НЕДВОИЧНЫХ БЛОКОВЫХ КОДОВ, содержащее oi блоков элементов И, входы первого из которых являются входами устройства, а блоков сумматоров , d -1 регистров, выходы которых являются выходами устройства, и генератор единиц, выходы которого являются вькодами устройства, при этом выходы каждого блока элементов И подключены к ne iBbiM входам соответствующего блока сумматоров, о т л ичающе ее я тем, что, с целью сокращения времени обработки информации при одновременном упрощении устройства, введены блок управления, дополнительный регистр, коммутатор и а-1 последовательно соединенных блоков умножения, при этом выход каждого :1-го блока умножения (, 2, ..., О-1) подключен к первым входам (i+1)-ro блока элементов И, причем входы первого блока умножения объединены с первыми входами первого блока элементов И, выходы i-ro блока сум 1аторов подключены к вторым входам (t + O-ro блока сумматоров, а выходы последнего блока сумматоров подключены к входам блока управления, первый выход которого подключен к управляющему входу коммутатора, а вторые выходы блока управления подключены к входам регистров, выходы i-го регистра (i,2,..., d-2) подключены к вторым входам (i+1)-ro регистра, а выходы последнего регистра подключега к вторым входам первого блока сумматоров и к входам дополнительного регистра, выходы которого подключены к первым входам коммутатора, к вторым входам которого подключены выходы генератора единиц, а выходы 3 коммутатора подключены к вторьм входам соответствующих блоков элементов И. 2.Устройство по п. 1, о т л и чающееся тем, что блок управления содержит распределитель, первый выход которого является первым выходом блока управления, и d -1 блоков элементов И, первые входы которых являются входами блока управления , а вторые входы соединены с соCb СП 4 4 ответствующими выходами распределителя , при этом выходы блоков элементов И являются вторыми выходами блока управления. 3.Устройство по п. 1, отличающееся тем, что регистры со второго по последний содержат на входе каждого разряда элемент ИЛИ, входы которого являются первым и вторым входами соответствующего раз ряда регистра, а выходы элементов ИЛИ подключены к входам соответствующих триггеров, выходы которых являются выходами регистров.

союз советсних соцИАлистичесних

РЕСПУБЛИК (l9l (!1» я» Н 04 L 1/10

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬС ГВУ

ГОсудАРственний нОмитет сООР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРИТЬЕ1 (21) 3610222/18-09 (22) 27.04.83 (46) 30.09.84. Бюл. Ф 36 (72) Ю.В.Сулимов и В.Н.Стальнов (53) 621.394.662(088.8) (56) 1. Передача информации 1» 30.

Экспресс-информация. 19?7, с . 26-28, рис. 3.

2. Блох Э.Л., Зяблов В.В. Обобщенные каскадные коды. М., "Связь", 1976, с. 113, рис. 3.44 (прототип). (54)(57) 1. УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ МНОГОЧЛЕНА ЛОКАТОРОВ СТИРАНИЙ

ПРИ ДЕКОДИРОВАНИИ НЕДВОИЧНЫХ БЛОКОВЫХ

КОДОВ, содержащее сМ блоков элементов

И, входы первого из которых являются входами устройства, а блоков сумматоров, д -1 регистров, выходы которых являются выходами устройства, и генератор единиц, выходы которого являются выходами устройства, при этом выходы каждого блока элементов

И подключены к первым входам соответствующего блока сумматоров, о т л ич а ю щ е е с я тем, что, с целью сокращения времени обработки информации при одновременном упрощении устройства, введены блок управления, дополнительный регистр, коммутатор и а-1 последовательно соединенных. блоков умножения, при этом выход каждого .1 -ro блока умножения (=1, 2, ..., а-1) подключен к первым входам (1+11-ro блока элементов И, причем входы первого блока умножения объединены с первыми входами первого блока элементов И, выходы i -ro блока сумматоров подключены к вторым входам (t+I)-ro блока сумматоров, а выходы последнего блока сумматоров подключены к входам блока управления, первый выход которого подключен к управляющему входу коммутатора, а вторые выходы блока управления подключены к входам регистров, выходы 1 -го регистра (=1,2,..., д -2) подключены к вторым входам (+1)-ro регистра, а выходы последнего регистра подключены к вторым входам первого блока сумматоров и к входам дополнительного регистра, выходы котсрого подключены к первым входам коммутатора, к вторым входам которого подключены выходы генератора единиц, а выходы коммутатора подключены к вторьи вхо- 3 дам соответствующих блоков элементов И.

2. Устройство по п. 1, о т л и— ч а ю щ е е с я тем, что блок управления содержит распределитель, первый B выход которого является первым выходом блока управления, и d -1 блоков элементов И, первые входы которых являются входами блока управления, а вторые входы соединены с соответствующими выходами распредели- ©» теля, при этом выходы блоков элемен- Cfl тов И являются вторыми выходами бло- «фЬ ка управления. «М

3. Устройство по п. 1, о т л и— ч а ю щ е е с я тем, что регистры со второго по последний содержат на входе каждого разряда элемент ИЛИ, ф» входы которого являются первым и вторым входами соответствующего разряда регистра, а выходы элементов

ИЛИ подключены к входам соответствующих триггеров, выходы которых являются выходами регистров.

1 11165

Изобретение относится к технике передачи дискретной информации и может быть применено в декодирующих устройствах аппаратуры передачи данных

Известно устройство для определения многочл на локаторов стираний при декодировании, содержащее генератор единиц, умножители, сумматоры и регистры L1) .

l0

Недостатком этого устройства является его сложность.

Наиболее близким к предлагаемому является устройство для определения многочлена локаторов стираний, содер- 15 жащее а блоков элементов И, входы первого из которых являются входами устройства, а блоков сумматоров, д -1 регистров, выходы которых являются выходами устройства, и генератор 2б единиц, выходы которого являются выходами устройства, при этом выходы каждого блока элементов И подключены к первым входам соответствующего блока сумматоров С23.

Недостатки известного устройства низкое быстродействие и сложность его построения.

Цель изобретения — сокращение времени обработки информации при одновременном упрощении устройства.

Поставленная цель достигается тем, что в устройство для определения многочлена локаторов стираний при декодировании недвоичных блоковых Ç5 кодов, садеражщее а блоков элементов

И, входы первого из которых являются входами устройства, а блоков сумматоров, с1 — 1 регистров, выходы которых являются-. выходами устройства, и генератор единиц, выходы которого являются выходами устройства, при этом выходы каждого блока элементов

И подключены к первым входам соответствующего блока сумматоров, введены блок управления, дополнительный регистр, коммутатор и а-1 последовательно соединенных блоков умножения, при этом выход каждого -го блока умножения (i=1,2,..., а-1) подключен к пер-50 вым входам (1+1)-ro блока элементов

И, причем входы первого блока умножения объединены с первыми входами первого блока элементов И, выходы <-ro блока сумматоров подключены к вторым 55 входам (+1)-го блока сумматоров, а выходы последнего блока сумматоров подключены к входам блока управления, 44 2 первый выход которого подключен к . управляющему входу коммутатора, а вторые выходы блока управления подключены к входам регистров, выходы

j-го регистра (=1,2. .. д -2) подключены к вторым входам (1+1)-ro регистра, а выходы последнего регистра подключены к вторым входам первого блока сумматоров и к входам дополнительного регистра, выходы которого подключены к первым входам коммутатора, к вторым входам которого подключены выходы генератора единиц, а выходы коммутатора подключены к вторым входам соответствующих блоков элементов И.

При этом блок управления содержит распределитель, первый выход которого является первым выходом блока управления, и d 1 блоков элементов И, первые входы которых являются входами блока управления, а вторые входы соединены с соответствующими выходами распределителя, при этом выходы блоков элементов И являются вторыми выходами блока управления.

Регистры с второго по последний содержат на входе каждого разряда элемент ИЛИ, входы которого являются первым и вторым входами соответствующего разряда регистра, а выходы элементов ИЛИ подключены к входам соответствующих триггеров, выходы которых являются выходами регистров.

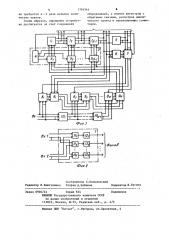

На фиг. 1 представлена структурная электрическая схема устройства для определения многочлена локаторов стираний при декодировании недвоичных блоковых кодов; на фиг. 2 — функциональная схема регистра.

Устройство для определения многочлена локаторов стираний при декодировании недвоичных блоковых кодов.содержит регистры 1, . .. 1А,, генератор 2 единиц, блок 3 управления, содержащий распределитель 4, блоки

5, ...5 1 „ элементов И, дополнительный регистр 6, коммутатор 7, блоки

8, ...,8„ элементов И, блоки 9,...,9д сумматоров, блоки 10,... 10С,, умножения, регистры 1,,..., 1 содержат элементы ИЛИ 11,,...11,„, триггеры 12,,..., 12„.

Устройство для определения много-. члена локаторов стираний при декодировании недвоичных блоковых кодов работает следующим образом.

1116544

Обрабатываемые локаторы стираний поступают на вход устройства. Количество исправляемых стираний для кода не превышает числа (d-1), где d кодовое расстояние. Первый локатор 5 .стирания обрабатывается за один двоичный такт, второй — два двоичных такта и т.д. В первый такт обработки каждого локатора стирания коммутатор

7 подключает к входам блоков 8,,...8О 10 элементов И выходы генератора .2 единиц, а в остальное время — выходы дополнительного регистра 6. Такой режим работы определяет блок 3 управления. На вход управления коммутатоI5 ра 7 подан первый выход распределителя 4. При обработке первого локатора стирания единичный сигнал с второго выхода распределителя 4 подключен к первым объединенным входам последнего блока 5б элементов И. При обГ работке (d-2) локатора единичный сигнал с (д-1)-го выхода распределителя 4 подключен к первым объединенным входам второго блока 5й элементов И.

При обработке (d-1)-го локатора единичный сигнал с cl-го выхода распределителя 4 подключен к входам первого блока 5, элементов И. В исходном.. состоянии регистры 1 обнулены. Значе30 ние первого локатора стираний через вход и выход первого блока 8 элемен-. тов И подается на входы первого блока 9 сумматоров, где складывается с "нулем", поданным с выходов послед-З5 него регистра 1. Результат поступает на входы последующих сумматоров

9,..., 9,„ и складывается с "нулем", . ! так как на входы 8,...,8о элементов

И, начиная со второго, подаются "нули" с выхопа коммутатора 7. Таким .образом. с выхода последнего блока .

9р сумматоров через входы и выходы последнего дополнительного блока

5,й 1 элементов И значение первого

45 локатора стираний записывается через первый вход в (б-1)-ый регистр 1.

В остальные регистры 1,...,1d I записываются нули, так как на первые входы блоков 5,,...,5d I элементов

И, кроме (д-2)-го, с выходов распределителя 4 подаются нулевые сигналы. На первом такте обработки второ-: го локатора его значение, проходя через вход и выход первого блока 8 элементов И, складывается в первом блоке 9 сумматоров со значением первого локатора и полученная сумма с выхода блока 8 сумматоров записывается через первый вход в (d-2)-ой регистр. В (d-1)-ый регистр через второй вход записывается "нуль" с выхода (d-2)-ro регистра. А значение первого локатора записывается с выхода (d-1)-го регистра в дополнительный регистр 6. На втором, последнем такте обработки второго локатора на выходе последнего блока 9о сумматоров получают сумму нуля с выходов (д-1) -го регистра с произведением з конечном поле значений первого.локатора с выхода дополнительного регистра 6 и второго локатора со входа устройства. С выходов блоков

10,,...,10,„, умножения получают сдвиги значений второго локатора, которые складываются в блоках

9,,...,9о сумматоров, если соответствующий разряд числа с выхода коммутатора 7 равен единице. В данном случае на выход коммутатора 7 подключено значение с выхода дополнительного регистра 6. А на вход первого блока 9, сумматоров подано нулевое значение с выхода (d-1)-го регистра. Полученное произведение запи" сывается в (д-2)-ой регистр. Значение из (с1-2)-го регистра переписывается в (д-1)-ый регистр, из (d-1)-гов дополнительный регистр 6. Остальные локаторы стираний обрабатываются аналогичным способом. При этом при обработке блок 3 управления переключает выход последнего блока 9о сумматора с первого входа 4-го регистра на первый вход (i -1) -го регистра, на остальные первые входы регист" ров 1,...,1 1 „ поданы нулевые сигналы с выходов блока 3 управления. 3апись значений чисел в триггеры 12 регистров со второго по (д-1)-ый производится по двум входам, объединенным элементами ИЛИ. После обработки всех локаторов стираний с выходов регистров 1,...1д и генератора 2 единиц получают необходимый результат.

Такое построение устройства позволяет обработать (d-1) локатор стираний sa — - — двоичных тактов. В д прототипе для обработки (д-1) лока2 торов стираний требуется (d-1) двоичных тактов. При числе обрабатываемых локаторов стираний, равном pasрядности чисел конечного поля, в предлагаемом устройстве для обработ1116544 раза меньшее колиупрощение устройстсчет сокращения

Взмок

Составитель С.Осмоловский

Редактор Н.Киштулинец Техред А.Бабинец

Корректор В. Бутяга

Заказ 6946/44 Тираж 634

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

133035, Москва, Ж-35, Раушская наб., д. 4/5

Подписное

Филиал ППП "Патент", г.ужгород, ул.Проектная, 4 ки требуется в 2 честно тактов.

Таким образом, ва достигается за оборудования, а именно регистров с обратными связями, регистров циклического сдвига и накапливающих сумматоров.