Сумматор по модулю два

Иллюстрации

Показать всеРеферат

СУММАТОР ПО МОДУЛЮ ДВА, содержащий элемент И, элемент И-НЕ и элемент задержки, причем первый и второй входа элемента ИтНЕ являются соответственно первым и вторым входами сумматора, выход элемента задержки соединен с первым входом элемента И, второй вход которого и вход элемента задержки объединены, отличающийся тем, что , с целью повышения достоверности работы , в него введены элемент Ш1И-НЕ, узел дифференцирования, расширитель импульсов и формирователь-импульсов, причем первый и второй входа элемёнта ШШ-НЕ соединены соответственно с первым и вторым входами элемента. И-НЕ, выход которого соединен с входом расширителя импульсов , выход которого соединение вторым входом элемента И, третий вход которого соединен с выходом узла дифференцирования , вход которого соединен с выходом элемента ИЛИ-НЕ , вькод элемента (Л И соединен с входом формирователя С импульсов, выход которого является выходом сумматора..

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК

0% (И) зав G 06 F 7/385

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

По ДЕЛАМ ИЗОБРЕТЕНИЙ И OTHPbrn1A

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСН0МУ СВИДЕТЕЛЬСТВУ (21 ) 361 3666/18-24 (22) 22.04..83 (46) 07.10.84. Бюп. Р 37 (72) В.П.Мочалов и В.П.Яковлев (53) 681. 3 (088. 8) (56) 1.: Паперков А.А. Логические; основы цифровых. машин и програмирование. М., "Наука", 1965, с.106, рис. 6.4.

2. Авторское свидетельство СССР

В 681429, кл.G 06 F 7/385, 1975 (прототип), (54) (57) СУММАТОР ПО МОДУЛ10 ДВА, содержащий элемент И, элемент И-НЕ и элемент задержки, причем первый и второй входы элемента И-.НЕ являются соответственно первым и вторым входами сумматора, выход элемента задержки соединен с первым входом элемента И, второй вход которого и вход элемента задержки объединены, отличающийся тем, что, с целью повышения достоверности работы, в него введены элемент ИЛИ-НЕ, узел дифференцирования, расширитель импульсов и формирователь импульсов, причем первый и второй входы элемен та ИЛИ-НЕ соединены соответственно с первым и вторым входами элемента

И-НЕ, выход которого соединен с входом расширителя импульсов, выход которого соединен с вторым входом элемента И, третий вход которого соединен с выходом узла дифференцирования, вход которого соединен с выходом элемента ИЛИ-НЕ, выход элемента

И соединен с входом формирователя импульсов, выход которого является выходом сумматора. динены соответственно с первым и вторым входами элемента И-НЕ, выход которого соединен с входом расширителя импульсов, выход которого соединен с вторым входом элемента И, третий вход которого соединен с выходом узла дифференцирования, вход которого соединен с выходом элемента KIH-HE, выход элемента И соединен с входом формирователя импульсов, выход которого является выходом сумматора.

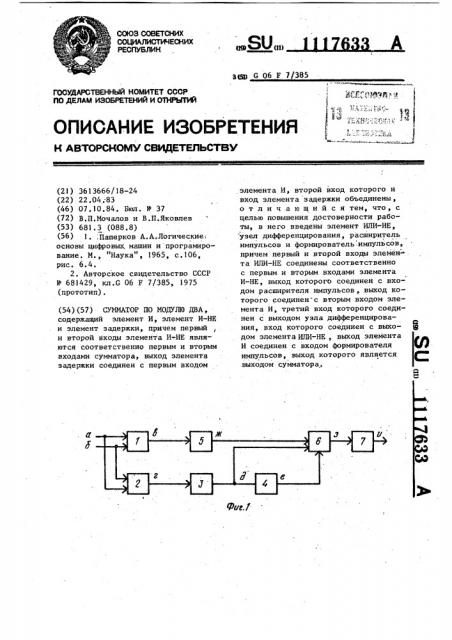

На фиг. 1 приведена функциональная схема сумматора; на фиг. 2 — временная диаграмма работы сумматора.

Сумматор по модулю два, изображенный (фиг.1) содержит элемент

ИЛИ-НЕ 1, элемент И-НЕ 2, расширитель 3 импульсов, элемент 4 задержки, узел 5 дифференцирования, элемент И 6, формирователь 7 импульсов.

Сумматор по модулю два работает следующим образом.

Длительность сигнала (фиг.l),ïîñтупающего с выхода элемента ИЛИ-НЕ 1 на суммарной длительности информационных сигналов 0, 8 . Запрещающий сигнал, поступающий с выхода элемента

И-НЕ 2 на вход расширителя 3, имеет длительность совпадающих частей информационных сигналов. Благодаря задер:жанному сигналу 6, проходящему через элемент 4 задержки .на первый вход элемента И Ь, сигналу Ф, проходящему на третий вход. элемента И 6, устраняются ложные сигналы, вызываемые рассогласованием задних и .передних фронтов информационных сигналов.Расширитель 3 и элемент 4 задержки построены таким образом, что. суммарная длительность сигналов. с их выходов равна сумме максимальных длительностей входных информационных сигналов. Выход элемента И 6 подключен к входу формирователя 7 импульсов, выход которого является выходом сумматора по модулю два.

Из временной диаграммы. (фиг. 2) видно, что достоверная работа предлагаемого сумматора сохраняется при рассогласовании во времени входных сигналов на величину, равную длительности входного сигнала, что в два раза превосходит максимально допустимое рассогласование известного сумматора.

1! 1117633 2

Изобретение относится к вычислительной технике и может быть использовано в импульсных и логических схе мах различного назначения, Известен сумматор по модулю два, содержащий элементы И-НЕ, И, ИЛИ, причем первый и второй входы элементов И-НЕ, ИЛИ подключены соответственно к первому и второму информационным входам сумматора по модулю 10 два, выходы элементов И-НЕ, ИЛИ вЂ” к первому и второму входам элемента и Я

Недостатком сумматора является сравнительно низкая достоверность функционирования.

Наиболее близким к предлагаемому является сумматор по модулю два, содержащий элементы И-HE И, ИЛИ, дополнительный элемент И и два элемента задержки, причем первый и второй входы элементов И-НЕ, ИПИ подключены соотвественно к первому и второму информационным входам сумматора по модулю два, . выходы элемейтов 25 на вход узла 5 дифференцирования, равИ-НЕ, ИЛИ вЂ” к первому и второму входам элемента И, выход элемента И-НЕ подключен к первому входу дополнительного элемента И и через первый элемент задержки к третьему входу 30 элемента И, выход которого через второй элемент задержки подключен к второму входу дополнительного элемента

И, выход которого является выходом сумматоРа по модулю два 12)

Недостатком известного устройства является низкая надежность работы в условиях значительного искажения временного положения входных сигналов, что приводит к появлению ложных 40 выходных сигналов.

Цель изобретения — повышение достоверности работы сумматора.

Поставленная цель достигается .тем, что в сумматор по модулю два, содер- 4g жащий элемент И, элемент И-HE и элемент задержки, причем первый и второй входы элемента И-НЕ являются соотвественно первым и вторым входами сумматора, выход элемента задерж-50 ки соединен с первым входом элемента И, второй вход которого и вход элемента задержки объединены, введены элемент ИЛИ-НЕ, узел дифференцирования, расширитель импульсов и фор мирователь импульсов, причем первый и второй входы элемента ИЛИ-НЕ сое1117633

Составитель В.Гречнев

Техред M.Tenep

Корректор А Зимокосов

Редактор Е.Лушникова

Подписное

Филиал ППП "Патент", r.Óæãîðîä, ул.Проектная, 4

Заказ 722!/33 Тираж 698

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Иосква, Ж-35, Раушская наб., д.4/5