Дифференциальный усилитель

Иллюстрации

Показать всеРеферат

ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ, содержащий основной дифференциальный каскад, каждое плечо которого вьшолнено в виде последовательно соединенных относительно источника питания первого транзистора, имеющего h-p-n-структуру , включенного по схеме с общим коллектором, и второго транзистора , имеющего p-f-p-структуру, включенного по схеме с общей базой, при этом коллекторы первых транзисторов объединены, а в общей цепи без вторых транзисторов включен первый источник тока, о т л и ч а ю щ и и с я тем, что, с целью увеличения быстродействия и уменьшения входных токов, в него введены первый дополнительный дифференциальньй каскад, выполненный на транзисторах, имеющих р-ц-р-структзфу, включенных по схеме с общим коллектором, с вторым и третьим источниками тока в соответствуЮ1ЦИХ цепях эмиттеров, второй дополнительный дифференциальный каскад, выполненйьй на транзисторах, имеющих р-п-р-структуру, с четвертым источником тока в общей эмиттерной цепи, элемент компенсации, выполненный на . первом транзисторе, имекщем р-п-р-структуру , с пятым источником тока в цепи эмиттера и втором транзисторе , имеющем п-р-п-структуру, коллектор которого соединен с соответствующей шиной источника питания, эмиттерс точкой соединения коллекторов первых транзисторов основного дифференциального каскада, базы первого и второго транзисторов элемента компенсации объединены, при этом базы тран (Л зисторов первого дополнительного дифференциального каскада подключены соответственно к. базам первых транзисторов основного дифференциального каскада, коллекторы объединены и подключены к соответствующей шине источника питания и к коллектору первого транзистора элемента компенсации, эмиттер которого соединен с управляющим входом четвертого источника тока, а базы транзисторов второго дополнительного дифференциального каскада подключены к соответствующим эмиттерам транзисторов первого дополнительного дифференциального каскада, коллекторы - к соответствующим эмит- . терам или коллекторам вторых транзисторов основного дифференциального каскада.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК

„,SU„, 11 27 з(д) Н 03 F 3/45

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЭОБРЕТЕНИЙ И ОТНРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ,„;:;:.;:К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 3607321/18 09 (22) 15. 06. 83 (46) 07.10.84. Бюп. а 37 (72) В.В. Матавкин .(53) 621.375.024(088.8) (56) 1. Шило В.Л. Линейные интегральные схемы. М., "Советское радио", 1979, с. 65.

2.Гребен А.Б. Проектирование аналоговых интегральных схем. М., "Энергия", 1976, с. 102 (прототип) ° (54) (57) ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ, содержащий основной дифференциальный каскад, каждое плечо которого выполнено в виде последовательно соединенных относительно источника питания первого транзистора, имеющего 6-р-и-структуру, включенного по схеме с общим коллектором, и второго транзистора, имеющего р-п-р-структуру, включенного по схеме с общей базой, при этом коллекторы первых транзисторов объединены, а в общей цепи без вторых транзисторов включен первый источник тока, о т л и ч а ю щ и й— с я тем, что, с целью увеличении быстродействия и уменьшения входных токов, в него введены первый дополнительный дифференциальный каскад, выполненный на транзисторах, имеющих р-п-р-структуру, включенных по схеме с общим коллектором, с вторым и третьим источниками тока в соответствующих цепях эмиттеров, второй дополнительный дифференциальный каскад, выполненный на транзисторах, имеющих р-п-р-структуру, с четвертым источником тока в общей эмиттерной цепи, элемент компенсации, выполненный на . первом транзисторе, имеющем р-h-р-структуру, с пятым источником тока в цепи змиттера и втором транзистоI ре, имеющем п-р-п-структуру, коллектор которого соединен с соответствующей шиной источника питания, эмиттерс точкой соединения коллекторов первых транзисторов основного дифференциального каскада, базы первого и второго транзисторов элемента компенсации объединены, при этом базы транзисторов первого дополнительного дифференциального каскада подключены соответственно к базам первых транзис- С торов основного дифференциального каскада, коллекторы объединены и под- И ключены к соответствующей шине источника питания и к коллектору первого транзистора элемента компенсации, эмиттер которого соединен с управляющим входом четвертого источника тока, "а базы транзисторов второго дополнительного дифференциального каскада подключены к соответствующим эмиттерам транзисторов первого дополнитель" ного дифференциального каскада, коллекторы — к соответствующим эмиттерам или коллекторам вторых транi зисторов основного дифференциального каскада.

Ф 1117

Изобретение относится к радиотехнике и может быть использовано в качестве входных каскадов в операционных усилителях и других аналоговых схемах.

Известен дифференциальный усили5 тель, содержащий основной дифференциальный каскад, каждое плечо которого выполнено в виде последовательно сое диненных относительно источника пита!

О ния первого транзистора, включенного по схеме с общим коллектором, и второго транзистора, включенного по схе ме С общей базой с источником тока в общей цепи баз 1 ).

Однакд данный дифференциальный . !5 усилитель обладает недостаточно хорошими динамическими параметрами при небольших значениях режимных токов

Наиболее близким по технической

20 сущности к предлагаембму является дифференциальный усилитель, содержащий основной дифференциальный каскад, каждое плечо которого выполнено, в виде последовательно соединенных 25 отнЬсутельно источника питания первого транзистора, имеющего h-p-h-структуру, включенного по схеме с общим коллектором, и второго транзистора, имеющего р-п-р-структуру, включенного по схеме с общей базой, при этом коллекторы первых транзисторов объединены, а в общей цепи без вторых транзисторов включен первый источник тока j2). 35

Известный дифференциальный усилитель обладает недостаточно высоким быстродействием и наличием нескомпенсированных входных токов.

Целью изобретения является увели- 4О чение быстродействия и уменьшение входных токов

Цель достигается тем, что в дифференциальный усилитель, содержащий основной дифференциальный каскад, 45 каждое плечо которого выполнено в виде последовательно соединенных относительно источника питания первого транзистора, имеющего h-p-и-структуру, включенного по схеме с общим кол"50 лектором„ и второго транзистора, имеющего р-h-р-структуру, включенного по схеме с общей базой, при этом коллекторы первых транзисторов объе-! динены, а в общей цепи без вторых 55 транзисторов включен первый источник тока, введены первый дополнительный дифференциальный каскад, выполненный

827 2 на трайзисторах, имеющих р-h-p-структуру, включенных по схеме с общим . t р коллектором, с вторым и третьим источниками тока в соответствующих цепях эмиттеров, второй дополнительный дифференциальный каскад, выполненный на транзисторах, имеющих р-h-p-структуру, с четвертым источником тока в общей эмнттерной цепи, элемент. компенсации, .выполненный на первом транзисторе, имеющем р-п-р-структуру, с пятым источником тока в цепи эмиттера и втором транзисторе, Имеющем

h-p-ь-структуру, коллектор которого соединен с соответствующей шиной источника питания, эмиттер — с точкой соединения коллекторов первых тран- зисторов основного дифференциального каскада, базы первого и второго транзисторов элемента компенсации объединены, при этом базы транзисторов первого дополнительного дифферен" циального каскада подключены соответ-, ственно к базам первых транзисторов основного дифференциального каскада, коллекторы объединены и подключены к соответствующей шине источника питания и к коллектору первого транзистора элемента компенсации, эмиттер которого соединен с управляющим входом четвертого источника тока, а базы транзисторов второго дополнитель,! ного дифференциального каскада подключены к соответствующим эмнттерам транзисторов первого дополнительного дифференциального каскада, коллекторы — к соответствующим змиттерам или коллекторам вторых транзисторов основного дифференциального каскада.

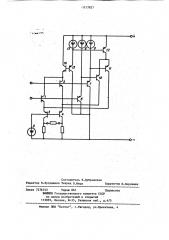

На чертеже представлена принципиальная электрическая схема предложенного дифференциального усилителя.

Дифференциальный усилитель содержит первые транзисторы 1 и 2, имеющие !

1-р-П-структуру, включенные по схеме с общим коллектором, вторые транзисторы 3 и 4 основного дифференциального каскада, имеющие р- -р-структуру„ включенные по схеме с общей базой, первый источник 5 тока, транзисторы 6 и 7 первого дополнительного дифференциального каскада, имеющие р-ft-p-структуру, включенные по схеме с общим коллектором, второй источник

8 тока, третий источник 9 тока,транзисторы 30 и 11 второго дополнительного дифференциального каскада, имеЮЩИЕ P-h-Р-Структуру, четвертЫй источник 12 тока, пятый источник 13

3 111 тока, второй транзистор 14, имеющий

h-p-й-структуру, и первый транзистор

15, имекщий р-п-р-структуру, элемента компенсации.

Дифференциальный усилитель рабо5 тает следующим образом.

Усиление входного сигнала производится основным и первым дополнитель ным дифференциальными каскадами, что обеспечивает улучшение быстродействия10 схемы усилителя. Например, скорость нарастания выходного напряжения записывается

2(3 Э )

l asrx где С - паразитная емкость или емкость частотной коррекции, а - режимный ток основного дифферен 4иального каскада

3„ - режимный ток первого допол- 2О кительного дифференциального каскада.

Улучшения быстродействия можно . достичь также, если увеличить только режимный ток основного дифференциаль-25 ного каскада. Однако это может привести к увеличению входных токов.

Включение двух транзисторов 6 и 7 р-п-р типа в базовой цепи первых транзисторов 1 и 2, а также выбор источников 8 и 9 тока, равных по величине половине значения источника

13 тока, позволяет значительно уменьшить входные токи. При этом источник

13 тока должен быть выбран меньше ве7827 4 личины эмиттернаго тока транзистора

15 который в свою очередь определяется соотношением э у ист Б (@Р) /(п I

Тогда величина скомпенсированного входного тока равна ь

/3 Р

5х б 1+)5 1+P ист е 2(1+ )2 где р„()з -, коэффициент усиления по току и-р- и (р-h-p> транзистора, Эо () - базовый ток транзистора 1(2);

7э75 эмнттерныи ток тран эистора 15;

3„ z,. — величина источника тока i-го транзистора.

Полученное соотношение справедливо при интегральном исполнении дифференциального усипителя, при котором обеспечивается идентичность компонентов и усилительных свойств транзисторов. При дискретном испблнении требуется подбор транзисторов.

В обоих случаях значения jk n-р -транзисторов могут значительно отличаться от р р-п-р-транзисторов.

Таким образом, предложенное устройство позволяет увеличить быстродействие и уменьшить входные токи в широком температурном диапазоне.

1117827

Составитель Н.Дубровская

Редактор X.Кугрышева Техред О.Неце Корректор Е.Сирохман

Заказ 7276/43 Тираж 861 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5

Филиал ППП "Патент", r.Óærîðîä, ул.Проектная, 4