Синтезатор частот

Иллюстрации

Показать всеРеферат

СИНТЕЗАТОР ЧАСТОТ, -.содержащий два генератора, один из которых является опорным генератором, а другой - управляемым генератором, последовательно соединенные первый накопительный регистр, цифроаналоговый преобразователь и фильтр нижних частот , выход которого соединен с управ ляющим входом управляемого генератора , второй накопительный регистр и Н-5-триггер, первый вход и выход которого подключены соответственно к вьпсоду переполненИя первого накопительного регистра и к входу старшего разряда цифроаналогового преобразователя , при зтом тактовый вход первого накопительного регистра соединен с выходом одного из двух генераторов , о тличающийся тем, что, с целью уменьшения уровня помех в выходном сигнале синтезатора частот, в него введен блок деления кодов, выходы целой и дробной частей которого подключены соответственно к кодовому входу первого накопительного регистра и к первому кодовому входу второго накопительного регистра, выход переполнения которого соединен с входом переноса первого накопительного регистра, первый кодовый вход блока деления кодов является входом делимого синтезатора частот, второй кодовый вход блока деления кодов объединен с вторым кодовым входом второго накопительного регистра и является входом делителя синтезатора частот, тактовый вход второго накопительного регистра; объединен с тактовым входом бло(са деления кодов и подключен к тактовому входу первого накопительного регистра , а второй вход В-5-триггера соединен с выходом другого из двух генераторов.

СОЮЗ COBETCHHX

WIWWHNK

РЕСПУБЛИК з(у) Н 03 L 7/18

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЬГГИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ К AST0PCHOIVIV СВИДЕТЕЛЬСТВУ

Я / (21) 346)661j18-09 (22) 05.07.82 (46) 07.10.84. Бюл. В. 37 (72) В.И.Козлов (53) 621.373.42(088.8), (56) 1. Патент США И 3913028, кл. 331-1А, 14.10.75.

2. Козлов В.И. Способ цифрового фазового детектирования. "Радиотехника"; 1980, У 4, с.25-29 (прототип). (54)(57) СИНТЕЗАТОР ЧАСТОТ, содержащий два генератора, один иэ которых является опорным генератором, а дру" гой — управляемым генератором, последовательно соединенные первый накопительный регистр, цифроаналоговый преобразователь и фильтр нижних частот, выход которого соединен с управляющим входом управляемого генератора, второй накопительный регистр и

8-э-триггер, первый вход и выход которого подключены соответственно к выходу переполнения первого накопительного регистра и к входу старшего разряда цифроаналогового преобра- зователя, при этом тактовый вход первого накопительного регистра со„,SU„„1117839 А единен с выходом одного из двух генераторов, отличающийся тем, что, с целью уменьшения уровня помех в выходном сигнале синтезатора частот,в него введен блок деления кодов, выходы целой и дробной частей которого подключены соответственно к кодовому входу первого накопительного регистра и к первому кодовому входу .второго накопительного регистра, выход переполнения которого соединен с входом переноса первого накопительного регистра, первый кодовый вход блока деления кодов является входом делимого синтезатора частот, второй кодовый вход блока деления Е кодов объединен с вторым кодовым входом второго накопительного регистра и является входом делителя синтезатора частот, тактовый вход второго накопительного регистра объе- Сй динен с тактовым входом бло*а деления кодов и подключен к тактовоМиюб му входу первого накопительного регистра, а второй вход B-5-триггера соединен с выходом другого иэ двух генераторов. 00

СФ нератора, второй накопительный ре-. гистр и R-g-триггер, первый вход и выход которого подключены соответственно к выходу переполнения первого накопительного регистра и к вхо"

5 ду старшего разряда цифроаналогового преобразователя, при этом тактовый вход первого накопительного регистра соединен с выходом одного из

1О двух генераторов, введен блок деления кодов, выходы целой и дробной частей которого подключены соответственно к кодовому входу первого накопительного регистра и к первому кодовому входу второго накопительного регистра, выход переполнения которого соединен с входом переноса первого накопительного регистра, первый кодовый вход блока деления кодов является входом делимого син20 тезатора частот, второй кодовый вход блока деления кодов объединен с вторым кодовым входом второго накопительного регистра и является входом делителя синтезатора частот, тактовый вход второго накопительного регистра объединен с тактовым входом блока деления кодов и подключен к тактовому входу первого накопительного регистра, а,второй вход

30 R-5-триггера соединен с выходом дру" гого из двух генераторов.

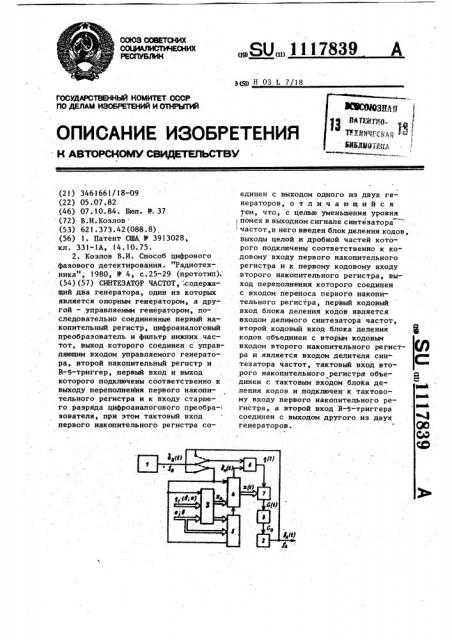

На чертеже изображена структур" ная электрическая схема синтезатора частот.

Синтезатор частот содержит опорный 1 и управляемый 2 генераторы, блок 3 деления кодов, первый накопительный регистр (HPt 4, вФорой НР

S, R-5-триггер 6, цифроаналоговый преобразователь (ЦАП) 7, фильтр нижних частот {ФНЧ) 8.

Синтезатор частот работает следующим образом.

Блок 3 деления кодов, а также

45 первый и второй HP 4 и 5 тактируются импульсами последовательности с большей частотой, например выходными импульсами о (1} управляемого генератора с частотой Е 1. Этот случай показан на чертеже сплошными линиями.

Блок 3 деления кодов вырабатывает целую Х и дробную Х части дроби —

«Ь где „2" — емкость первого HP 4, — число разрядов HP 4, а и Ьнаименьшие целые числа, удовлетворяющие условию bk< фчастота опорного генератора I. Ha кодовые входы блока 3 деления кодов поступают соответственно значения делимого и де1 11! 7839

Изобретение относится к радиотехнике и может использоваться для получения сетки стабильных частот в приемопередающей и измерительной аппаратуре.

Известен синтезатор частот, содержащий первый и второй накопительные регистры, выходы которых через цифровой сумматор соединены с цифроаналоговым преобразователем, а также фильтр нижних частот и перестраиваемый генератор, выход которого йодключен к тактовому входу первого накопительного регистра, а к тактовому входу второго накопительного регистра подключен выход опорного генератора (1 J.

Однако данный синтезатор частот имеет недостаточно широкий диапазон рабочих частот, который ограничен быстродействием цифрового сумматора, а также высокий уровень помех в выходном сигнале синтезатора.

Наиболее близким по технической сущности к изобретению является синтезатор частот, содержащий два генератора, один из которых является опорным генератором, а второй— управляемым генератором, последовательно. соединенные первый накопительный регистр, цифроаналоговый преобразователь и фильтр нижних частот, выход которого соединен с управляющим входом управляемого генератора, второй накопительный регистр и R-5-триггер, первый вход и выход которого подключены соответственно к выходу переполнения первого накопительного регистра и к входу старшего разряда цифроаналогового преобразователя, при этом тактовый вход первого накопительного регистра соединен с выходом одного иэ двух генераторов 1 2 ). .Однако известный синтезатор час- тот также имеет высокий уровень помех.

Цель изобретения — уменьшение уровня помех в выходном сигнале синтезатора частот.

Поставленная цель достигается тем, что в синтезатор частот, содержащий два генератора, один из которых является опорным генератором, а другой — управляемым генератором, последовательно соединенные первый накопительный регистр, цифроаналоговый преобразователь и фильтр нижних частот, выход которого соединен с управляющим входом управляемого ге"

4f >-fq х/ „= „Ь/ш

Составитель Ю.Ковалев

Техред C.Ìèãóíîâà Корректор А.Зимокосов

Редактор В.Данко

Заказ 7276/43 Тираж 8б! Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4

3 11 лителя. Последний используется так- же для управления емкостью второго

HP 5, т.е. в данном случае с -с .

Частное х и остаток дх поступают о на кодовые входы соответственно пер.вого HP 4 и второго HP 5. При заполнении второго HP 5 импульс переноса переходит в первый HP 4. Оба накопительйых регистра выполняют, таким образом, роль единого регистра, производящего накопление числа

x- %„Ь/e= X o+d xi@

Импульсы переполнения о „ (Ц первого

HP 4 воздействуют на один из входов

R-5-триггера б, на другой вход которого поступают импульсы последовательности с меньшей частотой, например импульсы опорной частоты с выхо да опорного генератора 1, как пока- зано на чертеже сплошной линией.

Триггер выполняет роль фазового детектора. Импульсы, переключений q,(

В петле фазовой автоподстройки достигается равенство опорной частоты f среднему значению частоты пеВ реполнения .Ед первого HP 4, т.е.

Следовательно, выходная частота синтезатора равна j>=f< a/Ь, Изменяя числа о и Ь, можно управлять выходной частотой и.шагом сетки частот синтезатора.

17839 4

Помеха дробности, возникающая в системе за счет некратности чисел х и q, компенсируется путем преобразования текущего значения числа х() на выходе НР 4 с помощью ЦАП 7.

При этом старший разряд HP 4 подклю:чается к второму от старшего разряда ЦАП 7. Этим достигается весовое соответствие процессов х() и с1,(Ц, необходимое для полной компенсации помех дробности.

Число разрядов ЦАП 7 и первого

HP 4 выбирается исходя из требований к подавлению помех дробности.

Долей нецикличности, вносимой переполнениями второго HP 5, в этом случае можно пренебречь. Подавление помех раСтет пропорционально емкости

%1 °

Тактовый вход у блока 3 деления кодов может отсутствовать, например, при:выполнении его на элементах комбинационной логики. Делимое Ь на входе этого блока фактически представляет собой число Ь, подаваемое

25 со сдвигом íà и разрядов в сторону старшего числа.

При > Е и, соответственно, Ь>с1 (связи для этого случая показаны на чертеже штриховыми линиями ) числа cl и Ъ взаимно меняются местами Тогда ХА п в х/Ф„ f a/Ü

Делимое и делитель меняются местами, и при постоянном шаге сетки частот емкость второго HP 5 при этом остается неизменной. Кроме того, уровень помех дробности в этом случае ниже, так как коэффициент передачи системы фазовой автоподстройки для этих помех уменьшается в соответ,ствующее число раз.