Цифровой фазовый детектор

Иллюстрации

Показать всеРеферат

ЦИФРОВОЙ ФАЗОВЫЙ ДЕТЕКТОР, содержащий ограгничитель, первьй и вто рой логические элементы, первый и второй счетчики, цифровой процессор последовательно соединенные генератор первый и второй делители частоты и эталонный счетчик, блок памяти, при, чем выходы второго делителя частоты соединены с блоком памяти, lepBt входы первого и второго логических элементов соединены с ограничителем, выходы логических элементов соединены . соответственно С- входами управления первого и второго счетчиков, выходы которых подключены к цифpoвo €y процессору , о т л и ч a ю щ и и с я тем, что, с целью расширения диапазона рабочих частот и повышения точности, в него введен коммутатор, причем выходы коммутатора соединены с вторыми входами первого и второго логических эглементов, первые входы коммутатора подключены к эталонному счетчику, a вторые входы - к блоку памяти, выход генератора импульсов соединен с входами первого и второго счетчиков.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК

ГОСУДАРСТВЕННЫИ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИИ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ (21) 3597538/18-21 (22) 30.05.83 (46) 15.10.84. Бюл.138 (72) И.Ф.Глумов, В.И.Кокорин, В.П.Майко,Н.В.Салюк, M.Á.Òîâáèñ и M.Ê.×ìûõ (71) Научно-производственное объединение "Сибцветметавтоматика" и Красноярский политехнический институт (53) 621.317.77(088.8) (56) 1. Авторское-свидетельство СССР

9773517, кл. Q 01 К 25/08, 1978.

2. Патент Франции к- 2417116, кл. Я 01 К 25/00; С 01 С 21/04, 1979. (54) (57) ЦИФРОВОЙ ФАЗОВЫЙ ДЕТЕКТОР, сод4ржапщй ограничитель, первый и второй логические элементы, первый

° и второй счетчики, цифровой процессор, последовательно соединенные генератор, первый и второй делители частоты и эталонный счетчик, блок памяти, при-, е

„5U„„, 1.118933 А

3(д) 6 01 R 25/ОО 01 и 25 08 чем выходы второго делителя частоты соединены с блоком памяти, первьФ входы первого и второго логических элементов соединены с ограничителем, выходы логических элементов соединены, соответственно с.входами управления первого и второго счетчиков, выходы которых подключены к цифровому процессору, отличающийся тем, что, с целью расширения диапазона рабочих частот и повышения точности, в него введен коммутатор, причем выходы коммутатора соединены с вторыми входами первого и второго логических элементов, первые входы коммутатора подключены к эталонному счетчику, а вторые входы к блоку памяти, выход генератора импульсов соединен с входами первого и второго счетчиков.

1 1118

Изобретение относится к измерительной технике и может быть использовано для измерения фазового сдвига сигналов в.широком динамическом и частотном диапазоне.

Известен измеритель сдвига фаз электрических сигналов, содержащий два ключа, соединенных с входом н выходом формирователя сигнала ортогонального опорному, выходы ключей соединены с интеграторами, подключенными к вычислителю, соединенному с регистратором $1(.

Однако известное устройство имеет большую погрешность измерения фазовых

15 сдвигов за счет использования аналоговых интеграторов и вычислителя.

Известен также цифровой фазовый детектор, содержащий ограничитель, подключенный к первым входам первого и второго логических элементов, первый и второй измерительные счетчики. соединенные с цифровым процессором, блок памяти, последовательно соеди.— ненные генератор, первый (программнъпЪ) и второй (фиксированный) делители частоты и эталонный счет-. чик, выходы которого соединены с вторыми входами первого и второго логических элементов,.выходы логи- ческих элементов соединены соответственно с входами управления первого и второго измерительных счетчиков, другие входы которых подключены к выходу первого делителя частоты, входы управления первого дели- З5 теля частоты соединены с блоком памяти, входы которого подключены к второму делителю частоты 2 1.

Недостатки данного фазового детектора заключаются в узком диапа- 40 зоне рабочих частот, ограниченном сверху максимально возможной скоростью управления коэффициентом деления первого делителя частоты, и низкой точности измерения фазо- 45 вых сдвигов, обусловленной изменением в широких пределах частоты счетных импульсов, поступающих на счетчики.

Цель изобретения — расширение 50 диапазона рабочих частот и повышение точности измерения фазового сдвига.

Указанная цель достигается тем, что в цифровой фазовый детектор, .э- 55 держащий ограничитель, первый и т.орой логические элементы, первый и втррой счетчики, цифровой про.

933 2 цессор, последовательно соединенные

f енератор, первый н второй делители частоты и эталонный счетчик, блок памяти, причем выходы второго делителя частоты соединены с блоком памяти, первые входы первого и второго логических элементов соединены с . ограничителем; выходы логических элементов соединены соответственно с входами управления первого и второго счетчиков, выходы которых .подключены к цифровому процессору, введен коммутатор, причем выходы коммутатора соединены с вторыми входами, первого и второго,логических элементов, первые входы коммутатора подключены к эталонному счетчику, а вторые входы — к блоку памяти, выход генератора импульсов соединен с вход ми первого и второго счетчиков.

Использование коммутатора, управляемого блоком памяти, позволяет расширить диапазон рабочих частот и повысить точность измерения, поскольку исключается процесс управления коэффициентом деления первого делителя частоты, а частота счетнйх импульсов, поступающих на измерительные счетчики, остается постоянной и равной частоте генератора импульсов.

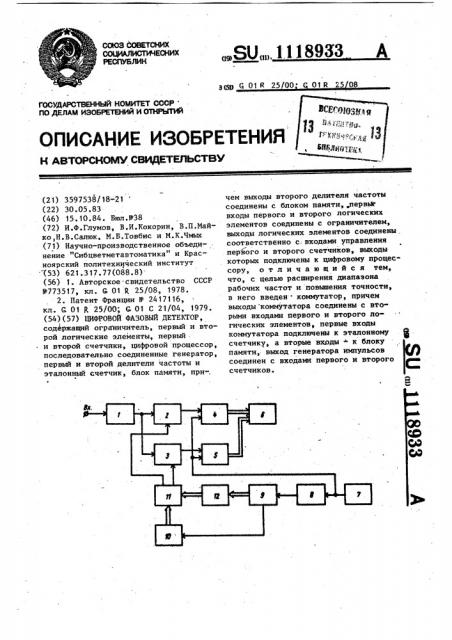

На чертеже приведена структурная схема цифрового фазового детектора.

Устройство содержит ограничитель

1, соединенный с первыми входами первого 2 и второго 3 логических элементов, первый ч и второй 5 счетчики, соединенные с цифровым процессором

6, последовательно соединенные генератор 7, первый 8 и второй 9 делители частоты, эталонный счетчик 10, коммутатор 11 блок памяти 12.

Устройство работает следующим образом.

Ограничитель 1 преобразует входной сигнал известной частоты в прямоугольные импульсы, поступающие на логические элементы 2 и 3. С выхода коммутатора 11 два прямоугольных эталонных колебания известной частоты, равной частоте входного сигнала, перемножаются в логических элементах 2 и 3 с прямоугольными импульсами входного сигнала, причем первое колебание поступает на логический элемент 2, второе, сдвинутое на 90 относительно первого, 30

tg +g -cf ср 2

3 11189 на логический элемент 3. Импульсные сигналы с выходов логических элементов 2 и 3 используются для управления режимом работы счетчиков 4 и 5, которые обеспечивают педсчет коли5 чества импульсов генератора 7. Количество импульсов, поступивших в счетчики 4 и 5, пропорционально косинусу и синусу измеряемого фазово-. го сдвига. 10

В цифровом процессоре 6 по окончании цикла измерения вычисляется отношение кодов чисел, накопленных в счетчиках 4 и 5, и берется функция арктангенса от этого отношения.

Синхронизация измерений осуществляется от генератора 7, а анализ смены информации счетчиков произво" дится процессором 6 по состоянию младших разрядов.

Поскольку характеристика, в соответствии с которой работает фазовый детектор, не гармоническая, а треугольная, результат вычисления фазового сдвига через арктангенс двух негармонических величин содержит погрешность измерения, максимальная величина которой превышает 4, а период повторения знакопеременной зависимости погрешности измерения от фазового сдвига составляет 90 . Для уменьшения указанной погрешности измерения сигнал с выхода генератора

7 поступает через первый делитель частоты 8 на второй делитель частоты

9. К выходу второго делителя частоты З5

9 подключен эталонный счетчик 10, который формирует и пар квадратур .ных эталонных сигналов, сдвинутых относительно друг друга на угол

Ч=90 /и. 40

При известной длительности времени измерения фазового детектора (Ти) последнее разбивается на и тактов

2 Т (для и 2 формируется два такта измерения Т> и Т2 причем 4>

1 2

Формирование тактов измерения осуществляется блоком памяти 12 путем опроса адресов блока памяти 12 сигналами с выходов второго делителя час- >0 тоты 9. Блок памяти 12 управляет коммутатором 11, в соответствии с сигналами управления. Длительность времени измерения Т„ фазового детектора разбивается на такты (Т, Т ... Т„), в течение которых коммутатором

11 к входам логических элементов 2 и 3 подключаются соответствующие па33 4 ры квадратурных составляющих эталонного колебания.

По окончании первого. такта измерения в счетчиках 4 и 5 зафиксированы коды чисел, пропорциональные соответственно косинусу синусу измеряемого фазового сдвига Ч,, значение которого определяется через арктангенс отношения измеренных величин в цифровом процессоре 6."

В течение второго такта измерения

Т коммутатор 11 подключает к логи2 ческим элементам 2 и 3 пару квадратурных эталонных сигналов, сдвинутых относительно эталонных сигналов в первом такте измерения на угол

V-90 /n.

По накопленной в счетчиках 4 и 5 информации по окончании второго такта измерения цифровым процессором

6 .определяется измеренный фазовый сдвиг Ч . Таким образом, в каждом последующем такте,.измерения коммутатор 11 подключает к логическим элементам 2 и 3 два квадратуриых эталонных сигнала, сдвинутых относительно эталонных сигналов преды дущего такта измерения на угол

90o/и, и в цифровом процессоре 6 определяется измеренный фазовый сдвиг.

Результат измерения среднего значения фазового сдвига за время Т„ определяется цифровым процессором

6 по Формуле „+(Ч- } (Ч -2VJ+.. +(У -(n-1fV)

cp . n

X. ч,. п-4 („1

2 п так как о Ч; эр 1=1 1 1 90 (2) и сРДля случаев п=2 среднее значение фазового сдвига равно

Таким образом, усредняя измерения за и тактов при различных значениях фазовых сдвигов эталонных сигналов, можно уменьшить погрешность измерения фазовых сдвигов, обусловленную негармонической характеристикой фазового детектора.

3 1118933

Составитель В. !!!убин

Редактор А, Гулько Техред С. Мигунова Корректор В. Гирняк

Заказ 7445/3 2 Тираж 710 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

11.3035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП - Патент", r. Ужгород, ул. Проектная, 4

Так, в простейшем случае при

h=2 погрешность измерения уменьшается на порядок и составляет менее 0,5 по сравнению с исходной.

В качеств" логических элементов 5

2 и 3 могут применяться элементы

ИСКЛ!ОЧАЮЩЕЕ ИЛИ, обеспечивающие логическое умножение входных сигналов.

При практической реализации фа-, зового детектора счетчики 4 и 5 могут быть выполнены в виде реверсивных или в виде сумьырующих счетчиков.

В случае применения реверсивных счетчиков 4 и 5 сигналы с выходов логических элементов 2 и 3 управляют рережимом счета, т.е. в моменты совпадения полярностей входных импульсов логических элементов 2 и 3 реверсивные счетчики работают на суммирование, при несовпадении полярностей входных импульсов логических элементов

2 и 3 — на внчйтание. При использовании суммирующих счетчиков 4 и 5 в моменты совпадения полярностей входных импульсов логических элементов 2 и 3 счетчики 4 и 5 суммируют импульсы, поступающие от генератора .7, при несовпадении полярностей входных импульсов логических элементов 2 и 3 — не считают. Для вычисления фазового сдвига (в этом случае в цифровом процессоре 6) результаты, полученные за такт измерения в счетчиках 4 и 5 центрируются, 35 т.е. из этих результатов вычитаются поправки, равные половине известного количества импульсов генератора 7 за измерительный такт, и берется функция арктангенса полученных величин.

Таким образом, систематические погрешности измерения фазового сдвига известного устройства и предлагаемого цифрового фазового детектора соизмеримы, однако по диапазону рабочих час- тот и точности измерения (погрешности квантования) предлагаемое устройство превосходит известное.

Поскольку в прототипе частота квантования уменьшается дискретно в 4 раза в течение периода измеряемой частоты от величины 1,024 МГц, тогда погрешность квантования (погрешность преобразования интервала времени в количестве импульсов), определяемая выражением о

360 .F

Г т„ " где F — частота измеряемого сигнала; — частота квантования, подаваемая на счетчики 4 и 5, увеличивается в 4 раза. В предлагаемом устройстве частота квантования поступает на счетчики 4 и 5 непосредственно и не изменяется в течение периода измеряемой частоты, погрешность квантования минимальная .и определяется частотой Х„

Для расшйрения диапазона рабочих частот изобретения в сторону верхних частот необходимо увеличить частоту генератора 7. для обеспечения необходимой точности измерения фазового сдвига согласно (4).