Устройство для сопряжения

Иллюстрации

Показать всеРеферат

1. УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ , содержащее две группы блоков согласования интерфейсов, первые вход и выход каждого из которых соединены с соответствующими информационными входами и выходами устройства, узел настройки , подключенный входом и выходом соответственно к управляющим входу и выходу устройства, и матрицу коммутирующих элементов, каждый из которых включает регистр адреса, выходом соединенный с первым входом схемы сравнения, триггер запроса и две группы эле ментов И, вторые вход и выход i-ro (j 1,М) блока согласования интерфейсов первой rpyjwbi и вторые вход и выход -го (J 1, N) блока согласования интерфейсов второй группы соединены соответственно с первыми выходами и входами и вторыми выходами и входами коммутирующего элемента i-й строки и j-ro столбца матрицы, управляющий вход и выход которого подключены соответственно к J-M управляющим выходу и входу из i-й группы управляющих выходов и входов узла настройки, отличающееся тем, что, с целью расщирения области применения устройства, вход разрещения и управляющий выход коммутирующего элемента i-й строки (i 1, М) матрицы подключены соответственно к выходу разрешения и входу запросов i-ro блока согласования интерфейсов первой группы, а вход выборки и выход готовности кoмJмyтиpyющегоэлемента j-ro столбца, (j 1, N) матрицы соединены соответственно с выходом выборки и входом готовности j-ro блока согласования интерфейсов второй группы, причем в каждый коммутирующий элемент матрицы введены два элемента И и элемент НЕ, причем в каждом коммутирующем элементе второй вход схемы сравнения соединен с вторым информационным входом коммутирующего элемента и первыми входами элементов И первой группы, выходы которых образуют первый информационный выход коммутирующего элемента, первые входы и выходы элементов И второй группы образуют соответственно первый информационный вход и второй инфорi мационный выход коммутирующего элемента , выход схемы сравнения соединен с пер (Л вым входом первого элемента И, выход которого подключен к первому входу триггера запроса, а второй вход соединен с входом выборки коммутирующего элемента и через элемент НЕ - с вторым входом триггера запроса, выход которого подключен к управляющему выходу коммутирующего элемента и первому входу второго элемента И, второй и третий входы которого сое00 динены соответственно с управляющим ;с дом и входом разрещения коммутирующего элемента, а выход - с вторыми входами элементов И первой и второй групп и вы00 ходом готовности коммутирующего элемента . 2. Устройство по п. I, отличающееся тем, что блок настройки содержит М узлов выбора, каждый из которых состоит из N элементов И и N элементов НЕ, причем первый и второй вxoды j-гo элемента И i-ro узла выбора (i 1, М; j 1, N) соединены соответственно с i-ми входами из J-X групп управляющих и командных входов блока настройки, а выход является 1-м выходом J-X групп управляющих и

„„SU„„1118993

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

А з(д) С 06 F 3/04, 15/16

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А ВТОРСКОМ .Ф СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3583167/18-24 (22) 25.04.83 (46) 15.10.84. Бюл. № 38 (72) А. М. Заяц, С. А. Матвеев и Ю. Е. Цуканов (53) 681.327.11 (088.8) (56) 1. Авторское свидетельство СССР № 314207, кл. G 06 F 15/16, 1971.

2. Авторское. свидетельство СССР № 651335, кл. G 06 F 3/04, G 06 F !5/16, 1976 (прототип). (54) (57) l. УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ, содержащее две группы блоков согласования интерфейсов, первые вход и выход каждого из которых соединены с соответствующими информационными входами и выходами устройства, узел настройки, подключенный входом и выходом соответственно к управляющим входу и выходу устройства, и матрицу коммутирующих элементов, каждый из которых включает регистр адреса, выходом соединенный с первым входом схемы сравнения, трн-гер запроса и две группы элементов И, вторые вход и выход i-го (i = f,Ì) блока согласования интерфейсов первой группы и вторые вход и выход j-го (j. = 1, N) блока согласования интерфейсов второй группы соединены соответственно с первыми выходами и входами и вторыми выходами и входами коммутирующего элемента i-й строки и j-го столбца матрицы, управляющий вход и выход которого подключены соответственно к j-м управляющим выходу и входу из i-й группы управляющих выходов и входов узла настройки, отличающееся тем, что, с целью расширения области применения устройства, вход разрешения и управляющий выход коммутирующего элемента i-й строки (i = 1, М) матрицы подключены соответственно к выходу разрешения и входу запросов i-го блока согласования интерфейсов первой группы, а вход выборки и выход готовности коммутирующего элемента j-го столбца, (j = 1, N) матрицы соединены соответственно с выходом выборки и входом готовности j-го блока согласования интерфейсов второй группы, причем в каждый коммутирующий элемент матрицы введены два элемента И и элемент НЕ, причем в каждом коммутирующем элементе второй вход схемы сравнения соединен с вторым информационным входом коммутирующего элемента и первыми входами элементов И первой группы, выходы которых образуют первый информационный выход коммутирующего элемента, первые входы и выходы элементов И второй группы образуют соответственно первый информационный вход и второй информационный выход коммутирующего элемента, выход схемы сравнения соединен с первым входом первого элемента И, выход которого подключен к первому входу триггера запроса, а второй вход соединен с входом выборки коммутирующего элемента и через элемент НŠ— с вторым входом триггера запроса, выход которого подключен к управляющему выходу коммутирующего элемента и первому входу второго элемента И, второй и третий входы которого соединены соответственно с управляющим входом и входом разрешения коммутирующего элемента, а выход — с вторыми входами элементов И первой и второй групп и выходом готовности коммутирующего элемента.

2. Устройство по п. 1, отличающееся тем, что блок настройки содержит М узлов выбора, каждый из которых состоит из N элементов И и N элементов НЕ, причем первый и второй входы j-го элемента

И i-го узла выбора (i = 1, М; j = 1, N) соединены соответственно с i-ми входами из j-x групп управляющих и командных входов блока настройки, а выход является

i-м выходом j-x групп управляющих и

1118993 командных выходов блока настройки и соединен с входом j-го элемента НЕ i-го узла выбора, К-й вход (К = 1, N; К + j) 1

Изобретение относится к вычислительной технике и может быть использовано для построения системы обмена информацией между различными устройствами вычислительных комплексов.

Известны устройства для сопряжения, содержащие матрицу коммутирующих элементов и две группы интерфейсных блоков (1).

Недостаток известных устройств состоит в ограниченных функциональных воз а можностях.

Наиболее близким к предлагаемому является устройство для сопряжения, содержащее две группы блоков согласования интерфейсов, первые вход и выход каждого из которых соединены с соответствующими информационными входами и выходами устройства, узел настройки, подключенный командными входом и выходом соответственно к управляющим входу и выходу устройства, и матрицу коммутирую- 20

Ших элементов, причем вторые входы и выход i-го (i = 1, М) блока согласования интерфейсов первой группы и вторые вход и выход j-го (j = 1, N) блока согласования интерфейсов второй группы соединены соответственно с первыми и вторыми информационными выходами и входами коммутирующего элемента i-й строки и j-го столбца матрицы, управляющие вход и выход которого подключены соответственно к i-му управляющим выходу и входу из j-й группы управляющих выходов и входов узла настройки.

Недостатком данного устройства является ограниченная область применения, так как оно не может быть использовано для сопряжения в качестве таких внешних 35 устройств, которые могут быть заняты соб ственной обработкой.

Цель изобретения — расширение области применения устройства.

Поставленная цель достигается тем, что 40 в устройство для сопряжения, содержащее две группы блоков согласования интерфейсов, первые вход и выход каждого из которых соединены с соответствующими информационными входами и выходами устройства, узел настройки, подключенный входом и выходом соответственно к управляюшим входу и выходу устройства, и матрицу коммутируюших элементов, каждый из которых включает регистр адреса, выходом соегруппы входов j-го элемента И i-ro узла выбора соединен с выходом К-го элемента

HE i-ro узла выбора.

2 диненный с первым входом схемы сравнения, триггер запроса и две группы элементов И, вторые вход и выход i-ro (i = 1, M) блока согласования интерфейсов первой группы и вторые вход и выход j-го (j

1, N) блока согласования интерфейсов второй группы соединены соответственно с первыми выходами и входами и вторыми выходами и входами коммутирующего элемента i-й строки и j-го столбца матрицы, управляюший вход и выход которого подключены соответственно к j-м управляюшим выходу и входу из i-й группы управляющих выходов и входов узла настройки, вход разрешения и управляющий выход коммутирующего элемента i-й строки (i = 1, М) матрицы подключены соответственно к выходу разрешения и входу запросов i-го блока согласования интерфейсов первой группы, а вход выборки и выход готовности коммутирующего элемента j-го столбца (j = 1, N) матрицы соединены соответственно с выходом выборки и входом готовности j-го блока согласования интерфейсов второй группы, причем в каждый коммутируюший элемент матрицы введены два элемента И и элемент НЕ, причем в каждом коммутируюшем элементе второй вход схемы сравнения соединен с вторым информационным входом коммутирующего элемента и первыми входами элементов И первой группы, выходы которых образуют первый информационный выход коммутируюшего элемента, первые входы и выходы элементов И второй группы образуют соответственно первый информационный вход и второй информационный выход коммутирующего элемента, выход схемы сравнения соединен с первым входом первого элемента И, выход которого подключен к первому входу триггера запроса, а второй вход соединен с входом выборки коммутирующего элемента и через элемент НŠ— с вторым входом триггера запроса, выход которого подключен к управляющему выходу коммутируюшего элемента и первому входу второго элемента И, второй и третий входы которого соединены с управляющим входом и входом разрешения коммутирующего элемента, а выход — с вторыми входами элементов

И первой и второй групп и выходом готовности коммутирующего элемента.

Блок настройки содержит М узлов выбора, каждый из которых состоит из эле1118993

В ответ на сигнал запроса ВА выдает сигнал разрешения, поступающий по входам

23 одновременно на элементы И 8 всех коммутирующих элементов 2 i-й строки матрицы. При этом на выходе только этого элемента И 8 формируется сигнал разрешения, на остальных входах которого имеются единичные сигналы от триггера 9 и узла 11. Сигнал с выхода элемента И 8 открывает элементы И 5 и 6 для обмена ин формацией между заданными ВМ и ВА и разрешает выдачу в ВМ сигнала готовности с выхода элемента И 8. По сигналу цией с ВА. Сигналы на управляющих линиях выборки, запроса и разрешения остаются в течение всего времени обмена.

После окончания обмена ВМ снимает с входа 27 сигнал выборки, что приводит к формированию в выбранном коммутирующем элементе 2 сигнала сброса в нулевое состояние триггера 9 запроса.

После сброса триггера 9 в выбранном коммутирующем элементе 2 снимается сигментов И и элементов, причем р

И N -.. ов НЕ, причем первый нчлевые входы поступают «1» с выходов и второй входы )-го элемента И i-го узл» соответствующих элементов НЕ 10. На вывыоора (i =,, ) ин „„ходах элементов И 12 поддерживаются нусоответственно с i-ми входами из j-х групп левые потенциалы, так как на их первые вхоо: андных входов блока ды поступают «О» с единичных выходов настройки, а выход является 1-м выходом триггера 9. В регистрах 3 адресов нахоj-x групп управляющих и командных выхо- дятся адреса соответствующих коммутирудов блока настройки и соединен со вхо lом юп их элементов 2. На линиях Bx().:1» !9

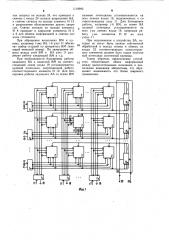

j-го элемента HE i-го узла выбора, К-й вход поддерживаются единичные сигналы. (К = 1Лч; К P j) гр ппы входов 1-го эле- Обмен информацией, например между j-й мента И i-го узла выбора соединен с выхо- 1o BM u i-м ВА, начинается с выди ги ВМ аддом К-го элемента НЕ i-го узла выбора. реса коммутируюшего элемента 2 и управНа фиг. 1 представлена блок-схема уст- ляюшего сигнала выборки, которые восройства на фиг. 2 — функциональная схе- принимаются всеми коммутирующими элема коммутируюшего элемента; на фиг. 3 — ментами 2 j-го столбца матрицы. При этом то же, узла вы ора., узла выбора.

15 код адреса сравнивается с содержимым реУстройство содержит (фиг. 1) блоки гистра 3 на схеме 4 сравнения. согласова ния интерфейсов первой и вто- При сравнении адресов в одном из комрой групп, коммутируюшие элементы 2 мат- мутируюших элементов 2 данного стол ца рицы, состоящие из (фиг. 2) регистра 3 матрицы на выходе схемы 4 сравнения усадреса, схемы сравнения, элем

4 равнения, элементов И 5 танавливается сигнал, поступающий па и 6 первой и второй групп, элементов И 7 20 вход элемента И 7, на другой вход которого и 8, триггера запросов и элемента

8, 9 запросов и элемента НЕ 10, no Bxony 27 подается сигнал выборки от узлы 1 1 выбора, состоящие из элементов ВМ. Сигнал с выхода элемента И 7 устаИ 12 и элементов HE 13 и образующих узел навливает триггер 9 в единичное состоя-! 4 настроики. и ние, сигнал с единичного выхода которого ю ий блок 1

Устройство через входы 15 и выходы 16 выдаетсЯ чеРез соответствУющий лок блоков 1 согласования интерфейсов первой и далее к 1-му ВА. Этот же сигнал постуг пп подключается к внешним абонентам пает на первый вход элемента и на групп (ВА), а через входы 17 и выходы 18 — q первый вход j-го элемента И - у. — И 12 i-го зла вычислительным машинам

1ительным машинам (ВМ). Входы 11, на остальные входы которого поступают

19 и выходы 20 являются управляющими «1» с выходов элементов НЕ, Узла входами и выходами устройства. Каждый зо ПоЯвление сигнала на выходе 1-го элеменкоммутируюший элемент 2 первыми ин- та И заблокиРУет все дРУгие элементы И 12 формационными входом 2! и выходом 22, Узла 11 пУтем noaawH Ha их входы входом 23 разрешения и управляюшим вы- вого сигнала с выхода j-го элемента НЕ 13. ходом п

24 одктючен к соответствующим С выхода j-го элемента И 12 сигнал постУпит но вход на вход элемента И 8 и выходам и входам одного из блоков 1 пер- пит но входу 29 на вход элемента и вой группы, вторыми информационными 35 подготовит его открытие. входом 25 и выходом 26, входом 27 выборки и выходом 28 готовности — к соответствующим выходам и входам одного из блоков 1 второй группы, а выходом 24 и управляюшим входом 29 — к входу и выходу соответствующих управляюших групп входов и выходу узла 14 настройки.

Регистр 3 адреса коммутирующего элемента 2 служит для хранения его постоянного адреса; схема 4 сравнения — для сравнения адреса с выхода регистра 3 адреса с 4 кодом адреса, поступающего по информационным линиям на вход 25 и выдачи сигнала в случае их совпадения.

Триггер 9 запроса предназначен для за-. „готовности ВМ начинает обмен информапоминания факта обращения ВМ и выдачи сигнала запроса на соответствуюший ВА через блок 1.

Узлы 11 выбора служат для организации очередности обмена с учетом приоритетов

ВМ относительно данного ВА в случае, когда к одному ВА обратились несколько ВМ. 55

Устройство работает следующим образом.

В исходном состоянии триггер 9 находится в нулевом состоянии, так как на его

1118993 нал запроса на выходе 24, что приводит к снятию с входа 23 сигнала разрешения ВА, к снятию сигнала на выходе элемента И 12 и разрешению обслуживания других запросов. Снятие сигнала на выходе элемента

И 8 приводит к закрытию элементов И 5 и 6 для обмена информацией и снятию сигнала готовности.

При обращении нескольких ВМ к одному, например i-ому ВА, i-й узел 11 обеспечит выбор старшей по приоритету ВМ (име ющей меньший номер). По завершении обмена между этой ВМ и ВА узел 11 разрешит работу следующей ВМ и т.д.

При необходимости блокировки работы заданного ВА и заданной ВМ на соответствующей линии входа 19 устанавливается нулевой потенциал, за прещающий работу соответствующего элемента И 12. Для блокировки работы заданного ВА со всеми ВМ нулевые потенциалы устанавливаются на всех линиях входа 19, подключенных к соответствующему узлу 11. Для блокировки работы, например j-й ВМ, со всеми ВА нулевой потенциал устанавливается на всех j-ых линиях входа 19, запрещая работу j-ых элементов И 12 во всех узлах 11.

При подключении к устройству ВА, которые не могут быть заняты собственной обработкой и всегда готовы к обмену на входы 23 соответствующих коммутирующих элементов должен быть подан постоянный потенциал логической единицы.

Таким образом, предлагаемое устройство обеспечивает обмен информацией между вычислительными машинами и различными внешними абонентами, что определяет возможность его более широкого п ри м ен ения.

1118993

ФОГ 2

Составитель В. Вертлиб

Редактор А. Ренин Техред И. Верес Корректор О. Билак

Закай 7453 35 Тираж 698 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4