Устройство для сопряжения информационно-вычислительной системы с мультиплексным последовательным каналом

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ИНФОРМАЦИОННО-ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ С МУЛЬТИПЛЕКС НЫМ ПОСЛЕДОВАТЕЛЬНЫМ КАНАЛОМ , содержащее четыре элемента И, элемент И-НЕ, элемент НЕ, входной усилитель, выходной усилитель, причем первые входы первого и второго элементов И образуют информационный вход устройства, выходы третьего и четвертого элементов И образуют информационный выход устройства, первый и второй выходы выходного усилителя образуют канальный информационный выход уст ройства, первый и второй входы входного усилителя образуют канальный информационный вход устройства, вход элемента НЕ является входом разрещения передачи устройства , первые входы третьего и четвертого элементов И-объединены и подключены к входу разрещения приема устройства. вторые входы первого и второго элементов И соединены с выходом первого элемента И-НЕ, первый и второй входы которого соединены с первыми входами первого и второго элементов И соответственно, выход элемента НЕ соединен с третьими входами первого и второго элементов И, выходы которых соединены с первым и вторым входами выходного усилителя соответственно , вторые входы третьего и четвертого элементов И соединены с первым и вторым выходами входного усилителя соответственно , отличающееся тем, что, с целью расщирения области применения, в устройство введены триггер, два элемента ИЛИ, элемент И-НЕ, причем первый нулевой вход триггера соединен с входом сброса i устройства, инверсный выход триггера является разрешающим выходом устройства, вторые входы третьего и четвертогоэлементов И соединены соответственно с первым и вторым Входами первого элемента ИЛИ, выход которого соединен с первым входом второго элемента И-НЕ, выход которого соединен с единичным входом триггера, прямой выход которого соединен с входами J и /( триггера, синхровход которого соединен с выходом второго элемента ИЛИ, первый и второй входы которого соединены с первым и вторым входами первого 00 СО элемента И-НЕ соответственно, вход разрещения передачи устройства соединен с вторым входом второго элемента И-НЕ и с вторым нулевым входом триггера. со

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК з(Я) б 06 F 3 04

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

IlO ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3604436/24-24 (22) 15.06.83 (46) 15.10.84. Бюл. № 38 (72) С. Т. Хвощ, С. В. Бочкарев, В. Т.

Лебедев, В. В: Горовой, А. В. Прибыльский, В. Е. Ашурков и Д. М. Шмаков (53) 681.3 (088.8) (56) 1. Data terminal hybrid simpl ifies

155S-bus interface. Electronic Design.

September 13. 1980, January 22. 1981.

2. Serial digital bus heads for industrial Systems. ElectroHic Design. September

13. 1980 (прототип). (54) (57) УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ИНФОРМАЦИОННО-ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ С МУЛЬТИПЛЕКС

НЫМ ПОСЛЕДОВАТЕЛЬНЫМ . КАНАЛОМ, содержащее четыре элемента И, элемент И вЂ” НЕ, элемент НЕ, входной усилитель, выходной усилитель, причем первые входы первого и второго элементов И образуют информационный вход устройства, вь ходы третьего и четвертого элементов И образуют информационный выход устройства, первый и второй выходы выходного усилителя образуют канальный информационный выход уст ройства, первый и второй входы входного усилителя образуют канальный информационный вход устройства, вход элемента НЕ является входом разрешения передачи устройства, первые входы третьего и четвертого элементов И. объединены и подключены к входу разрешения приема устройства, „„SU„„1118999 А вторые входы первого и второго элементов

И соединены с выходом первого элемента

И вЂ” НЕ, первый и второй входы которого соединены с первыми входами первого и второго элементов И соответственно, выход элемента НЕ соединен с третьими входами первого и второго элементов И, выходы которых соединены с первым и вторым входами выходного усилителя соответственно, вторые входы третьего и четвертого элементов И соединены с первым и вторым выходами входного усилителя соответственно, отличающееся тем, что, с целью расширения области применения, в устройство введены триггер, два элемента ИЛИ, элемент И вЂ” НЕ, причем первый нулевой вход триггера соединен с входом сброса устройства, инверсный выход триггера яв- Е ляется разрешающим выходом устройства, вторые входы третьего и четвертого элементов И соединены соответственно с первым и вторым входами первого элемента ИЛИ, выход которого соединен с первым входом второго элемента И вЂ” НЕ, выход которого соединен с единичным входом триггера, прямой выход которого соединен с входами

JиК триггера,,синхровход которого сое- ра динен с выходом второго элемента ИЛИ, первый и второй входы которого соединены с первым и вторым входами первого элемента И вЂ” НЕ соответственно, вход раз- QO решения передачи устройства соединен с вторым входом второго элемента И вЂ” НЕ и с вторым нулевым входом триггера. с©

1118999

Изобретение относится к цифровой вычислительной технике и может быть использовано в системах сбора и обработки информации для передачи и приема цифровых данных со скоростями обмена до 8 Мбит/с.

В связи с необходимостью повышения надежности и живучести информационных вычислительных систем, снижения стоимо- . сти их разработки и внедрения, затрат на модернизацию и модификацию, в последнее время широкое распространение получили распределенные вычислительные системы с организацией обмена по общей шине. Требование повышения достоверности обмена при снижении энергетических и весогабаритных показателей указанных систем обусловливает тенденцию к широкому использованию обмена биполярным фазоманипулированным кодом без возврата к нулю по мультиплексным каналам последовательной передачи. Существенным фактором, снижающим эффективность использования интерфейса, является недостаточная для ряда при менений допустимая длина линий связи и . возможных от нее ответвлений, что требует дополнительных затрат на реализацию ретрансляции передаваемых сообщений.

Известны устройства, содержащие усилители ввода-вывода и входную логику управления, обеспечивающие прием и выдачу цифровой информации, представленной в последовательном биполярном фазоманипулированном коде без возврата к нулю. Эти устройства предназначены для сопряжения с трансформаторной линией последовательной передачи и позволяют производить обмен информацией между средствами подсистемы и последовательным цифровым каналом (1).

Недостатками этих- устройств являются ограниченность функциональных возможностей и невозможность построения на их основе двунаправленного ретранслятора последовательного канала без дополнительных затрат оборудования, что сужает область возможных применений и обусловливает большие затраты аппаратных средств, а также дополнительные задержки передачи при организации каналов большой протяженности или с топологией связи, отличной от последовательного шлейфового соединения

Наиболее близким к изобретению по технической сущности является приемопередатчик BUS-8553, содержащий четыре элемента И, элемент И вЂ” НЕ, элемент НЕ, входной и выходной усилители, причем первый информационный вход устройства и второй информационный вход устройства соединены с первыми входами соответственно первого и второго элементов И, выходы которых подключены соответственно к первому и второму входам выходного усилителя, первые входы первого и второго элементов И соединены с первым и вторым входом первого элемента И вЂ” НЕ соответственно, выход которого - подключен к вторым входам первого и второго элементов И. Первый вход управления подключен к входу элемента НЕ, .выход которого соединен с третьими входами первого и второго эле ментов И. Первый и второй выходы входного усилителя подключены к первым входам соответственно третьего и четвертого элементов И, выходы которых являются информационными выходами устройства. Второй управляющий вход устройства соединен с вторыми входами третьего и четвертого элементов И, первый и второй выходы вы ходного усилителя являются выходами устройства в последовательный канал, первый и второй входы входного усилителя являются входами устройства из последовательного канала (2).

Недостатком известного устройства яв2О ляется невозможность построения на его основе без дополнительных затрат оборудования двунаправленного ретранслятора, что снижает функциональные возможности устройства.

Цель изобретения — расширение области применения.

Указанная цель достигается тем, что в устройство для сопряжения информационновычислительной системы с мультиплексным последовательным каналом, содержащее че30 тыре элемента И, элемент И вЂ” НЕ, элемент

НЕ, входной усилитель, выходной усилитель причем первые входы первого и второго элементов И образуют информационный вход устройства, выходы третьего и четвертого элементов И образуют информацион ный выход устройства, первый и второй выходы выходного усилителя образуют канальный информационный выход устройства, первый и второй входы зходного усилителя образуют канальный информационный вход

40 устройства, вход элемента НЕ является входом разрешения передачи устройства, первые входы третьего и четвертого элементов И объединены и подключены к входу разрешения приема устройства, вторые входы первого и второго элементов И сое4 динены с выходом первого элемента И вЂ” НЕ, первый и второй входы которого соединены с первыми входами первого и второго элементов И соответственно, выход элемента

НЕ соединен с третьими входами первого и второго элементов И, выходы которых сое динены с первым и вторым входами выходного усилителя соответственно, вторые входы третьего и четвертого элементов И соединены с первым и вторым выходами входного усилителя соответственно, введены

SS триггер, два элемента ИЛИ, элемент И вЂ” НЕ, причем первый нулевой вход триггера соединен с входом сброса устройства, инверсный выход триггера является разрешаю1118999 щим выходом устройства, вторые входы третьего и четвертого элементов И соединены соответственно с первым и вторым входами первого элемента ИЛИ, выход которого соединен с первым входом второго элемента И вЂ” HE, выход которого соединен с единичным входом триггера, прямой выход которого соединен с входами J и К триггера синхровход которого -соединен с выходом второго элемента ИЛИ, первый и второй входы которого соединены с первым и вторым входами первого элемента И вЂ” НЕ соответственно, вход разрешения передачи устройства соединен с вторым входом второго элемента И вЂ” НЕ и с вторым нулевым входом триггера.

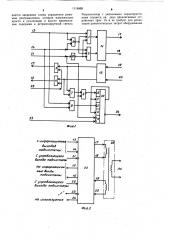

На фиг. 1 показана функциональная схема предлагаемого устройства; на фиг. 2— использование устройства в режиме приемопередатчика; на фиг. 3 — применение устройства в режиме двунаправленного ретранслятора.

Устройство содержит (фиг. 1) четыре элемента 1 — 4 И, два элемента 5 и 6 И—

НЕ, два элемента 7 и 8 ИЛИ, элемент 9

НЕ, триггер 10, выходной и входной усилители 11 и 12, информационные входы 13 и

14 и выходы 15 и 16, информационные канальные выходы 17 и 18, и входы 19 и 20, подключаемые к последовательному каналу, три входа управления «Разрешение передачи«21, «Разрешение приема» 22, «Сброс»

23 и разрешающий выход 24 «У».

Устройство сопряжения с мультиплексным последовательным каналом может работать в режиме приемопередатчика, а также использоваться для построения двунаправленного ретранслятора линии. Включение устройства в режиме приемопередатчика последовательного канала показано на фиг. 2. В этом режиме информационные входы 13 и 14 и выходы 15 и 16 устройства подключены соответственно к информационным выходам и входам обслуживаемой подсистемы, управляющие выходы которой «Разрешение передачи» и «Разрешение приема» соединены соответственно с управляющими входами 21 и 22 устройства. На управляющий вход 23 «Сброс» подается постоянный уровень логической единицы «1», а выход

24 «У» не используется. Передача информации в последовательный канал по информационным канальным выходам 17 и

18 с информационных входов устройства

13 и 14 и прием информации из последовательного канала с информационных канальных входов 19 и 20 на информационные выходы устройства 15 и 16 осуществляется при наличии соответственно нулевого по: тенциала на управляющем входе 21 «РП» и единичного потенциала на управляющем входе 22 «РПр».

Двунаправленный ретранслятор линии

/ строится на двух устройствах 25 и 25 (фиг. 3), причем первое из них подключено информа- ционными канальными входами 19 и 20 и выходами 17 и 18 к последовательному каналу 1 (ПК1), а второе — теми же своими выходами — к последовательному каналу 2 (ПК2). Информационные выходы

15 и 16 устройства 25 соединены соответственно с информационными входами 13 и 14 устройства 25 . Информационные выходы 15 и 16 устройства 25 соединены соответственно с информационными входами 13 и 14 устройства 25. Управляющий вход

21 и выход 24 устройства 25 соединены соответственно с выходом 24 и входом 21" устройства 25 . На управляющие входы 22 и 22 устройства подан постоянный уровень логической единиы «1», на управляющие входы 23 и 23 устройства 25 и 25 подан сигнал «Сброс».

20 Работа устройства в составе ретранслятора происходит следующим образом.

Направление передачи в ретрансляторе устанавливается в соответствии с моментом поступления посылки на его информацион25 ные входы из последовательного канала. С целью . исключения возможности самовозбуждения ретранслятора при включении питания и отсутствии сигналов в линиях связи, на выходах 24 и 24 устанавливаются высокие потенциалы, запрещая передачу соответственно в ПК1 и ПК2. При поступлении посылки, например, из ПК1, триггер 10 устройства 25 переключается в состояние, при котором на управляющем выходе 24 устройства 25 устанавливается низкий потенциал, разрешающий по управляющему входу «Разрешение передачи» 21 устройства 25 передачу информации в канале ПК2. Одновременно с этим блокируется вход установки в единицу триггера

10 устройства сопряжения 25 по второму

40 входу элемента 6 И вЂ” НЕ до окончания пе редачи посылки в данном направлении и затухания переходных процессов в ретрансляторе. Установка триггера 10 устройства

25 в исходное состояние осуществляется по отрицательному фронту сигнала на входе

45 синхронизации этого триггера. При этом на . управляющем выходе 24 устанавливается вы сокий потенциал. Разрешение конфликтов на уровне посылок осуществляется в са-, мом протоколе обмена последовательного канала.

Известные устройства и устройство-прототип характеризуются ограниченными функциональными возможностями, а именно невозможностью построения на их основе без дополнительных затрат оборудования двунаправленного ретранслятора, «прозрачного» по отношению к протоколу обмена в последовательном канале. В пред лагаемом устройстве этот недостаток устра1118999

Фиг.f

Фе исаолььуется няется введением схемы управления режимом рентрансляции, которая максимально проста в реализации и вносит минимальные задержки в ретранслируемый сигнал.

С инроргщццонн ыя ойдо/ аодсыюееы

C уюРаАжмщего

8жоУа nacF uem@y

На инрорнациож сФУ АоА юоАм;лечи

С улраВляющего

8ыюйг nodcucme

Ретранслятор с указанными характеристиками строится на двух предлагаемых устройствах (фиг. 3) и не требует для реализации дополнительных затрат оборудования.!

118999 . 1

Составитель С. Пестмал

Редактор С. Лнсина Техред И. Верес Корректор А. Тяско

Заказ 7453 35 Ти раж 698 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

1 l 3035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4