Преобразователь параллельного кода в последовательный

Иллюстрации

Показать всеРеферат

ПРЕОБРАЗОВАТЕЛЬ ПАРАЛЛЕЛЬНОГО КОДА В ПОСЛЕДОВАТЕЛЬНЫЙ, содержащий первый регистр сдвига, входы разрядов которого соединены с соответствующими входными шинами, первый генератор импульсов, выход которого соединен с входом сдвига первого регистра сдвига, депмфратор нуля, первый вькод которого соединен с первым входом первого генератора импульсов, и коммзп-атор, о тлйчающийс я тем, что, с целью расширения функциональных возможностей , в него введены счетчик, ;дешифратор, второй генератор импульсов и второй регистр сдвига, входы разрядов которого соединены с соответствующими входными шинами , а выходы - с входами дешифратора нуля, первый выход которого подi ключен к первому управляющему выходу преобразователя и управляющему входу дешифратора, а второй выход соединен с входом второго генератора импульсов, выход которого соединен с входом сдвига второго регистра сдвига и входом прямого счета счетчика, вход обратного счета которого соединен с выходом первого генератора импульсов, при этом : выход переполнения счетчика подключен к второму входу первого генератора импульсов и второму управляющему выходу преобразователя, а выходы разрядов счетчика соединены с (Л входами дешифратора, выходы которого соединены с управляющими входами коммутатора, информационные входы которого соединены с выходами разрядов первого регистра сдвига, кроме выхода младшего разряда, а выход коммутатора соединен с выходом преобразователя, кроме того, тановочные входы первого и второго О регистров сдвига, счетчика и дешифо кэ ратора подключены к установочному входу преобразователя.

,„ЯЦ„„1119002

СОЮЗ СОВЕТСКИХ

CNIH

РЕСПУБЛИК

Г ОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н АВТОРСКОМ,Ф СВИДЕТЕЛЬСТВУ (21) 3605972/18-,21 (22) 15.04 ° 83

: (46) 15. 10.84. Бюл. Р 38 (72) А.А. Самчинский и Б.Г. Шаров (53) 681. 325 (088. 8) (56) 1. Авторское свидетельство СССР

1Ф 217712, кл. G 06 Р 5/04, 06.02.67, 2.,Авторское свидетельство СССР Р 860056, кл. G 06 F 5/04, 06.08.79 (прототип). (54)(57)

НОГО КОДА В ПОСЛЕДОВАТЕЛЬНЫЙ, содержащий первый регистр сдвига, входы разрядов которого соединены с соответствующими входными шинами, первый генератор импульсов, выход которого соединен с входом сдвига первого регистра сдвига, дешифратор нуля первый выход которого соединен с первым входом первого генератора импульсов, и коммутатор, о тл и ч а ю шийся тем, что, с целью расширения функциональных возможностей, в него введены счетчик, дешифратор, второй генератор импульсов и второй регистр сдвига, входы разрядов которого соединены с соответствующими входными шиназш G 06 F 5 04 Н 03 К 13 256 ми, а выходы — с входами дешифратора нуля, первый выход которого под,ключен к первому управляющему выхо" ду преобразователя и управляющему входу дешифратора, а второй выход соединен с входом второго генератора импульсов, выход которого соединен с входом сдвига второго регистра сдвига.и входом прямого счета счетчика, вход обратного счета которого соединен с выходом первого генератора импульсов, при этом выход переполнения счетчика подключен к второму входу первого генератора импульсов и второму управляющему выходу преобразователя, а выходы разрядов счетчика соединены с входами дешифратора, выходы которого соединены с управляющими входами коммутатора, информационные входы которого соединены с выходами разрядов первого регистра сдвига, кроме выхода младшего разряда, а выход коммутатора соединен с выходом преобразователя, кроме того, установочные входы первого и второго регистров сдвига, счетчика и дешифратора подключены к установочному входу преобразователя.

1 l 9002 2

f0

f5

25

Цель изобретения — расширение функциональных возможностей преобразователя.

Поставленная цель достигается тем, что в преобразователь параллельного кода в последовательный, содержащий первый регистр сдвига, входы разрядов которого соединены с соответствующими входными шинами, первый генератор импульсов, выход ко50

1 1

Изобретение относится к импульсной технике и может найти примене ние в системах передачи данных по цифровым каналам с преобразованием параллельного кода в последовательный.

Известен преобразователь параллельного кода в последовательный, содержащий регистр сдвига, дешифратор нуля, выкоды которого соединены с выкодами разрядов регистра сдвига, эа исключением старшего, генератор импульсов, управляющий вход которого соединен с выходом дешифратора нуля, а выкод генератора импульсов соединен с входом сдвига, выход старшего разряда регистра сдвига соединен с информационным выходом преобразователя (1).

Недостаток данного преобразователя состоит в невозможности преобразования чисел с различными форматами (различным числом разрядов).

Наиболее близким к изобретению является преобразователь параллельного кода в последовательный, содержащий первый регистр сдвига, входы разрядов которого соединены с соответствующими входными шинами, первый генератор импульсов, выход которого соединен с входом сдвига первого регистра сдвига,. дешифратор нуля, первый выход которого соединен с первым входом первого генератора импульсов, а входы с выхода-, ми разрядов регистра сдвига, и коммутатор, выходы которого соединены с соответствующими разрядами регистра сдвига 2 3.

Недостатками известного преобра- зователя являются сложность записи в регистр сдвига кода при изменении его формата (т..е. сложность совмещения старшего разряда формата кода с .ь -ым разрядом регистра сдвига при изменении первого), необходимость предварительной информации о формате преобразуемого кода. торого соединен с входом сдвига пеРвого регистра сдвига, дешифратор нуля, первый выход которого соединен с первым входом первого генератора импульсов, и коммутатор введены счетчик, дешифратор, второй генератор импульсов и второй регистр сдвига, входы разрядов которого соединены с соответствующими входными шинами, а выходы — с входами дешифратора нуля, первый выход которого подключен к первому управляющему выходу преобразователя и управляющему входу дешифратора, а второй выход соединен с входом второго генератора импульсов, выход которого соединен с входом сдвига второго регистра сдвига и входом прямого счета счетчика, вход обратного счета которого соединен с выходом первого генератора импульсов, при этом выход переполнения счетчика подключен к второму входу первого генератора импульсов и второму управляющему выходу преобразователя, а выходы разрядов счетчика соединены с входамн дешифратора, выходы которого соединены с уцравлякппими входами коммутатора, информацИонные входы которого соединены с выходами разрядов первого регистра сдвига, кроме выхода младшего разряда, а выход коммутатора соединен с выходом преобразователя, кроме того, установочные входы первого и второго регистров сдвига, счетчика и дешифратора подключены к установочному входу преобразователя.

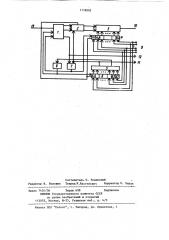

На чертеже приведена блок-схема преобразователя.

Выходы разрядов счетчика 1 соединены с входами дешифратора 2, выхо- . ды которого соединены с управляющими входами коммутатора 3.. Информационные входы последнего соединены с выходами разрядов первого регистра 4 сдвига, кроме младшего разряда.

Входы дешифратора 5 нуля соединены с выходами разрядов второго регистра 6 сдвига. Первый вход первого генератора 7 импульсов и вход .вто". рого генератора 8 импульсов соединены соответственно с первым и вторым выходами дешифратора 5 нуля.

Входы разрядов. регистров 4 и 6 сдвига соединены с соответствующими вход" ными шинами 9, выход коммутатора 3 соединен с выходом 10 преобразовате

119002

50

3 1 ля, первый выход дешифратора 5 нуля соединен с управляющим входом дешифратора 2 и первым управляющим выходом 11 преобразователя. Выход переполнения счетчика 1 соединен с вторым входом первого генератора 7 импульсов и вторым управляющим выходом 12 преобразователя. Установочный вход 13 преобразователя соединен с установочными входами счетчика 1, дешифратора 2 и регистров 4 и 6 сдвига. Выходы первого и второго гене раторов 7 и 8 импульсов соединены с входами обратного и прямого счета счетчика 1, соответственно, а также с входами сдвига первого и второго регистров 4 и 6 сдвига соответственно.

Коммутатор 3 выполнен на логических элементах И и ИЛИ и осуществляет коммутацию выхода одного из разрядов регистра 4 сдвига на выход 10 преобразователя в соответствии с кодом на выходе дешифратора 2.

Преобразователь работает следую щим образом.

Преобразуемый параллельный код вводится с входных шин 9 в разряды первого 4 и второго регистров 6 сдвига. Разряды преобразуемого кода и разряды первого и второго регистров 4 и 6 сдвига совмещаются по первому {младшему) разряду. При этом дешифратор 5 нуля снимает запрещающий потенциал с второго генератора 8 импульсов, так как содержимое разрядов второго регистра 6 сдвига не является нулевым, на первом же генераторе 7 импульсов запрещающий потенциал с первого выхода дешифратора 5 нуля присутствует.

Импульсы максимальной частоты с выхода второго генератора 8 импульсов поступают на вход сдвига второго регистра 6 сдвига и на вход прямого счета счетчика 1. Сдвиг продолжается до тех пор, пока все разряды второго регистра 6 сдвига не обнулятся. С второго выхода дешифратора 5 нуля на второй .генератор 8 импульсов подается запрещающий потенциал, а с.первого .ге5

t5

4 нератора 7 импульсов запрещающий потенциал снимается, В то же время по отрицательному перепаду напряжения на первом выходе дешифратора

5 нуля происходит дешифрация содержимого счетчика t дешифратором

2. Содержимое счетчика 1 соответствует формату преобразуемого кода, записанного в первый регистр 4 сдвига. Коммутатор 3 производит коммутацию вьмода одного из разрядов первого регистра 3 сдвига на выход !О преобразователя в соот".. ветствии с кодом на выходе дешифратора 2. С выхода первого генератора 7 импульсов тактовые импульсы поступают на вход сдвига первого регистра 4 сдвига и на вход обратного счета счетчика 1. Сдвиг преобразуемого кода в первом регистре

4 сдвига продолжается до тех пор, пока все разряды счетчика 1 не обнулятся. Зто происходит тогда, когда весь записанный в первый регистр 4 сдвига параллельный код выдается с соответствующего разряда на выход 10 преобразователя. С выхода переполнения счетчика 1 на первый генератор 7 импульсов подается запрещающий потенциал и генератор 7 прекращает продвижение кода по первому регистру 4 сдвига.

Отрицательный перепад напряжения на выходе t1 характеризует начало преобразования, а отрицательный перепад напряжения на выходе 12конец преобразования. Это дает воэможность зафиксировать начало и конец любой кодовой посылки на вьмоде 10.

После каждого преобразования необходимо подать на вход 13 импульс начальной установки.

Изобретение обеспечивает преобразование параллельного кода в последовательный без предварительной информации о формате первого, а также устраняет необходимость совмещения старшего разряда формата кода с h --ым разрядом регистра сдвига при изменении формата кода, что расширяет функциональные возможности устройства.

1119002

Составитель О. Ревинский

Редактор Н. Воловик Техред Ж.Кастелевич Корректор О. Билак

Заказ 7454/36 Тираж 698 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская йаб., д. 4/5

Филиал ППП "Патент", r Ужгород, ул. Проектная, 4