Устройство для вычисления экспоненциальных зависимостей

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ЭКСПОНЕНЦИАЛЬНЫХ ЗАВИСИМОСТЕЙ, содержащее счетчик, элемент И, элемент задержки и блок вычисления экспоненты , состоящий из первого и второго счетчиков, группы элементов И и элемента ИЛИ, причем выходы разрядов первого и второго счетчиков соединены соответственно с первыми и вторыми входами соответствующих элементов И группы, выходы которлк соединены с входами элемента ИЛИ, выход которого соединен со счетным входом второго счетчика, выход которого подключен к выходу устройства, тактовый вход устройства соединен со учетным входом счетчика, отличающее с я тем, что, с целью повышения точности, в него введены дешифратор единицы и одноразрядный блок памяти, адресный вход и вход считывания которого соединены соответственно с выходом старших разрядов счетчика и выходом дешифратора единицы, вход кЬторого соединен с выходом мпадших разрядов счетчика, выход одноразрядного (Л блока памяти через элемент задержки соединен с инверсным входом элемента И, прямой вход и выход которого соединены соответственно с тактовьм входом устройства и счетным входом первого счетчика блока вычисления экспоненты.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСОУБЛИН

„„SU,, 120318

g g G 06 F- 7/556 .Ю с=. г

М

- I

ОПИСАНИЕ ИЗОБРЕТЕНИЯ,.":." .

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ

r/d

К A8TOPCHOMV СВИДЕТЕЛЬСТВУ (21) 36046 19/24-24 (22) 14 ° 06 ° 83 (46) 23.10.84. Бюл. Р 39 (72) В.П.Данчеев и К.К.Кинкладзе (71) -Московский ордена Ленина и ордена Октябрьской Революции энергетический институт (53) 681.325(088.8) (56) 1. Мухопад Ю.Ф. Проектирование специализированных микропроцессорных вычислителей. Новосибирск, "Наука", 1981, с. 34.

2. Авторское свидетельство СССР

N - 624228, кл. С 06 F 7/556, 1977 (прототип). (54) (57) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ

ЭКСПОНЕНЦИАЛЬНЫХ ЗАВИСИМОСТЕЙ, с одержащее счетчик, элемент И, элемент задержки и блок вычисления экспоненты, состоящий из первого и второго счетчиков, группы элементов И и элемента ИЛИ, причем выходы разрядов первого и второго счетчиков соединены соответственно с первыми и вторыl ми входами соответствующих элемейтов И группы, выходы которых соединены с входами элемента ИЛИ, выход которого соединен со счетным входом второго счетчика, выход которого подключен к выходу устройства, тактовый вход устройства соединен со счетным

I входом счетчика, о т л и ч а ю щ е е с я тем, что, с целью повышения точности, в него введены дешифратор единицы и одноразрядный блок памяти, адресный вход и вход считывания которого соединены соответственно с выходом старших разрядов счетчика и выходом дешифратора единицы, вход которого соединен с выходом младших разе рядов счетчика, выход одноразрядного блока памяти через элемент задержки соединен с инверсным входом элемента И, прямой вход и выход которого соединены соответственно с тактовым входом устройства и счетным входом первого счетчика блока вычисления экспоненты.

1120318 ства.

Изобретение относится к вычислительным средствам систем управления и измерительных систем и может быть использовано как для воспроизведения функций значениями кода, заданного в дискретные моменты времени, в промежутках между этими моментами, так и в качестве блока управления специализированных устройств, занятых обработкой непрерывных процессов. 10

Известно устройство, содержащее счетчик и блок памяти, причем разряд- ные выходы счетчика соединены соот ветственно с адресными входами блока памяти, управляющий вход которого соединен с входом счетчика и подключен к тактовому входу устройства. И устройстве такт за тактом по адресному коду 6, поступающему со счетчика адреса из блока памяти, считывается код функциональной зависимости

НМ t13.

Недостатком устройства является большой объем оборудования. Так, например, при воспроизведении экспоненты ч=е + при ь,=11 и емкости микросхем 1024х1 бит схема устройства содержит около 130 корпусов.

Наиболее близким к изобретению

30 по технической сущности является устройство,. содержащее два счетчика, элемент И, триггер,,элемент задержки, схему сравнения и блок вычисления экспоненты, вход которого соединен с выходом элемента задержки и первым входом элемента И, второй вход и выход которого соединены соответственно с выходом триггера и входом первого счетчика, выход блока вычисления экспоненты соединен с первым входом схемы сравнения, выход и второй вход которой соединены соответственно с входом триггера и выходом второго счетчика, вход которого соединен с тактовым входом устройства и входом элемента задержки, причем блок вычисления экспоненты содержит два счетчика, группу элементов И и элемент ИЛИ, выходы разрядов счетчиков соединены с первыми и вторыми входами соответствующих элементов И, выходы которых соединены с входами элемента ИЛИ, выход которого соединен с входом второго счетчика, вход первого и выход вто- 55 рого счетчиков соединены соответственно с входом и выходом блока вычисления экспоненты 523.

Недостатком известного устройства является пониженная точность воспроизведения экспоненциальных зависимостей.

Цель изобретения — повышение точности устройства.

Поставленная цель достигается тем, что в устройство .для вычисления экспоненциальных зависимостей, содержащее счетчик, элемент И, элемент задержки и блок вычисления экспоненты, состоящий из первого и второго счетчиков, группы элементов И и элемента ИЛИ, причем выходы разрядов первого и второго счетчиков соединены соответственно с первыми и вторыми входами соответствующих элементов И группы, выходы которых соединены с входами элемента ИЛИ, выход которого

1соединен со счетным входом второго счетчика, выход которого подключен к выходу устройства, тактовый вход устройства соединен со счетным входом счетчика, дополнительно введены. дешифратор единицы и одноразрядный блок памяти, адресный вход и вход считывания которого соединены соответственно с выходом старших разрядов счетчика и выходом дешифратора единицы, вход которого соединен с выходом младших разрядов счетчика, выход одноразрядного блока памяти через элемент задержки соединен с инверсным входом элемента И,. прямой вход и выход которого соединены соответственно с тактовым входом устройства и счетным входом первого счетчика блока вычисления экспоненты.

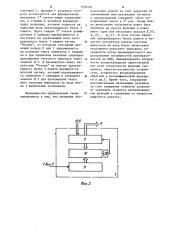

На фиг.1 представлена блок-схема предлагаемого устройства; на фиг,2 блок-схема блока вычисления экспоненты, на фиг. 3-4 — график и временная диаграмма, поясняющие работу устройУстройство для вычисления экспоненциальных зависимостей содержит блок 1 вычисления экспоненты, счетчик 2, одноразрядный блок 3 памяти, элемент ч задержки, элемент И 5; дешифратор 6 единицы и вход 7 устройства.

Блок вычисления экспоненты 1 содержит выход 8, счетчик 9, группу элементов И 10, счетчик 11 и элемент ИЛИ 12.

Устройство работает следующим образом.

Тактовые импульсы поступают на прямой вход элемента И 5 и на вход

318 ет увеличить скорость воспроизведеПреимущества предлагаемой схемы 25 ния функций в сравнении со .скоростью заключаются в том, что экономия обо- цифрового аналога. з 1120 счетчика 2, младшие К разрядов которого используются для формирования интервала 2 " тактов между коррекциями, а старшие 1л разрядов формируют адрес поправки, которая подается на адресный вход одноразрядного блока 3 . памяти. Через каждые 2 " тактов дешифратором 6 единицы вырабатывается и поступает на управляющий вход одноразрядного блока 3 памяти сигнал 10

"Чтение", по которому считанный двоичный разряд,О или 1 задерживается на половину такта элементов 4 задержки и при единичном значении запрещает прохождение тактового импульса через 15 элемент И 5. В промежутках между импульсами "Чтение" на выходе одноразрядного блока 3 памяти формируется нулевой сигнал, который подтверждается элементом 4 задержки и открывает элемент И 5 для прохождения через него тактовых импульсов на вход блока 1 вычисления экспоненты. рудoDBIIHH памяти за счет перехода от запоминания многоразрядных сигналов к одноразрядным сокращает число запоминаемых чисел в 2 раз. Схема блоК ка вычисления экспоненты может быть обобщена.на другие функции и может иметь один или несколько выходов Г„(t), Е (),,Е„(Ф.) . В этом случае введенйе одноразрядного блока памяти в качестве регулятора подачи тактовых импульсов на вход блока вычисления экспоненты позволяет уменьшить погрешность путем предварительного мо; делирования погрешностей преобразователя на ЭВМ, минимизировать погрешности воспроизведения единственной или всей совокупности функций (например, синусно-косииусное устройство, устройство воспроизведения обратной и логарифмической функцией и др.) . Кроме того, сокращение дополнительных незначащих разрядов за счет повышения точности позволяФиг. 2

» rO3i8

Ькг (,У

Жг ,7 Ю

Составитель А.Зорин

Редактор И.Николайчук Техред С.Мигунова Корректор О.Билак

Заказ 7743/36 Тираж 698 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

»3035, Москва, Ж-35, Раушская наб., д,4/5 филиал ППП "Патент", r.Ужгород, ул.Проектная, 4