Устройство для контроля микропроцессорной системы

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ МИКРОПРОЦЕССОРНОЙ СИСТЕМЫ, содержащее блок сравнения, состоящий из трех компараторов и элемента ИЛИ, блок коммутации, формирователь импульсов , причем первые и вторые информационные входы компараторов блока сравнения попарно соединены и подключены к первой, второй и третьей шинам контролируемых данных устройства соответственно, стробирующие входы компараторов блока сравнения соединены с соответствующими выходами блока коммутации, а выходы компараторов блока сравнения через элемент ИЛИ соединены с входом формирователя импульсов, выход которого соединен со йтробирующим входом блока коммутации и является выходом устройства, отличающееся тем, что, с целью повышения надежности системы путем восстановления , при одиночных сбоях, в него введен блок анализа отказов, который содержит первый, второй и третий D-триггеры запросов, первый, второй , третий и четвертый элементы ШШ, первый и второй элементы И, счетный триггер, элемент НЕ, причем первые входы с первого по третий элементов ИЛИ соединены с выходами соответствующих компараторов блока сравнения, вторые входы с первого по третий элементов ИЛИ соединены с выходом первого элемента И, а выходы - со сбросовыми входами соответствующих Б-триггеров запросов, тактовые вхоi ды которых соединены с выходом формирователя импульсов, информационные входыD-триггеров запросов соединены с шиной единичного потенциала, а выходы - с соответствующими входами }четвертого элемента ИЛИ и с соответствующими информационными входами блока коммутации, выход четвертого элемента ИЛИ соединен со счетным входом счетного триггера и первым входом второго элемента И, второй вход которого соединен с выходом элемента НЕ и вторым входом первого элемента И, а выход является выходом запроса на прерывание устройства, выход счетного триггера установлен с входом элемента НЕ, сбросовый вход счетного триггера и первый вход первого элемента И образуют соответственно вход сигнала сброса и вход сигнала подтверждения сбоя устройства.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН

as .э0 (1!) 3(59 G 06 F.11/20

ГОСУДАРС ТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ т %М,F.,, . 7 ф " 5 4 °

Н ABTOPCHONV СВИДЕТЕЛЬСТВУ (21) 3590649/24-24 (22) 01.04.83 (46) 23. 10.84. Вюл. К 39 (72) В.М.Лисенков, Г.А.Казимов, Д.В.Шалягин, В.С.Петрухин и В.П.Солдатенков (71) Московский ордена Ленина и ордена

Трудового Красного Знамени институт ин, женеров железнодорожного транспорта (53) 681.3(088.8) (56) 1 ° В.Гес и др. Применение микро. ЭВМ на подвижном составе.-"Железные дороги мира", 1982, N 10, с. 35-40.

2. Automatic Train Control System

МОООО, р. 1-19 ж, 333 И 04-14, 1980 (прототип). (54)(57) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ

МИКРОПРОЦЕССОРНОЙ СИСТЕМЫ, содержащее блок сравнения, состоящий из трех компараторов и элемента ИЛИ, блок коммутации, формирователь импульсов, причем первые и вторые информационные входы компараторов блока сравнения попарно соединены и подключены к первой, второй и третьей шинам контролируемых данных устройства соответственно, стробирующие входы компараторов блока сравнения соединены с соответствующими выходами блока коммутации, а выходы компараторов блока сравнения через элемент ИЛИ соединены с входом формирователя импульсов, выход которого соединен со стробирующим входом блока коммутации и является выходом устройства, о т л и ч а ю щ е е с я тем, что, с целью повышения надежности системы путем восстановления при одиночных сбоях, в него введен блок анализа отказов, который содержит первый, второй и третий

D-триггеры запросов, первый, второй, третий и четвертый элементы ИЛИ, первый и второй элементы И, счетный триггер, элемент НЕ, причем первые входы с первого по третий элементов

ИЛИ соединены с выходами соответствующих компараторов блока сравнения, вторые входы с первого по третий элементов ИЛИ соединены с выходом первого элемента И, а выходы — со сбросовыми входами соответствующих

Э-триггеров запросов, тактовые входы которых соединены с выходом формирователя импульсов, информационные входы 2 -триггеров запросов соединены с шиной единичного потенциала, а выходы — с соответствующими входами четвертого элемента ИЛИ и с соответствующими информационными входами блока коммутации, выход четвертого элемента ИЛИ соединен со счетным входом счетного триггера и первым входом второго элемента И, второй вход которого соединен с выходом элемента НЕ и вторым входом первого элемен. та И, а выход является выходом запроса на прерывание устройства, выход счетного триггера установлен с входом элемента НЕ, сбросовый вход счетного триггера и первый вход первого элемента И образуют соответственно вход сигнала сброса и вход сигнала подтверждения сбоя устройства.

t 1 i 203

Изобретение относится к системам железнодорожной автоматики, B частности к устройствам контроля микропроцессорных систем (МПС) управления транспортными средствами.

Известно устройство контроля . (ИПС) управления, содержащее два канала, в которых контролируемые па" раметры логически связаны схемой самоконтроля. Выходы каналов через усилители управляют контрольными контакторами, удерживая их во вклю- " ченном положении до тех пор, пока не произойдет повреждение (1 $.

Наиболее близким к изобретению по технической сущности является устройство для контроля системы автоматической локомотивной сигнализацни, содержащее кампараторно-селектор" ный блок, информационные входы которого соединены с шинами данных, а один из выходов — с входом синхронизации формирователя управляющих импульсов, блок коммутации и блок прерывания программы (2 j.

Однако известное устройство одинаково реагирует как на кратковре" менные сбои, так и на устойчивые отказы, отключая при этом систему от

/ объекта управления или осуществляя рекомендацию системы. Это приводит к снижению надежности системы.

Цель изобретения — повышение надежности системы путем восстановления при одиночных сбоях.

Поставленная цель достигается тем, что в устройство для контроля

МПС, содержащее блок сравнения, состоящий из трех компараторов и элемента ИЛИ, блок коммутации, формирователь импульсов, причем первые и вторые информационные входы компараторов блока сравнения попарно сое" динены и подключены к первой, второй и третьей шинам контролируемых данных устройства соответственно, стробируйицие входы компараторов блока (сравнения соединены с соответству кицими выходами блока коммутации, а выходы компараторов блока сравнения через элемент ИЛИ соединены с вхрдом формирователя импульсов, выход которого соединЕн со стробирующим вх/эдом блока коммутации и является выходом устройства, введен блок 55 анализа отказов, который содержит первый, второй и третий З -триггеры запросов, первый, второй, третий и четвертый элементы ИЛИ, первый и

Зб 2 второй элементы И, счетный триггер, элемент НЕ, причем первые входы с первого по третий элементов ИЛИ соединены с выходами соответствующих компараторов блока сравнения, вторые входы с первого по третий элементов

ИЛИ соединены с выходом первого элемента И, а выходы — со обросовыми входами соответствующих J3 -триггеров запросов, тактовые входы которых соединены с выходом формирователя импульсов, информационные входы

9-триггеров запросов соединены с шиной единичного потенциала, а выходы — с соответствующими входами четвертого элемента ИЛИ и с соответствующими информационными входами блока коммутации, выход четвертого элемента ИЛИ соединен со счетным входом счетного триггера и первым вхо„цом второго элемента И, второй вход которого соединен с выходом элемента НЕ и вторым входом первого элемента И, а выход является выходом запроса на прерывание устройства, выход счетного триггера соединен с входом элемента НЕ, сбросовый вход счетного триггера и первый вход первого элемента И образуют соответственно .вход сигнала сброса и вход сигнала подтверждения сбоя устройства.

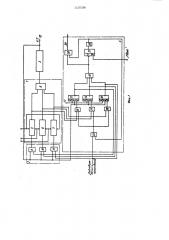

На фиг. 1 приведена функциональная схема устройства; на фиг. 2— алгоритм обработки отказов, Устройство содержит блок 1 сравнения, блок 2 коммутации, формирователь 3 импульсов, блок 4 анализа заявок, компараторы 5 - 7, элемент

ИЛИ 8, элементы И 9-11, выход 12, 3-триггеры 13-15 запросов, элементы

ИЛИ 16-19, элемент И 20, счетный триггер 21, элемент НЕ 22, элемент

И 23, выход 24 запроса на прерывание.

В состав блока 1 входят три компаратора 5-7, выходы которых через эле/ мент ИЛИ 8 соединены с входом синхронизации формирователя 3 управляющих импульсов. В состав блока 2 ком мутации входят три элемента И 9-1 1 первые входы которых объединены с входом блока анализа отказов и подключены к выходу формирователя 3 управляющих импульсов.

В состав блока 4 анализа заявок

1. входят также три Ь-триггера 13-15 запроса прерывания, счетные входы кото" рых соединены с выходом, информацион« ные входы через элементы ИЛИ 16-18с выходами компараторов 5-7 блока 1,.

11203

35 а выходы соответственно с вторыми входами элементов И 11-13 блока 4 и с входами элемента ИЛИ 19. Выход элемента ИЛИ 19 подключен к первому элементу И 20 и к счетному входу счетчика

21 сбоев,на информационный вход которого подается сигнал "Сброс" от микроЭВМ. Выход счетного триггера 21 через элемент НЕ 22 подключен к второму входу элемента И 20 и к первому входу элемента И 23, на другой вход которого от микроЭВМ подается сигнал "Подтверждение прерывания", а выход подключен к объединенным вторым входам элементов ИЛИ 16-18.

Устройство контроля работает следующим образом.

Сигналы с шин данных от трех микроЭВМ системы поступают на компараторы: 5"7, где попарно сравниваются. Для о фиксации состояния шин в определенный момент времени формирователь 3 управляющих импульсов вырабатывает стробирующий импульс опроса, подаваемый на компараторы 5-7 через элементы И 9-11 блока 2 и на счетные входы Р -триггеров 13-15.

Если нет ошибок в работе МПС, импульс опроса проходит через компараторы 5-7 и элемент ИЛИ 8 на вход синхронизации формирователя 3, а на выходах 3 -триггеров 13-15 блока 4 отсутствует сигнал "Запрос прерыва- ° ния", В случае возникновения ошибки в одной из микроЭВМ импульс опроса отсутствует на выходе соответствующего компаратора, соответствующий

Э-триггер сформирует сигнал "Запрос прерывания", который через элемент

ИЛИ 19 поступает на счетный вход триггера 21, в который записывается

"+1", и,через элемент И,на другой вход которого через элемент НЕ 22 поступает сигнал с выхода триггера— в блок прерывания программы. МПС вос45

36 4 принимает это прерывание и переходит на подпрограмму обработки сбоев. Для обеспечения такой обработки вся программа микроЭВМ разбивается на отдельные участки. В канале каждого участка программы, формируется контрольная точка, которая представляет собой записанные в определенной зоне ОЗУ исходные данные и информацию о состоянии микроЭВМ на момент ее формирования. Как только поступает сигнал "Запрос прерывания" от устройства контроля MIIC все три микроЭВМ восстанавливают свое состо1яние, выдает сигнал "Подтверждение прерывания" и повторяет сбившийся участок программы.

Если во время прохождения повторно сбившегося участка ошибка не обнаружена, то сбрасывается триггер 21 и устройство контроля переходит в первоначальное состояние. Если же ошибка обнаружена повторно, в триггер 21 записывается вторая "1" и сигнал с выхода триггера 21 блокирует сброс состояния соответствующего

3-триггера прерывания, который в свою очередь записывает соответствующие элементы И блока 2 коммутации.

Если же после реконфигурации обнаруживается ошибка, на выходе компараторно-селекторного блока отсутствует сигнал, синхронизирующий работу формирователя управляющих импульсов, и происходит останов системы.

Таким образом, предлагаемое устройство позволяет повысить точность контроля МПС за счет обработки сбоев.

Реконфигурации системы в случае сбоев не происходит, следовательно не надо при каждом сбое проверять локализованную микроЭВМ, отыскивая неисправность, как в известном, тем более, что интенсивность сбоев, как указывалось, на 2-3 порядка выше, чем интенсивность устойчивых отказов.

1120336! 120336