Функциональный преобразователь

Иллюстрации

Показать всеРеферат

ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ , содержащий блок памяти и счетчик адреса, счетный вход которого соединен с тактовым входом преобразователя и тактовым входом блока памяти , адресный вход которого подключен к выходу счетчика адр1еса, отличающийся тем, что, с целью сокращения аппаратурных затрат за счет использования одноразрядного блока памяти,, он содержит реверсивный счетчик функции, реверсивный двоичный умножитель, триггер режима , два элемента И и элемент ИЛИ, причем блок памяти вьшолнен одноразрядным , выход блока памяти подключен к первому входу первого элемента И, второй вход и выход которого соединены соответственно с инверсным выходом триггера режима и первым входом элемента ИЛИ, выход которого соединен со счетным входом реверсивного счетчика функции, выход которого соединен с выходом преобразователя и управлякнцим входом реверсивного двоичного умножителя, тактовый вход и выход которого соединены соответственно с тактовым входом преобразователя и первым входом второго элемента И, выход которого соединен с вторым входом элемента ИЛИ и информа191онным входом блока памяти, вход задания режима записи - считывания которого соединен с прямым выходом триггера режима, вторым входом второго элемента И и входами управления -реверсом реверсивного счетчика функции, реверсивного двоичного умножителя и счетчика адреса, счетный вход триггера режима соеди нен с входом задания режима преобразователя .

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН

09) (И) А зев С, 06 F 15/31

ЮСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОЧНРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCHOMY СВИДЕТЕЛЬСТВУ (21) 3604618/24-24 (22) 14.06.83 (46) 23.10.84. Бюл. У 39 (72) В.П.Данчеев и К.К.Кинкладэе (71) Иосковский ордена Ленина и ордена Октябрьской Революции энергетический институт (53) 681.325(088. 8) (56) 1. Данчеев В.П. Цифро-частотные вычислительные устройства. М., "Энергия™, 1976, с. 57.

2. Мухопад Ю.Ф. Проектирование специализированных микропроцессорных вычислителей. "Наука", 1981, с. 34 (прототип). (54)(57) ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ, содержащий блок памяти и счетчик адреса, счетный вход которого соединен с тактовым входом преобразо» вателя и тактовым входом блока памяти, адресный вход которого подключен к выходу счетчика адреса, о т— л и ч а ю шийся тем, что, с целью сокращения аппаратурных затрат за счет использования одноразрядного блока памяти,, он содержит реверсивный счетчик функции, реверсивный двоичный умножитель, триггер режима, два элемента И и элемент ИЛИ, причем блок памяти выполнен одноразрядным, выход блока памяти подключен к первому входу первого элемента

И, второй вход и выход которого соединены соответственно с инверсным выходом триггера режима и первым входом элемента HJIH, выход которого соединен со счетным входом реверсивного счетчика функции, выход которого соединен с выходом преобразователя и управляющим входом реверсивного двоичного умножителя, тактовый вход и выход которого соединены соответственно с тактовым входом преобразователя и первым входом второго Я элемента И, выход которого соединен с вторым входом элемента ИЛИ и информационным входом блока памяти, вход задания режима записи — считывания которого соединен с прямым вьиодом триггера режима, вторым входом второго элемента И и входами управления реверсом реверсивного счетчика функции, реверсивного двоичного умножителя и счетчика адреса, („) счетный вход триггера режима соединен с входом задания режима преобразователя.

1 1 1203

Изобретение относится к гибридным ! вычислительным средствам систем управления и измерительных систем и может быть использовано как для воспроизведения функций значения кода, заданного в дискретные моменты времени, в промежутках между этими моментами, так и в качестве блока управления специализированных устройств при обработке непрерывных процессов.

Известен цифро-частотный функциональный генератор, содержащий счетчик, двоичный умножитель, линию обратной связи, по которой подается частотная зависимость единиц и нулей 1 3.

Недостатком такого устройства является то, что при реверсе воспроизводимой зависимости возникают ситуации, названные нереверсируемыми: при обратном ходе траектория значений функций не совпадает с прямой траекторией.

Наиболее близким к изобретению является устройство, содержащее счетчик и блок памяти, причем вход счетчика и управляющий вход блока памяти объединены и подключены к тактовому входу устройства, разрядные выходы счетчика соединены соответственно с адресными входами блока памяти. КажЗО дое слово, записанное в блоке памяти с требуемой разрядностью h, такт за тактом по адресному коду t считывается из блока памяти как в прямом, так и в обратном направлениях(2) 5

Недостатком известного устройства является большой объем оборудования.

Так, например, при воспроизведении экспоненты при о = 11 (где и — разрядность числа) и емкости микросхем >

1С24 х 1 бит схема устройства содержит около 190 корпусов.

Цель изобретения — сокращение аппаратурных затрат за счет использования одноразрядного блока памяти.

Поставленная цель достигается тем, что функциональный преобразователь, содержащий блок памяти и счетчик адреса, счетный вход которого соединен с тактовым входом преобразователя и тактовым входом блока памяти, адресный вход которого подключен к выходу счетчика адреса, содержит реверсивный счетчик функции, реверсивный двоичный умножитель, триг- 55

rep режима, два элемента И и элемент

ИЛИ, причем блок памяти выполнен одноразрядным, выход блока памяти сщ43 2 ключен к первому входу первого элемента И, второй вход и выход которого соединены соответственно с инверсным выходом триггера режима и первым входом элемента ИЛИ, выход которого соединен со счетным входом реверсивного счетчика функции, выход которого соединен с выходом преобразователя и управляющим входом реверсивного двоичного умножителя, тактовый вход и выход которого соединены соответственно с тактовым входом преобразователя и первым входом второго элемента И, выход которого соединен с вторым входом элемента ИЛИ и информационным входом блока памяти, вход задания режима записи — считывания которого соединен с прямым выходом триггера режима, вторым входом второго элемента И и входами управления реверсом реверсивного счетчика функции, реверсивного двоичного умножителя и счетчика адреса, счетный вход триггера режима соединен с входом задания режима преобразователя.

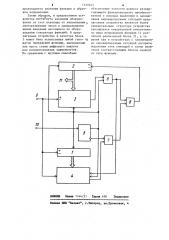

На чертеже представлена блок-схема преобразователя.

Функциональный преобразователь содержит счетчик 1 адреса, реверсивный счетчик 2 функции, .реверсивный двоичный умножитель 3, одноразрядный блок 4 памяти, триггер 5 режима, элементы И 6 и 7, элемент ИЛИ 8, тактовьй вход 9, вход 10 задания режима и выход 11.

Устройство работает следующим образом.

В каждом такте в случае прямой развертки одноразрядное значение приращения по обратной связи поступает с выхода реверсивного двоичного умножителя 3 через элемент И б, который открыт триггером 5 режима, поступает на информационный вход блока 4 памяти, а через элемент

ИЛИ 8 подается на сложение в счетчик 2, в котором формируется выходная функция ° При реверсе (обратном ходе) триггер 5 режима закрывает эле- мент И б, октрывает элемент И 7, переключает блок 4 памяти на считывание и реверсирует двоичный умножитель

3 и счетчики 1 и 2. В этом случае приращение (нуль или единица) передается из блока памяти через элемент

И 7 и элемент ИЛИ 8 на вычитание в счетчике 2 функции, в котором восз 11203 производятся значения функции в обратном направлении.

Таким образом, в предлагаемом устройстве достигнута экономия оборудоВания за счет перехода От запоминания многоразрядных чисел к одноразрядным ценой введения несложного по оборудованию генератора функций. В предлагаемом устройстве в качестве блока

3 может быть использован любой гене- 10, ратор приращений функции, выполненный как часть схемы цифрового аналога для воспроизведения зависимостей.

По сравнению с другими способами

43 обеспечения точности реверса развертывающего функционального преобразователя с помощью вьделения и запоминания нереверспруемых ситуаций предлагаемое устройство является более универсальным: структура устройства оказывается инвариантной относительно вида непрерывной функции (с различной реализацией блока 3), в то время как в устройствах с запоминанием нереверсируемых ситуаций алгоритм вьделения этих ситуаций и схема включения соответствующих блоков зависят от типа функции.

ВНИИПК Заказ 7744/37 Тирам 698 Подписное

Филиал ППП "Патент", г.Умгород, ул.Проектная, 4