Анализатор спектра

Иллюстрации

Показать всеРеферат

АНАЛИЗАТОР СПЕКТРА, содержащий первый регистр сдвига, первый, второй, третий и четвертый сумматоры , отличающий ся тем, что, с целью расширения области применения , в него введемз первый и второй блоки памяти, элемент НЕ, счетчик, первый, второй, третий и четвертыймультиппексоры, первый и второй регистры, второй и третий регистры сдвига, информационные выходы которых подключены к первым входам соответственно первого и второго сумматоров, выходы которых подключены к ин формационным входам соответственно второго и третьего регистров сдвига и являются соответственно первым и вторым информационными выходами анализатора, информационный выход первого регистра сдвига подключен к первым входам первого и второго мультиплексоров, выходы которых подключены к первым входам соответственно третьего и четвертого сумматоров, вЪтходы которых подключены к вторым входам соответственно первого и второго сумматоров и соединены с информационными входаьм соответственно первого и второго регистров, информационные выходы которых подключены к первым входа соответственно третьего и четвертого мультиплексоров, выходы которых подключены к вторым входам соответственно третьего и четвертого сумматоров, выхода разрядов первой группы первого и второго блоков памяти подключены к второму входу первого мультиплексора , выходы разрядов второй группы первого и второго блоков памяти СО подключены к второму входу второго fyльтиплeкcopa, выходы разрядов третьей группы первого блока памяти подключены к адресному входу второго блока памяти, информационный вход которого соединен с информационным входом первого регистра сдвига и является информационным входом . анализатора, выход младшего разряда счетчика подключен к входу элемента НЕ, второму входу четвертого мультиплексора и знаковому входу второго блока памяти, выход элемента НЕ подключен к второму входу третьего мультиплексора и входу знакового разряда первого регистра сдвига.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУЬЛИН

„SU„„1120348

А 1 11 G 06 F.15/332!

В;- Р" ()1 ."1 н g r

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCHOVIV СВИДЕТЕЛЬСТВУ с : :: 1 (21) 3613764/24-24 (22) 04.07.83 (46) 23.10.84. Бюл. 11 - 39 (72) А.В.Белинский (53) 681. 32 (088. 8) (56) 1. Авторское свидетельство СССР

II 924716, кл. G 06 F 15/332, 1980.

2. Авторское свидетельство СССР

Ф 484523,. кл. G 06 F 15/332, 1973 (прототип) . (54) (5 7) АНАЛИЗАТОР .СПЕКТРА, содержащий первый регистр сдвига, первый, второй, третий и четвертый сумматоры, отличающийся тем, что, с целью расширения области применения, в него введены первый и второй блоки памяти, элемент НЕ, счетчик, первый, второй, третий и четвертый. мультиплексоры, первый и второй регистры, второй и третий регистры сдвига, информационные выходы которых подключены к первым входам соответственно первого и второго сумматоров, выходы которых подключены к информационным входам соответственно второго и третьего регистров сдвига и являются соответственно первым и вторым информационными выходами анализатора, информационный выход первого регистра сдвига подключен к первым входам первого и второго мультиплексоров„ выходы которых подключены к первым входам соответственно третьего и чет\ вертого сумматоров, вЪ1ходы которых подключены к вторым входам соответственно первого и второго сумматоров и соединены с информационными входами соответственно первого и второго регистров, информационные выходы которых подключены к первым входам соответственно третьего и четвертого мультиплексоров, выходы которых подключены к вторым входам соответственно третьего и четвертого сумматоров, выходы разрядов первой группы первого и вто" рого блоков памяти подключены к второму входу первого мультиплексора, выходы разрядов второй груп- I пы первого и второго блоков памяти подключены к второму входу второго мультиплексора, выходы разрядов третьей группы первого блока памяти подключены к адресному входу второго блока памяти, информационный вход которого соединен с информа— ционным входом первого регистра сдви-

ra и является информационным входом . анализатора, выход младшего разряда счетчика подключен к входу элемента НЕ, второму входу четвертого мультиплексора и знаковому входу второго блока памяти, выход элемента HE подключен к второму входу третьего мультиплексора и входу знакового разряда первого регистра сдвига.

348

1 1120

Изобретение относится к специальным средствам вычислительной техники, предназначенным для спектральной обработки цифровых сигналов, аппроксимируемых прямоугольными сопряжениями по локальным экстремумам, дифференциальным порогам, клиппированных сигналов, и может использоваться при решении задач распознавания образцов, идентификации, диагностики.

Известно устройство для выполнения преобразования Хаара с разложением исходного сигнала по бинарному базису, содержащее N групп блоков, каждый из которых состоит из трех сумматоров-вычитателей и трех регист-. ров сдвига f1 $.

Недостатком устройства является малое быстродействие при реализации в скользящем режиме обработки цифровой последовательности входного сигналаа.

Наиболее близким к изобретению но технической сущности является устройство, содержащее четырнадцать ключевых элементов, преобразователь аналог-цифра, девять регистров сдвига, сумматор-интегратор, четырнадцать сумматоров и блок управления, выходы которого соединены с управляющими входами соответствующих блоков. Устройство предназначено для формирования коэффициентов разложения Хаара на скользящем интервале (2 ).

Недостатками известного уст— ройства являются большой объем аппаратуры, малое быстр одей ствие, отсутствие возможности на базе устройства для формирования коэффициентов 4О

Хаара получить набор коэффициентов полного разложения по бинарному базису Фурье, коэффициенты определяются только по одной базисной составляющей.

Цель изобретения — расширение области применения.

Поставленная цель достигается тем, что в анализатор спектра, содержащий первый регистр сдвига, пер- 5О вый, второй, третий и четвертый сумматоры, введены первый и второй блоки памяти, элемент НЕ, счетчик, первый, второй, третий и четвертый мультиплексоры, первый и второй ре, — 55 гистры, второй и третий регистры сдвига, информационные выходы которых подключены к первым входам соответственно первого и второго сумматоров, выходы которых подключены к информационным входам соответственно второго и третьего регистров сдвига и являются сооответственно первым и вторым информационными выходами анализатора, информационный выход первого регистра сдвига подключен к первым входам первого и второго мультиплексоров, выходы которых подключены к первым входам соответственно третьего и четвертого сумматоров, выходы которых подключены к вторым входам соответственно первого и второго сумматоров и соединены с информационными входами соответственно первого и второго регистров, информационные выходы которых подключены к первым входам соответственно третьего и четвертого мультиплексоров, выходы которых подключены к вторым входам соответственно третьего и четвертого сумматоров, выходы разрядов первой группы первого и второго блоков памяти подключены к второму входу первого мультиплексора, выходы разрядов второй группы первого и второго блоков памяти подключены к второму входу второго мультиплексора, выходы разрядов третьей группы первого блока памяти подключены к адресному входу второго блока памяти, информационный вход которого соединен с информационным входом первого регистра сдвига и является инфор— мационным входом анализатора, выход младшего разряда счетчика подключен к входу элемента НЕ, второму входу четвертого мультиплексора и знаковому входу второго блока памяти, выход элемента НЕ подключен к второму входу третьего мультиплек— сора и входу знакового разряда первого регистра сдвига.

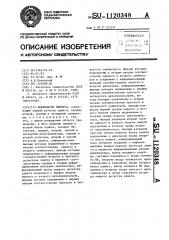

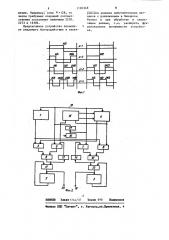

На фиг. 1 приведены графики четырех базисных бинарных функций: синусной и косинусной; на фиг.2 блок-схема предлагаемого устройства для вычисления спектра в бинарном базисе при скользящем режиме обработки ограниченной выборки цифрового сигнала в виде действительной последовательности.

Устройство содержит регистры

1 — 3 сдвига, блок 4 оперативной памяти, мультиплексоры 5 — 8, сумматоры 9 — 12, регистры 13 и 14, блок 15 памяти, счетчик 16, эле—

0348 4

Вычисление величин д f u производится с помощью сумматоров 9 и 10. Результаты заносятся в регистры 13 и 14, после чего организуются циклические процедуры накапли 5 вания значений суммирования Л Е и с элементами исходной выборки

f(k), подающимися в требуемом порядке с соответствующими знаками. Для этого в блоке 4 оперативной памяти!

35 !

М =(- 1P f (Ni-Ю (О!

3 112 мент НЕ 17. По информационному вход ду 18 в устройство поступает исходная информация, а результаты вычислений подаются во внешний процессор по информационным выходам 19 и 20.

Устройство работает следующим образом.

После обнуления регистров 1 — 3 сдвига блока 4 оперативной памяти, регистров 13 и 14 на вход 18 устройства поступает дискретное значение

E(V) в виде f (N) . При этом по двум параллельным каналам в устройстве реализуются два вида операции свертки по бинарному синусному базису р Из/р-1

F„(p) =. Е (- f (Ц

5=1 k= N(s- !)/р и по бинарному косинусному базису (И (Zs <1>

5+ (1,)+ () )

5=2 )с=N(as-ЗЦХр к=О й-1

+(ц .> f (!!

k-й(2р-1)! 2р

Расчет последующих значении (p) и I () производится !!+ и+1 в устройстве на базе рекурентных соотношений

Р-4

F„+„(pl= F„(p)+6f+2Z (- } f (Ns/р), 61=(-!l f (й1- f (o), где

Р

FÄ Ä (p)= „(p)+ f"+2 Å (-!) f/ (2s-1!!2р) Одновременно с поступлением значений f (N) в блоки 1 и 4 они подаются через входы мультиплексоров 6 и 7 на входы сумматоров 9 и 10

В этом же такте с выхода регистра сдвига через входы мультиплексоров 5 и 8 на входы сумматоров 9 и 10 подаются значения 1(О!.

Посредством двухразрядного счетчика 16 и элемента НЕ 17, на вход которого подается значение первого разряда из счетчика 16, формируются соответствующе знаковые разряды величины f(N) для вычисле- ний по синусному и косинусному базисам соответственно. организована пошаговая сдвиговая параллельная запись значений обрабатываемой выборки размером N, а в блоке 15 памяти (постоянного типа j записи хранятся целые значения констант 1NS/Р C и )И(28-1)/2Р(и их знаковые разряды. Число этих констант определяется суммой арифметической прогрессии. Данные константы, поступающие с выходов блока 15 памяти на входы блока 4 оперативной памяти, определяют адреса считывания информации о f (k) из блока 4, которая вместе с коммути-. руемыми знаковыми разрядами с вы— ходов блока 15 памяти подается через входы мультиплексоров 5 и 8 на входы сумматоров 9 и 10. Одновременно на другие входы сумматоров 9 и 10 через входы мультиплексоров 6 и 7 подаются значения из регистров 13 и 14, в которых в последующем накапливаются промежуточные результаты. После завершения р-1 цикла для левой и р циклов. для правой .частей устройства результаты с сумматоров 9 и 10 подаются на входы сумматоров 11 и 2.

Цикл р для левой части реализуется путем суммирования полученного результата с нулевыми значениями.

На другие входы сумматоров 1 и 12 с из регистров 2 и 3 сдвига подаются значения Г „(р) и F „(р), а результаты сложения Г„„(р) и Р", (р) одновременно записываются в регистры 2 и 3 сдвига и подаются во внешний процессор, являясь выходными результатами вычислений устройства.

Переменная р в устройстве изменяется в пределах р =1, N /2-1. Общее количество операций алгебраического сложения для левой части устройства составляет 20+1 +. (N"2) (N-4)/8, а для правой части 2N+I + N(N-2)/8.

Прямая реализация свертки с бинарным базисом при переходе от предыдущей и последующей выборке требует N операций алгебраического сло5 1120348 жения. Например; если М =128, то числа требуемых операций соответственно составляют величины 22!О, 2273 и )6384.

Предлагаемое устройство позволя- ет уведичить быстродействие в chemральном анализе действительных сигнапов с разложением в .бинарном базисе и при обработке в скользящем режиме, т.е. расширить фун5 .кциональные воэможности устройства, ВНИИПИ Заказ 7 744/37 Тираж 698 Подшсное

Филкал ППП "Патеит", г. Ужгород,ул.Проектная, 4