Способ форсированного запирания транзисторов

Иллюстрации

Показать всеРеферат

СПОСОБ ФОРСИРОВАННОГО ЗАПИРАНИЯ ТРАНЗИСТОРОВ, заключающийся в том, что подают запирающее напряжение на переход эмиттер-база транзистора, отличающийс я тем, что, с целью повышения КПД, одновременно с подачей запирающего напряжения формируют импульс тока, который суммируют с током нагрузки транзистора, причем величину импульса тока выбирают такой, чтобы суммарный ток через переход эмиттер-коллектор прёвьппал 10% от величины максимального тока нагрузки данного транзистора. и: kn

СОЮЗ COBETCHHX

ШИ4%Ф

РЕСПУБЛИК

g g Н 02 М 1/08

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К Лвто омМ свкДКтЕЛьСтвМ (21) 3440683/24-07 (22) 21.05.82 (Q6) 23.10.84. Бюл . У 39 (72) М.А. Житков, А.Ф. Петров и В.Н. Пичугин (71) Специальное конструкторско-технологическое бюро геофизической техники (53) 621.316.727(088.8) (56) 1. Авторское свидетельство СССР

8 698104, кл. Н 02 М 1/08, 1978.

2. Драбович Ю.И. и др. Способ управления транзисторами в высокочастотных инверторах. — В сб.: Проблемы преобразовательной техники. ч. 1, Киев, 1979.,SUÄÄ 1120462 А (54) (57 ) СПОСОБ ФОРСИРОВАННОГО

ЗАПИРАНИЯ ТРАНЗИСТОРОВ, заключающийся в том, что подают запирающее напряжение на переход эмиттер-база транзистора, о т л и ч а ю щ и йс я тем, что, с целью повьппения

КПД, одновременно с подачей запирающего напряжения формируют импульс тока, который суммируют с током нагрузки транзистора, причем величину импульса тока выбирают такой, чтобы суммарный ток через переход эмиттер-коллектор превьппал 10Х от величины максимального тока нагрузки данного транзистора.

1120462

f

Изобретение относится к электротехнике и,может быть использовано в источниках вторичного электропитания с бестрансформаторным входом.

Известен способ форсированного запирания транзисторов, состоящий в том, что одновременно с подачей запирающего напряжения на переход база-эмиттер формируют запирающее напряжение на переходе база-,коллектор (1) .

Однако такой способ позволяет снизить время выключения не более чем на 10-202, так как действие источника в цепи база-коллектор снижает эффективность действия источника запирающего напряжения в цепи база-эмитт ер .

Наиболее близким к изобретению по технической сущности является 20 способ форсированного запирания транзисторов, заключающийся в том, что подают запирающее напряжение на переход эмиттер-база транзистора (2). гя

Недостатком способа является то, что при частотах в десятки килогерц, время, в течение которого транзистор находится на границе активной области, составляет значительную часть рабочего периода. При этом очень сильно возрастают статические потери в транзисторе.

Целью изобретения является повышение КПД.

Поставленная цель достигается тем, что согласно способу форсированно.го запирания транзисторов, заключающемуся в том, что подают запирающее напряжение на переход эмиттербаэа, одновременно с подачей запирающего напряжения формиру-. ют импульс тока, который суммируют с током нагрузки транзистора, причем величину импульса тока выбирают такой, чтобы суммарный ток через пе-. реход эмиттер-коллектор превышал 10Х от величины максимального тока нагрузки данного транзистора.

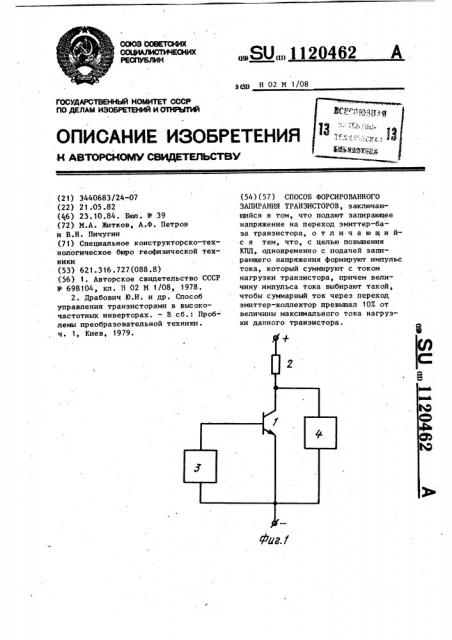

На фиг. 1 приведена блок-схема устройства, реализующего данный способ, на фиг. 2 — диаграмма таков и напряжений в различных точках схемы.

Устройство реализации способа форсированного запирания транзистора 1 содержит включенные в цепь коллектор-эмиттер транзистора 1 и нагрузку 2, блок 3 управления, подключенный к базо-эмиттерному переходу транзистора 1, и формирователь

4 тока, подключенный параллельно переходу эмиттер-коллектор транзистора 1. !

Устройство реализации работает следующим образом.

В насыщенном состоянии к переходу база-эмиттер приложено отпирающее напряжение и через него течет ток I<, определяемый сопротивлением нагрузки 2 (фиг. 2а, б). При смене полярности управляющего напряжения в базовой области транзистора 1 начинается процесс рассасывания неосновных носителей, в течение которого транзистор 1 продолжает оставаться открытым (фиг. 2 r). Одновременно со сменой полярности управляющего напряжения формирователь 4 тока формирует импульс тока I д (фиг. 2 в), величина которого не зависит .от тока нагрузки I> и может выбираться в зависимости от типа транзистора 1. В результате этого снижается коэффициент насыщения тока базы при выключении, происходит эффективное рассасывание неосновных носителей и форсированное запирание транзистора 1. При этом действие формирователя и тока не оказывает отрицательного влияния на процессы в цепи база-эмиттер.

Таким образом, при сравнительно небольшой дополнительной подгрузке транзистора (порядка 10X) удается в

1,5-2 раза уменьшить время его выключения.

1120462

Составитель В. Жмуров

Техред 3. Палии Корректор М. Дем ик

Редактор Л. Лосева

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4

Заказ 7757/43 Тираж 666 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5