Устройство для записи цифровой информации

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ ЗАПИСИ ЦЙФРО ВОЙ ИНФОРМАЦИИ, соде рзкащее вярдную и выходную информафюнные штны, гене ратор импульсов, вход которого подключен через счетчик к инверсному входу элемента равнозигачности, первый регистр, инфо)р(ма1|ионный вход которого соединен с входной информационной шиной, а тактовый вход -. с инверсным входом эл(ента равнозначности , прямой вход которого подключен к выходу второго разряда первого регистра, и коммутатор, первеш четыре входа которого связаны соот ветственно с выходами первого, второго , третьего и четвертого разрядов первого регистра, отличающееся тем, что, с целью повышения . помехозащищенности устройства, в него введены второй регистр и два триггера, а коммутатор выполнен на трех ;элементах И-НЕ эле менте ШШтНЕ, двух элементах ИСКЛЮЧАЮЩЕЕ ИЛИ, двух элементах И-ШШ и инверторе, причем первые входы первого и второго элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, первого элемента Ии первого элемента И-ШШ соединены и являются первым входом ко Ь утатора , второй вход которого подключен ко второму входу первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, третий вход подкхю чен к второму входу второго элемента ИСКШ ШОЩЕЕ ИЛИ и первому входу элемента ИЛИ-НЕ, выход которого срединен с вторым и третьим вхрдами первого элемента И-ИЛИ, а второй; вхЬд.объединен с первьн входом второго элемента И-НЕ и с выходом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, а четвертый вход (утатора подключен S К четвертому входу первого И-ИЛИ и второму входу первого элемента И-НЕ, выход которого соединен с вторым входом второго элемента И-НЕ, третий вход последнего соедияен с выходом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход второго эле;мента И-НЕ соединен с первьм входом третьего элемента , второй вход которого соединён с выходом инвертонд :ра, 8 выход - с Первым входом второго элемента , второй вход коР , торого подключен к выходу первого :п элемента И-ШШ пятый вход коьмутатора соединен с Т1 етьим входом второго элемента И-ШШ и с выходом первого разряда счетчика, выход второго разряда, которого связан с четвергам . входом второго элемента И-ШШ, с ;входом инвертора и с шестым входом коммутатора, выход последнего подключен к тактов гу входу первого триггера, информационный вход которого соединен с выходом элемента

СОЮЗ СОВЕТСНИХ

Ц

РЕСГ1УБЛИН

gyp G 11 В 5/09

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

K ABT0PCHOMV СЭИДВТЦЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И Of ÍÐÈÒÜÉ (21) 3565853/18-10 (22) 10.03;83 (46) 07.11.84. Бкш. В 41(72) В.В.Иванов и А.Ф.Плевако (71) Киевский .научно-исследователь.ский и конструкторский институт- пери- ферийного оборудования. (53) 534 ..852(088.8) .(56) 1. Патент Японии е 51-33401, кл. 102Е-33+, 1976.

2. Авторское свидетельство СССР.

В 877607, кл. G 11 В 5/09, 1979 (прототип). (54)(57) УСТРОЙСТВО ДЛЯ ЗАПИСИ ЦИФРО

ВОЙ ИНФОРМАЦИИ, содериащее входную и выходную информационные шины, генератор импульсов, вход которого подключен через счетчик к йнверсноиу входу элемента равнозначности, 1еер» вый регистр, информационный вход которого соединен с входной информационной шиной, а тактовый вход -. с инверсным входом элемейта равнозначности, прямой вход которого подключен к выходу второго разряда первого регистра, и коммутатор, первые четыре входа которого связаны соот.. ветственно с выходами первого, второго, третьего и четвертого разрядов первого регистра, о т л и ч а ющ е е с я тем,. что, с целью иовышения помехозащищенности устройст- .

sa, в него введены второй регистр и два триггера, а коммутатор выполнен на трех элементах И-НБ, элементе ИЛИ..-HK, двух элементах ИСИП0ЧАКЩЕЕ ИЛИ, двух элементах И-ИЛИ и инверторе, причем первые входы, SU„„112 А первого и второго элементов ИСКЛЮЧАЯЦЕЕ ИЛИ, первого элемента И-НЕ и первого элемента И-ИЛИ соединены и являются первым входои коммутатора, второй вход которого подключен . ко второму входу первого элемента

ИСКЛЮЧАЮЩЕЕ ИЛИ, третий вход подключен к второму входу второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и первому входуэлеиента ИЛИ-НЕ, выход которого соединен с вторыи и третьии входаии первого элемента И-ИЛИ, а второй вход объединен с первьи входом второго элемента И-НЕ-и с выходом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, а четвертый вход кожутатора подключен Я к четвергоиу входу первого элемента

И-ИЛИ и второму входу первого элемента И-НЕ, выход которого соединен с вторым входом второго элемента, И-НЕ, третий вход последнего соеди- д иен с выходом второго элемента

ИСИПОЧАЮЩЕЕ ИЛИ, выход второго эле- .мента И-НЕ соединен с лервым входом третьего элемента И-.НЕ, второй вход . которого соединен-с выходои инверто-.

:ра, а выход - с первым входои второго элемента И-.ИЛИ, второй вход ко,торого-подключен к выходу первого элемента И-.ИДИ, пятый вход коммута- . тора соединен с третьии входом второго элемента И-ИЛИ и с выходом первого разряда счетчика, выход второго разряда которого связан с четвертым входом .второго элемента И-ИПИ, с входом инвертора и с Шестыи входом коммутатора, выход последнего подключен к тактовому входу первого триггера, информационный вход кото-рого соединен с выходом элемента равнозначности, а выход — с информационным входом второго регистра и со счетным входом второго триггера, выход генератора импульсов подключен к тактовому входу второго ре1123051 гистра, выход которого соединен с установочным входом второго триггера, а выход второго триггера подключен к выходной информационной шине.

Изобретение относится к области накопления информации и может быть использовано в качестве устройства записи цифровой информации в трехчастотном коде. 5

Известно устройство для записи. информации, содержащее блок трехчастотного кодирования, генератор импульсов, счетчик и элемент НЕ (I) .

Недостатком этого устройства 10 является снижение надежности работы устройства при повышении плотности записи из-за погрешности записи, Наиболее близким по технической сущности к изобретению является устройство для записи цифровой информации, содержащее входную и выходную информационные шины, генератор импульсов, выход которого подключен через счетчик к инверсному входу элемента равнозначности, первый регистр, информационный вход которого соединен с входной информационной шиной, а тактовый вход — с инверсным входом элемента равнозначности, пря- 2 мой вход которого подключен к выходу второго разряда первого регистра, и коммутатор, первые четыре входа которого связаны соответственно с выходами первого, второго, третьего и четвертого разрядов первого регистра, формирователь сдвинутых серий и усилитель записи, причем коммутатор выполнен из элементов И и ИЛИ (2) .

Недостатком известного устройства

35 является его низкая помехозащищенность из-за возникновения помехи в сигнале при сложении по модулю два вследствие несовпадения фронтов импульсов.

Целью изобретения является повышение помехозащищенности устройства.

Поставленная цель достигается тем, что, в устройство для записи цифровой информации, содержащее вход-45 ную и выходную информационные шины, генератор импульсов, выход которого подключен через счетчик к инверсному входу элемента равнозначности, первый регистр, информационный вход которого соединен с информационной входной шиной, а тактовый вход — с инверсным входом элемента равнозначности, прямой вход которого подключен к выходу второго разряда первого регистра, и коммутатор, первые четыре входа которого связаны соответственно с выходами первого, второго, третьего и четвертого разрядов первого регистра, введены второй регистр и два триггера, а коммутатор выполнен на трех элементах ИНЕ, элементе ИЛИ-НЕ, двух элементах

ИСКЛЮЧАЮЩЕЕ ИЛИ, двух элементах ИИЛИ и инверторе, причем первые входы первого и второго элементов

ИСКЛЮЧАЮЩЕЕ ИЛИ, первого элемента

И-НЕ соединены и являются первым входом коммутатора, второй вход которого подключен к второму входу первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, третий вход подключен к второму входу второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и первому входу элемента ИЛИ-НЕ, выход которого соединен с вторым и третьим входами первого элемента И-ИЛИ, а второй вход объединен с первым входом второго элемента И-HE и с выходом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, а четвертый вход коммутатора подключен к четвертому входу первого элемента И-ИЛИ и второму входу первого элемента И-HF., выход которого соединен с вторым входом второго элемента И-НЕ, третий вход последнего соединен с выходом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход второго элемента И-НЕ соединен с первым входом третьего элемента И-НЕ, второй

11230 >! 4 вход которого соединен с выходом инвертора, а выход — с первым входом второго элемента И-ИЛИ, второй вход которого подключен к выходу первого элемента И-ИЛИ, пятый вход коммутатора соединен с третьим входом второго элемента И-ИЛИ и с выходом первого разряда счетчика, выход второго. разряда которого связан с четвертым входом второго элемента

И-ИЛИ, с входом инвертора и с шестым входом коммутатора, выход последнего подключен к тактовому входу первого триггера, информационный вход ! которого соединен с выходом эле,мента равнозначности, а выход — с информационным входом второго регистра и со счетным входом второго триггера, выход генератора импульсов подключен к тактовому входу второго регистра, выход которого соединен с установочным входом второго триггера, а выход второго триггера подключен к выходной информационной шине.

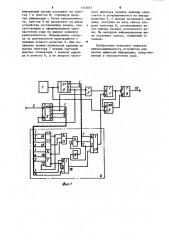

На фиг.1 изображена функциональная схема устройства для записи цифровой информации, на фиг.2 — временные диаграммы работы элементов устройства.

Устройство содержит генератор 1 импульсов, регистр 2 сдвига, информационный вход которого подключен к информационной шине 3, коммутатор

4, обеспечивающий необходимые фазовые предискажения при записи, элемент 5 равнозначности, счетчик 6, триггер 7, триггер 8 и регистр 9, при этом коммутатор выполнен на трех элементах И-НЕ 10-12, элементе ИЛИНЕ 13, двух элементах ИСКЛЮЧАЮЩЕЕ

ИЛИ 14 и 15, двух элементах И-ИЛИ

16 и 17 и инверторе 18, причем первые входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ

14 и 15, элемента И-НЕ 10 и элемента И-ИЛИ 16 соединены и являются первым входом коммутатора 4, второй вход которого подключен к второму входу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 14, третий вход подключен к второму входу элемента ИЛИ-НЕ 13, выход которого соединен с вторым и третьим входами элемента И-ИЛИ 16, а второй вход объединен с первым входом элемента И-HF. 11 и с выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 14, а четвертый вход коммутатора подключен к четвертому входу элемента И-ИЛИ 16 и второму входу элемента И-НЕ 10, выхол которого соединен с вторым входом элемента И-НЕ 1?, третий вход последнего соединен с выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 15, выход второго элемента И-HF- 12 соединен с первым входом третьего элемента

И-НЕ 12, второй вход которого соединен с выходом инвертора, а выход— с первым входом элемента И-ИЛИ !7, второй вход которого подключен к выходу элемента И-ИЛИ 16, пятый .вход коммутатора соединен с третьим входом элемента И-ИЛИ 16 и с выходом первого разряда счетчика 6, выход второго разряда которого связан с четвертым входом элемента И-ИЛИ, с входом инвертора 18, и с шестым входом коммутатора 4, выход последнего подключен к тактовому входу триггера 7, информационный вход которого соединен с выходом элемента .5 равнозначности, а выход — с информационным входом регистра 9 и со счетным

1О!

20 тактовому входу второго регистра 9, выход которого соединен с установочным входом второго триггера 8, а выход второго триггера 8 подключен к информационной шине 19. Выход генератора 1 подключен также через счетчик 6 к инверсному входу элемента 5 равнозначности. Тактовый вход первого регистра 2 соединен также с инверсным входом элемента 5 равнозначности, прямой вход которого подключен к выходу второго разряда регистра 2, а четыре первых входа коммутатора связаны соответственно с выходами первого, второго, третьего и четвертого разрядов регистра 2.

ЗО

40

Устройство для записи информации работает следующим образом.

При воспроизведении цифровой информации, импульс, находящийся на стыке двух неравных интервалов, смещается в сторону более длительного интервала, вследствие чего происходят фазовые искажения. Для компенса ции этого смещения коммутатор 4 анализирует поступающую на его первые

50 четыре входа информацию с выхода регистра 2 и пропускает на выход один из сигналов g и (фиг.2) или результат их сложения, обеспечивая тем самым смещение импульса в сторону более короткого интервала. Сфор55

25 !входом второго триггера 8, выход ге нератора 1 импульсов подключен к

3 11 мированный сигнал поступает на триггер 7 и триггер 8, стробируя входную информацию с блока равнозначности. Триггер 8 не пропускает на выход устройства составляющую помехи, присутствующую в сформированном трехчастотном коде на выходе элемента равнозначности. Формирование сигнала по длительности производится с помощью второго регистра 9. При появлении уровня логической единицы на выходе триггера 7 первый тактовый импульс. генератора 1 заносит единицу в регистр 9, а от второго такто23051 ваго импульса уровень единицы сдвигается и устанавливается на выходе регистра 9. С выхода последнего единица, поступая на вход сброса вто5 рого триггера 8, устанавливает на его выходе уровень логического нуля. На выходную информационную шину поступает сигнал, очищенный от помехи.

Изобретение позволяет повысить помехозащищенность устройства для .записи цифровой информации, представленной в трехчастотном коде.

1123 051

Составитель Л.Кондрыкинская

Техред А.Бабинец Корректор А.Зимокосов

Редактор Н.Пушненкова

Подписное

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4

Заказ 8147/41 Тирах 574

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, .Ж-35, Раушская наб., д. 4/5