Формирователь импульсов

Иллюстрации

Показать всеРеферат

ФОРМИРОВАТЕЛЬ ИМПУЛЬСОВ, содержащий первый и второй МДП-транзисторы п-типа проводимости, третий МДП-транзистор р-типа проводимости, шину питания и пину нулевого потенциала , причем исток первого ОДПтранзистора и-т1ша проводимости соединен со стоком второго МДП-транзистора п-типа проводимос-ги, затвор которого соединен со стоком третьего ЩП-транзистора р-типа проводимости, затвор первого МДП-транзистора и проводимости является первым управляющим входом устройства, и сток соединен с шиной питания, отличающийся тем, что, с цепью снжкения потребляемой мощности, в него введены четвертый и пятый МДПтранзисторы п-типа проводимости, причем исток третьего МДП-транзистора р-типа проводимости соединен с шиной питания, а затвор - с затвором первого МДП-транзистора п-типа проводимости , истоки четвертого и пятого ЩЩ-транзисторов п-типа проводимости подключены к шине нулевого потенциала , затвор четвертого МЩ1-транзистора и-типа проводимости является вторым управляющим входом устройства , сток четвертого МДП-транзистора п-типа проводимости соединен с истоком второго ОДП-транзистора «-типа проводимости и с затвором пятого МДП-транзистора 1 -типа проводимости, сток которого соединен со стоком третьего МДП-транзистора р-типа проводимости .

Ц11. С 11 С 7/00 (21) 3637500/24-24 (22) 22.08.83 (46) 07.11.84.Бюл. Р 41 (72) С.Н.Косоусов, В.А.Максимов и Я.Я.Петричкович (53) 681.327(088.8) (56) !. Патент США У 4025801, кл. С 11С 7/00, опублик. 1980.

2. Патент Великобритании

У 2028044, кл. С 11 С 7/00, опублик. 1980 (прототип). (54) (57) ФОРИИРОВАТЕЛЬ ИИПУЛЬСОВ, содержащий первый и второй ИДП-транзисторы и-типа проводимости, третий

ИДП-транзистор р-типа проводимости, шину питания и шину нулевого потенциала, причем исток первого ИДПтранзистора и-типа проводимости соединен со стоком второгб ИДП-транзистора и-типа проводимости, затвор которого соединен со стоком третьего

ИДП-транзистора р-типа проводимости, затвор первого ИДП-транзистора и-тнпа проводимости является первым управляющим входом устройства, и сток соединен с шиной питания, о т л и— ч а ю шийся тем, что, с целью снижения потребляемой мощности, в него введены четвертый и пятый %UI pa sacxopv и-типа проводимости, причем исток третьего ИДП-транзистора р-типа проводимости соединен с шиной питания, а затвор — с затвором первого ИДП-транзистора л-типа проводимости, истоки четвертого и пятого ИДП-транзисторов и-типа проводимости подключены к шине нулевого потенциала, затвор четвертого ИДП-транзистора 1-типа проводимости является Q вторым управляющим входом устройства, сток четвертого ИДП-транзистора п-типа проводимости соединен с истоком второго ИДП-транзистора и-типа проводимости и с затвором пятого

HgII-транзистора и -типа проводимости, сток которого соединен со стоком третьего ИДП-транзистора р-типа проводимостн.

1123

Изобретение относится к вычислительной технике и электронике и может быть использовано при построении устройств для считывания информации иэ накопителей запоминающих устройств в качестве элемента, осуществляющего . подэаряд емкостей, образуемых шинами данных.

Известен формирователь импульсов для подзаряда емкостей, содержаший 10 пару последовательно включенных МДПтранзисторов, причем затвор и сток одного из транзисторов объединены tel

Недостатком данного устройства является непроизводительное потребление мощности источника питания за счет протекания сквозного тока через пару транзисторов в режиме формирования уровня предварительного заряда.

Наиболее близким по технической сущности к изобретению является фор- . мирователь импульсов, содержащий последовательно включенные межцу шиной питания и общей шиной первый, второй МДП-транзисторы р типа проводимоети и третий, четвертый МДПтранзисторы и -типа проводимости, причем затворы первого и четвертого

МДП-транзисторов соединены со стоками второго и третьего МДП-транзисто30

pO8 MTBOphI K0TOpblX RBJIRI0TCB С00Т» ветственно инверсным и прямым управляющими входами Г2).

Недостатком известного устройства является рассеяние мощности истояника питания в течение времени дейст-, вия управляющего импульса обусловленное сквозным током через открытые транзисторы.

Целью изобретения является снижение потребляемой мощности формирователя импульсов.

Поставленная цель достигается . тем, что .в формирователь импульсов, содержацщй первый и второй МДП-транзисторы -тина проводимости, третий

МДП-транзистор и-типа проводимости. .шину питания и шину нулевого потен056 2 тый и пятый МДП-транзисторы И -типа проводимости, причем исток третьего

МДП-транзистора р -типа проводимости соединен с шиной питания, а. затвор— с затвором первого МДП-транзистора П-тина проводимости, истоки четверто го и пятого МДП-транзисторов и -типа проводимости подключены к шине нулевого потенциала, затвор четвертого

МДП-транзистора и-типа проводимости является вторым управлякпцим входом устройства, сток четвертого. МДПтранзистора и-типа проводимости соединен с истоком второго МДП-транзистора и - типа проводимости и с затвором пятого МДП-транзистора о -,типа проводимости, сток которого соединен .со стоком третьего.МДП-транзистора р-,типа проводимости.

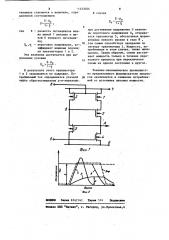

На фиг. 1 представлена схема предлагаемого устройства; на фиг. 2кривые переходных процессов.

Формирователь ймпульсов содержит первый 1 и второй 2 МДП-транзисторы й-типа проводимости, третий 3 МДПтранзистор р --тина проводимости, четвертый 4 и пятый 5 МДП-транзисторы и-тина проводимости, шину.б нулевого потенциала, шину 7 литания, шины

8 и 9 управления (входы).

Устройство работает в .режиме начальной установки и в режиме нодзаряда. В режиме. начальной установки на управляющих входах 8 и 9 установлены противоположные логические уровни "0" и "1", открываняцие транзисторыЗи4.

Открытые траэисторы обеспечивают в точках 4 и 6 формирование уровней, соответствующих потенциалам шин б и 7 (низкий и высокий). сьответственио. Потенциал узла А (низкий) является запирающим по отношени о к .

4 транзистору 5, поэтому схема представляет комплементарную структуру; величина потребляемого от источника питания тока определяется только токами утечки. зистора -тина проводимости, затвор первого МПП-транзистора п -типа проводимости является первым управляющим входом устройства, а.сток соединен с шиной питания, введены четвер55 циала, причем исток первого МДП-транзистора и-типа проводимости соединен 5О со стоком второго МДП-транзистора й-типа проводимости, затвор которого соединен со стоком третьего МДП-транВ режиме подзаряда на управлякнцих входах 8 и 9 установлены соответственно противоположные логические уровни "1" и "0", закрывающие транзисторы 3 и 4. Открывающийся при этом первый 1 трайзистор и открытый пятый 5 транзистор обеспечивают изменение потенциала узла А, Напряжение между узлом А и шиной б нулевого по-

В случае

Е 00

О 1Ф ам<

Фиг. 8

ВНИИПН Заказ 8 f 47/41 Тираж 574 Подшсиюе

Фщщал ППП Патент", г, Ужгород, ул. Проектная,4 з 11230 тенциала стремится к величине, определяемой соотношением ""о

U=1+

5 где Š— разность потенциалов йежжу шиной 7 питания и ши ной 6 нулевого потенциала;

U ..,,à — пороговое напряжение, ко-. эффициент влияния подложки транзисторов 1 и 2.

Эта величина достигается при выполнении условия !

E-uo

0 о <+g

В результате этого транзисторы

1 и 2 закрываются по подложке. Потребляемый ток определяется утечкой .20 через обратносмещенные р-п-переходы. при достижении напряжения 0 величины порогового напряжения Uo открывается транзистор 5, обеспечивая формирование низкого уровня в узле 8, тем самым способствуя запиранию по затвору транзистора 2, Мощность, потребляемая в этом случае, также минимальна. Таким образом, схема рассеивает мощность только в течение переходного процесса при переключении схемы из одного состояния в другое.

Технико-экономическое преимущество предлагаемого формирователя импульсов заключается в снижении потребляемой от источника питания мощности.