Система автоматического управления циклическими процессами

Иллюстрации

Показать всеРеферат

СИСТЕМА АВТОМАТИЧЕСКОГО УПРАВЛЕНИЯ ЦИКЛИЧЕСКИМИ ПРОДЕССАМИ, содержащая последовательно соединенные измеритель рассогласования, усилитель, фильтр, сумматор и исполнительное устройство, подключенное выходом к входу объекта регулирования , выход которого соединен с сигнальным входом датчика обратной связи , первый вход измерителя рассогласования подключен к выходу датчика обратной связи, второй вход сумматора соединен с выходом блока памяти, выход сумматора соединен с первым входом блока памяти, второй вход которого соединен с выходом таймерного устройства и входом программного устройства, выходом подключенного к второму входу измерителя рассогласования , отличающаяся тем, что, с целью повышения производительности оборудования, в нее введены счетчик тактов, последовательно соединенные блок коррекции, реверсивный счетчик и нелинейный блок, выходом подключенный к входу таймерного устройства, первый вход блока коррекции соединен с выходом измерителя рассогласования, второй вход - с вторым входом нёлийейного блока и с выходом счетчика тактов, вход которого подключен к выходу таймерного .устройства.

СОЮЗ СОВЕТСНИХ

СО14ИАЛИСТИЧЕСНИХ

РЕСПУБЛИК

0% 01) 3(5g 05 В 13/02

ОПИСАНИЕ ИЗОБРЕТЕНИЯ;

К ILBIOPCNOMV СЗИДВтвъстви

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

1 10 ДЕЛАМ ИЗОБРЕТЕНИЙ И OTHPblTHA (21) 3582717)24-24 (22) 21.04.83 (46) 15.11.84. Бюл. У 42 (72) В.Г.Жуковский, А.И.Евченко и И.Н.Быкадоров (53) 62-50(088.8) (56) 1. Авторское свидетельство СССР

В 723510, кл. Q 05 В 17/00, 1975.

2. Анхимюк В.Л. Теория автоматического управления ° Минск, "Высшая школа", 1979, с. 10. (54)(57) СИСТЕМА АВТОМАТИЧЕСКОГО

УПРАВЛЕНИЯ ЦИКЛИЧЕСКИМИ ПРОЦЕССАМИ, содержащая последовательно соединен ные измеритель рассогласования, усилитель, фильтр, сумматор и исполнительное устройство, подключенное выходом к входу объекта регулирования, выход которого соединен с сигнальным входом датчика обратной связи, первый вход измерителя рассогласования подключен к выходу датчика обратнбй связи, второй вход сумматора

I .соединен с выходом блока памяти, выход сумматора соединен с первым входом блока памяти, второй вход которого соединен с выходом таймерного устройства и входом программного устройства, выходом подключенного к второму входу измерителя рассогласо" вания, отличающаяся тем, что, с целью повышения производительности оборудования, в нее введены счетчик тактов, последовательно соединенные блок коррекции, реверсив" ный счетчик и нелинейный блок, выхо" дом подключенный к входу таймерного устройства, первый вход блока кор- Я рекции соединен с выходом измерителя рассогласования, второй вход - с

1вторым входом нелийейного блока и с выходом счетчика тактов, вход которого подключен к выходу таймерного ,устройства.

1124247 2

Цель изобретения — повышение производительности оборудования.

Укаэанная цель достигается тем, что в систему автоматического управления циклическими процессами, содержащую последовательно соединенные измеритель рассогласования, усилитель, фильтр, сумматор и исполнитель-55 ное устройство, подключенное выходом к входу объекта регулирования, выход которого соединен с сигнальным вхоИзобретение относится к системам автоматического управления и регулирования и может использоваться для . Управления процессами с циклическим характером выполняемой программы.

Известна система автоматического

/ регулирования, содержащая задатчик требуемого и датчик реального значений регулируемого параметра, устройство сравнения, фильтр, усилитель 10 и объект регулирования (1j .

Недостатком известной системы является невысокая точность регулирования, что обусловлено инерционностью следящей системы и ограниченной величиной ее коэффициента усиления.

Наиболее близкой к предлагаемой является система автоматического регулирования, содержащая измеритель рассогласования, выход которого через усилитель подключен к входу сглаживающего фильтра, объект регулирования, вход которого подсоединен к выходу исполнительного устройства, датчик обратной связи, связанный с объектом регулировки и входом измерителя рассогласования, программное устройство, к выходу которого подключен вход измерителя рассогласования, сумматор, входами подключенный к выходам фильтра и блока памяти, а выходом — к входам блока памяти и исполнительного устройства, и таймерное устройство, выходами связанное с управляющим входом блока памяти. При этом, блок памяти — это два двухпоэиционных переключателя и два блока записи-воспроизведения информации (2) .

Однако известная система автоматического регулирования не позволяет использовать уменьшение ошибки управления после нескольких циклбв отработки программы для уменьшения времени цикла и повышения производи45 тельности оборудования, управляемого и регулируемого известной системой.

1 дом датчика обратной связи, первый вход измерителя рассогласования подключен к выходу датчика обратной связи, второй вход сумматора соединен с выходом блока памяти, выхбд сумматора соединен с первым входом блока памяти, второй вход которого соединен с выходом таймерного устройства и входом программного устройства, выходом подключенного к второму входу изяерителя рассогласования, введены счетчик тактов, последовательно соединенные блок коррекции, реверсивный счетчик и нелинейный блок, выходом поключенный к входу таймерного устройства, первый вход блока коррекции соединен с выходом измерителя рассогласования, второй вход — с вторым входом нелинейного блока и с выходом счетчика тактов, вход которого поключен к выходу таймерного устройства.

Предлагаемая система отличается от известной тем, что после того, как вследствие самонастройки максимальное в цикле значение ошибки г. (т,) не превышает порогового эначеЩ ния E:JE+ (t) j Е, в таймерное устройство заносится код времени, соответствующий меньшей длительности цикла, Уменьшение длительности цикла приводит к увеличению ошибок управления, однако новое значение длительности цикла должно быть выбрано таким образом, чтобы новое значение максимальной ошибки в цикле не превышало максимально допустимого значения ж . погрешности управления. Таким образом, при выполнении поставленных требований по точности управления длительность цикла уменьшается, что ведет к повышению производительности.

В предлагаемой системе в каждом новом цикле работы кроме информации в текущем отклонении регулируемой координаты от требуемого значения используется также информация о процессе регулирования на предыдушем цикле, что уменьшает динамический диапазон выходных .сигналов, снима-. емых с измерителя рассогласования, что приводит к увеличению тсчности от цикла к циклу. Б конечном счете, после обработки системой ц циклов ошибка регулирования становится меньше заданной. ПрА достижении этой ситуации в таймер заносится код времени, меньший кода, с которым были

3 11242 отработаны системой и предыдущих циклов. Уменьшение длительности цикла влечет эа собой изменение скорости выполнения программы, обусловливая тем самым изменение динамичесикх характеристик объекта регулирования.

Принцип функционирования системы сохраняется прежним — в каждом новом цикле сигнал управления содержит две составляющие: одна определяется сиг- 1р налом текущего отклонения координаты, вторая - сигналом управления, выработанным в предыдущем цикле. Отработка следующих rn циклов производится до тех пор, пока максимальное в цикле 15 значение ошибки не станет меньше Е, после чего опять производится уменьшение кода времени, назначающего длительность цикла, и процесс регулирования продолжается в соответствии с вышеизложенным.

Пусть в серии иэ и циклов длительность каждого цикла равна Т„ и в каждом цикле запоминается значений управляющих воздействие и выдается в g5 систему регулирования. Тогда частота выдачи управляющих воздействий в

-! этой серии равна 9 = E T

После отработки циклов в таймер поступает код времени T = T> К с Т, где Кл — коэффициент, учитывающий уменьшение длительности цикла.

При этом частота объема и выдачи информации равна

1 (1) 35

rpe 1, ) — соответственно частоты съема информации и выдачи дополнительно управляющего воэдейст- 4О вия для серий иэ h u

tn циклов

Š— пороговое значение погрешности;

Ем — максимально допустимое 45 значение погрешности в системе управления °

Таким образом, для того, чтобы сжатие (т.е. скорость считывания и выдачи) информации и уменьшение длительности цикла происходило пропорционально, в процессе управления необходимо учитывать (1), что осуществляется нелинейным блоком.

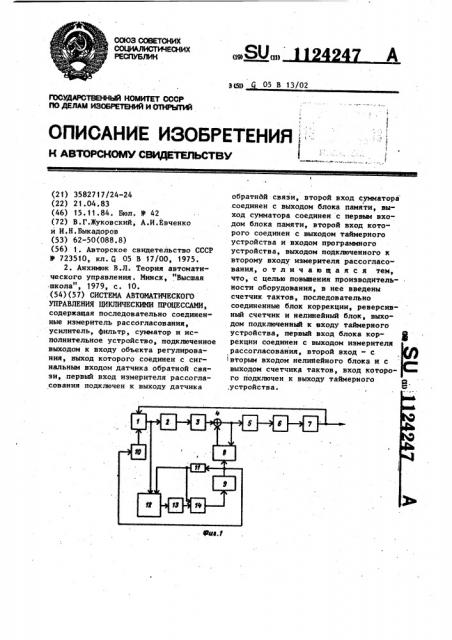

На фиг. 1 изображена структурная 55 схема предлагаемой системы автоматического регулирования; на фиг. 2 структурная схема блока коррекции

47 4 (вариант); на фиг. 3 — структурная схема блока памяти.

Система содержит измеритель 1 рассогласования, усилитель 2, фильтр

3, сумматор 4, исполнительное устройство 5, объект 6 управления, датчик 7 обратной связи, блок 8 памяти, таймерное устройство 10, счетчик 11 тактов, блок 12 коррекции, реверсивный счетчик 13 и нелинейный блок 14.

:Блок 12 коррекции (фиг. 2) содержит линию 15 задержки, задатчик

16 порогового значения погрешности. блок 17 сравнения. триггер 18 и логический элемент И 19.

Блок 8 памяти состоит из цифроаналогового преобразователя 20, блока

21 регистров аналого-цифрового преобразователя 22, сборки 23 линий saдержки, причем в блоке 21 содержится (3+1) регистр, а в сборке 23 — (ь-1) линий задержки.

Блок 8 работает по принципу памяти

FIF0: первый сигнал, который записан в блоке памяти, первым выдается в систему регулирования °

Нелинейный блок 14 построен на базе очейки памяти, делителя и умножителя.

Система работает следующим образом.

Цикл работы состоит из тактов одинаковой длительности. В блоке 8 памяти записана информация о величине управляющего воздействия, сформированного в предыдущем цикле. Через время = Т„ ь (где Т„ — длительность k -го цикла) от таймерного устройства 9 поступает сигнал управления .на блок 8 памяти, в результате чего с выхода блока 8 на второй вход сумматора 4 поступает сигнал управления для номера такта, на единицу меньшего текущего и записанного в блок 8 в предудыщем цикле. На первый вход сумматора 4 от измерителя 1 рассогласования через усилитель 2 и фильтр 3 подается сигнал, пропорциональный разности между требуемым в данном такте значением управляемой величины, подаваемым от программного устройства по сигналу управления, выработанному таймерным устройством 9, и фактическим, поступающим от датчика 7 обратной связи. Полученный таким образом сигнал управления, снимаемый ! с выхода сумматора 4, записывается в блок 8 памяти и одновременно подается на исполнительное устройство 5, подБлок 8 работает следующим образом.

В первом цикле в регистры блока 2 1 от АЦП 22 записывается 8 значений выработанных управляющих воздейс.гвий., По сигналу, полученному от таймер1 ного устройства 9, осуществляется

45 сдвиг записанной в блоке 21 регистров информации влево и выдача на

ПАП 2О в первом такте второго цикла управляюще ro воздействия, полученного в первом такте первого цикла. После этого от линии задержки сборки 23

5О поступает сигнал, разрешающий запись от АЦП 22 скорректированного сигнала управления первого такта второго цикла в (+1)-й регистр. С окончанием каждого такта в цикле осуществляется процесс сдвига влево записанной информации выдачи через ЦАП 2G в систему соответствующих дополнительных управлений и их записи.

5 112424 ключенное к объекту 6 регулирования, переводя его в состояние, отвечающее заданному. Программное устройство; 10 может представлять соббй 3 ячеек памяти, последовательно подключаемых 5 таймерным устройством.

Счетчик 11 тактов служит для определения ситуации, отвечающей окончанию цикла: по этому признаку от счетчика 11 поступает сигнал, включающий блок 12 коррекции и нелинейный блок 14.

В блоке 12 коррекции производится оценка максимального в цикле ошибки

Eö(4 ) с пороговым значением 1.. Если 15

j Eм (1) 4, то блоком коррекции вырабатывается сигнал коррекции кода времени, поступающий на реверсивный счетчик 13, где формируется код длительности цикла, меньший кода длитель 2О ности предудыщего цикла, который был записан в счетчик 13 (по правилу Т ч

Этот код подается на первый вход нелинейного блока 14, где в соответствии с формулой (1) вырабатывается сигнал управления таймерным устройством 9, учитывая тем самым требование изменения частоты выдачи управляющих воздействий в системе, связанное с изменением длительности 3й цикла. Выход таймерного устройства 9 связан с входом счетчика 11 тактов.

При переполнении счетчика вырабатывается сигнал, подключающий блок 14, заставляя его вырабатывать сигнал управления теймерным устройством 9.

При переполнении счетчика 11 он сигнализирует об окончании цикла, и вырабатывает сигнал на подключение блока 12 коррекции.

Так как программа управления во времени от цикла к циклу строго повторяется, то уменьшение длительности цикла приводит к увеличению скорости отработки задания, а зто — к ситуации! м (<) ) 6, которая оценивается блоком l2 коррекции, управляющая часть которого включается счетчиком

11 в конце каждого цикла. Новый код длительности цикла сохраняется до тек пор, пока максимальная в предыдущем цикле ошибка не станет меньше порогового значения Е, после чего для следующего цикла назначается новый код длительности и процесс продолжается в соответствии с вышеописанным.

Блок 12 коррекции работает следующим образом.

7 б

С выхода измерителя 1 рассогласования в течение цикла на один из входов блока 17 сравнения поступает

3 значений ошибок, на другой вход которого подается от задатчика 16 порогового значения погрешности сигнал,,пропорциональный Я . Если Е (4) 6 Е, то в устройстве сравнения вырыбатывается сигнал, в против" ном случае сигнал не вырабатывается.

Пусть имеет место второй случай, Тогда триггер 18 закрыт, поэтому закрыт логический элемент И 19, от блока коррекции на реверсивный счетчик 13 сигнал коррекции кода длительности цикла не поступает и код остается прежним.

При наличии ситуации 1 C„(<)l f. от блока 17 сравнения íà R -вход триггера 18 поступает сигнал, пере- . водящий его в состояние "1". Этот сигнал "1" подается на первый вход логического элемента И 19, на второй вход которого по окончании цикла подается "1" от счетчика 11. В соответствии с принципом работы логическо" го элемента И 19 на его выходе появляется сигнал управления реверсивным счетчиком 13, заставляющий последний изменять код длительности цикла (т.е. счетчик 13 запускается сигналом "1") .

Через линию 15 задержки сигнал от счетчика f 1 тактов поступает на

5-вход триггера 18, обнуляя его. Этот канал необходим для подготовки триггера к работе в следующем цикле.

1124247

Сравним (2) и (3):

Т -Т„=

ОмЮ1

Покажем, что использование предлагаемой системы по сравнению с прототипом» который примем за базовый образец, ведет к уменьшению общего времени изготовления изделия при сохранении поставленных требований, т.е. к повьппению производительности оборудования.

Пусть время уменьшения длительности каждого цикла 6 ñ< удовлетворяет требованию (E А, (t) l м . Кроме того, очевидно, что длительность цикла ограничена снизу величиной »,кр .

Если длительность цикла обозначить через t» и изделие изготавли- 15 вается за Й циклов» то при использовании базового образца время изготовления изделия равно

Т =, й, (2)

Рассмотрим процесс изготовления изделия в условиях применения предлагаемой системы.

Пусть отработано »<„ i N циклов с длительностью каждого циала t<, после 25 чего максимальная ошибка в цикле

E (E;) стала меньше порогового значения Я . Длительность цикла уменьшается tg =t<-î< < 4» и система работает 2< N циклов до возникновения ситуа- ZO ции IE »<,(<)l E . Дальше процесс повторяется до тех пор, пока 1»< не станет л равно <,„,, после чего длительность . цикла не уменьшается и оставшиеся к-» 35 (9-,» »1; ) циклов работа идет с дли1=1 и тельностью каждого цикла

Тогда время изготовления изделия составляет

К-< К-1

I TH = : 1; я; (4 „ N-Е п;1= KN <К И „ tк) п; .

<-1 < если »О =, то выигрьпп во во вр< мени изготовления есть; если А О, то выигрыша по времени изготовления нет; к-< ъ = нАн —.,(;- )»;-И,- „1 -К,- д, ;Е (-Чи;=(6,-1 j(-,\-.Е Ь;-t.1и„..

Очевидно, что при <- Ъ разница (4 - ») - О, т.е. под знаком суммы са" мый большой сомножитель (t -<к)к(1; ).

Оценим наихудший результат, т.е. выражение под знаком суммы представим в виде гк- » вам(Е <4 < ln;)=(t <к1(ю,tn i„,tn„.,) .Тогда

Гр- п=(,-1,l(n, n2 ...+<„-n,)- (t., „) (,„ "S ° ° ° +ПК-

Т -Т< > О и предлагаемая система по сравнению с базовым образцом дает выигрыш во времени изготовления изделий, или при фиксированном времени обеспечения — выпуск большего количества единиц продукции.

1124247

Заказ 8277/35

Тираж 841

Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4

Составитель П. Кудрявцев

Редактор И. Рыбченко Техред И.Гергель Корректор М. Максимижинец