Устройство приоритета

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ПРИОРИТЕТА, содержащее дна регистра, первую группу элементов И и элемент ИЛИ, причем единичный выход каждого разряда первого регистра соединен с первьвл входом одноименного элемента И первой группы, выход каждого элемента И первой группы соединен с единйчньм входом одноименного разряда второго регистра, входы элементов И первой группы соединены с первьм тактовым входом устройства, нулевой выход i-ro ( i 1, ..., n,nчисло запросов) разряда первого регистра соединен с соответствующим входом каждого j-ro ( jr i+i,.., ,п) элемента И первой группы, отличающеесятем, что с целью расширения области применения за счет возможности последовательного обслуживания запросов, устройство содержит вторую, третью группы элементов И и две 1руппы элементов ИЛИ, причем каждый запросный вход устройства соединен с первым входом одноименного элемента ИЛИ первой группы, выход которогосоеди-нен с единичным входом одноименного разряда первого регистра, нулевой вход каждого разряда первого регистра соединен с выходом одноименного элемента ИЛИ второй группы, вторые входы элементов ИЛИ первой группы соединены с выходами соответствующих элементов И второй группы, первые входы которых соединены с вторым тактовым входом устройства, третий тактовый вход соединен с первыми входами элементов И третьей группы, вторые входы которых соединены с единичными выходами одноименных разрядов второго регистра и с вторыми входами одноименных элементов И второй группы, вход сброса устройства соединен с первьии входами элементов ИЛИ второй группы и с нулевыми входами разрядов второго регистра, нулевые выходы разрядов первого регистра соединены с входами элемента ИЛИ, выход которого является сигналь4i ным выходом устройства, каждый выход которого соединен с выходом одоо ноименного элемента И первой группы, вторые входы элементов ИЛИ второй группы соединены с выходами одноименных элементов и третьей группы

„„SU„„24 07 А

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН

3f59 G 06 F 9 46

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ

t i

% ь ".. ь.: )

К ABTOPGHOMY СВИДЕТЕЛЬСТВУ (21) 3631868/24-24 (22) 12.08.83 (46) 15.11.84. Бюл. В 42 (72) В.A.Àâäååâ и A.È.HåcTåðåíêo (71) Таганрогский радиотехнический институт им. В.Д. Калмыкова (53) 681.325(088.8) (56)1. Авторское свидетельство СССР

9 600557, кл. G 06 F 9/46, 1976.

2.Авторское свидетельство СССР

9 955070, кл. G 06 F 9/46, 1982 (прототип). (54)(57) УСтРОЙСтВО ПРИОРИТЕТА, содержащее два регистра, первую группу элементов И и элемент ИЛИ, причем единичный выход каждого разряда первого регистра соединен с первым входом одноименного элемента И первой группы, выход каждого элемента

И первой группы соединен с единичным входом одноименного разряда второго регистра, вторые входы элементов И первой группы соединены с первым тактовым входом устройства, нулевой выход i-го (i = 1,..., n, — число запросов) разряда первого регистра соединен с соответствующим входом каждого >-го (j= i +1,...,n) элемента И первой группы, о т л ич а ю щ е е с я. тем, что с целью расширения области применения за счет воэможности последовательного обслуживания запросов, устройство содержит вторую, третью группы элементов И и две руппы элементов ИЛИ, причем каждый запросный вход устройства соединен с первым входом одноименного элемента ИЛИ первой группы, выход которого соединен с единичным входом одноименного разряда первого регистра, нулевой вход каждого разряда первого регистра соединен с выходом одноименного элемента ИЛИ второй группы, вторые входы элементов ИЛИ первой группы соединены с выходами соответствующих элементов

И второй группы, первые входы которых соединены с вторым тактовым входом устройства, третий тактовый вход соединен с первыми входами элементов И трстьей группы, вторые вхо- g 2 ды которых соединены с единичными выходами одноименных разрядов второго регистра и с вторыми входами одноименных элементов И второй группы, вход сброса устройства соединен с первьми входами элементов

ИЛИ второй группы и с нулевыми входами разрядов второго регистра, нулевые выходы разрядов первого регистра соединены с входами элемента

ИЛИ, выход которого является сигнальным выходом устройства, каждый выход которого соединен с выходом одноименного элемента И первой группы, вторые входы элементов ИЛИ второй группы соединены с выходами одноименных элементов И третьей группы, 1124307

Изобретение относится к вычислительной технике и может быть исполь зовано в вычислительных системах с приоритетами.

Известно устройство приоритета, содержащее элементы ИЛИ, регистр, две группы элементов И и элемент задержки 11.

Однако быстродействие известного устройства недостаточно.

Наиболее близким к предлагаемому 10 по технической сущности и достигаемому результату является устройство приоритета, содержащее два регистра, генератор импульсов, группу элементов И и элемент ИЛИ, причем единичные входы первого регистра являются входами запросов устройства, выходы которого соединены г. единичными выходами второго регистра, нулевые выходы которого соединены с входами сброса первого регистра(23.

Недостатком этого устройства является узкая область применения.

Цель изобретения — расширение области применения устройства за

25 счет возможности последовательного обслуживания запросов.

Поставленная цель достигается тем, что в устройство приоритета, содержащее два регистра, первую

-группу элементов И и элемент ИЛИ, причем единичный выход каждого разряда первого регистра соединен сединичным входом одноименного разряда второго регистра, вторые входы элементов И первой группы соединены с первым тактовым входом устройства, нулевой выход i -го (i = 1,..., и, — число запросов) разряда первого регистра соединен с соответствующим входом каждого j --го (= +1,..., ) 40 элемента И первой группы, введены вторая, третья группы элементов И и две группы элементов ИЛИ, причем каждый запросный вход устройства соединен с первым входом одноименного 45 элемента ИЛИ первой группы, выход которого соединен с единичным входом одноименного разряда первого регистра, нулевой вход каждого разряда первого регистра соединен с выходом одноименного элемента ИЛИ второй группы, вторые входы элементов ИЛИ перз вой группы соединены с выходами соответствующих элементов И второй группы, первые входы которых соединены с единичными выходами одноименных разрядов второго регистра и с вторыми входами одноименных элементов И второй группы, вход сброса устройства соединен с первыми входами элементов ИЛИ второй группы и с нулевыми входами рязрядов второго регистра, нулевые выходы разрядов первого регистра соединены с входами элемента ИЛИ, выход которого является сигнальным выходом устройства, каждый выход которого соединен ,с выходом одноименного элемента И первой группы, вторые входы элементов ИЛИ второй группы соединены с выходами одноименных элементов

И третьей группы.

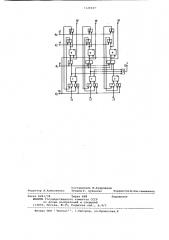

На чертеже приведена структурная схема предлагаемого устройства.

Устройство содержит триггеры 1 первого регистра, элементы И 2 первой группы, элемент ИЛИ 3, тригерры 4 второго регистра, элементы

И 5 второй группы, элементы И б третьей группы, элементы ИЛИ 7 и 8 первой и второй групп соответственно, тактовый вход 9, выходы 10, тактовые входы 11 и 12, запросные входы 13, вход 14 сброса, сигнальный выход

15 устройства.

Работа устройства осуществляется следующим образом.

На вход 14 поступает, сигнал, который устанавливает в нулевое состояние триггеры 1 и 4. Затем выполняется последовательный обход триггеров, находящихся в единичном состоянии. Если триггер 1 имеет единичное значение, то по сигналу, приходящему на вход 9, через элемент

И 2 происходит передача единичного значения триггера 1 в триггер 4.

С поступлением сигнала на тактовый вход 11 осуществляется подключение через элементы И 5 и 2 единичного выхода триггера 4 к нулевому входу триггера 1 и происходит сброс триггера 1 в нулевое состояние. Если еще имеются триггеры из множества в единичном состоянии, то на выходе.

15 сигнал равен 1 и описанная процедура повторяется для следующего триггера 1, находящегося в единичном состоянии. Приоритетный пере.ход от одного триггера к другому реализуется с помощью элементов И

2 и соответствующих их связей с триггерами 1.

B том случае, если осведомительный сигнал на выходе 15 равен 0, то по сигналу, поступающему на вход

12 устройства, производится передача содержимого триггера 4 в триггеры 1, т.е. восстанавливается первоначальное состояние триггеров 1.

Применение изобретения позволяет расширить область применения устройства.

1124307

Составитель М.Кудрявцев

Техред Т ..Пуби нчак КорректорМ.Максимишинец

Редактор Л.Алексеенко

Заказ 8281/38 Тираж 698

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5

Подписное

Филиал ППП Патент, г.Ужгород, ул.Проектная,4