Устройство для восстановления непрерывных функций по дискретным отсчетам

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ ВОССТАНОВЛЕНИЯ НЕПРЕРЫВНЫХ ФУНКЦИЙ ПО ДИСКРЕТНЫМ ОТСЧЕТАМ, содержащее блок вычитания , два цифроаналоговых преобразователя и сдвигающий регистр, управляющий вход которого соединен с первым входом синхронизации устройства, отличающееся тем, что, с целью повьшения точности восстановления непрерывных функций и расширения функциональных возможностей за счет одновременного формирования интерполированных и экстраполированных значений, устройство содержит суммирующий блок и накапливающий сумматор, первая, вторая и третья группы разрядных выходов которого соединены соответственно с первым входом суммирующего блока, с входом первого цифроаналогового преобразователя и с первым входом блока вычитания , второй вход которого соединен с информационным входом устройства, выход блока вычитания соединен с информационным входом сдвигающего регистра , выход которого соединен с информационным входом накапливающего г сумматора и с вторым входом суммирующего блока, выход которого соединен с входом второго цифроаналогового преобразователя, выходы первого и второго цифроаналоговых преобразователей являются выходами устройства, а управляющий вход накапливающего сумматора соединен с вторым входом синхронизации устройства. Ю 11

СОЮЗ ССВЕТСНИХ

О И

РЕСПУблин

g g G 06 G 7/30

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н ABTOPCHOMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОбРЕТЕНИЙ И ОТНРЫТИЙ (21) 3624957/18-24 (22) 21.07.83 (46) 15.11.84. Бюл. № 42 (72) В.Е.Борзых (71) Рязанский радиотехнический институт (53) 681.3(088.8) (56) 1. Авторское свидетельство. СССР

¹ 698012, кл. G 06 G 7/30, 1978.

2. Авторское свидетельство СССР № 627489, кл. G 06 G 7/30, 1978. (54) (57) УСТРОЙСТВО ДЛЯ ВОССТАНОВЛЕНИЯ HEIIPEPbIBHbE ФУНКЦИЙ ПО ДИСКРЕТНЫМ ОТСЧЕТАМ, содержащее блок вычитания, два цифроаналоговых преобразователя и сдвигающий регистр, управляющий вход которого соединен с первым входом синхронизации .устройства, отличающееся тем, что, с целью повышения точности восстановления непрерывных функций и расширения функциональных возможностей за счет одновременного формирования

ÄÄSUÄÄ 1124338 А интерполированных и экстраполированных значений, устройство содержит суммирующий блок и накапливающий сумматор, первая, вторая и третья группы разрядных выходов которого соединены соответственно с первьм входом суммирующего блока, с входом первого цифроаналогового преобразователя и с первым входом блока вычитания, второй вход которого соединен с информационным входом устройства, выход блока вычитания соединен с информационным входом сдвигающего регистра, выход которого соединен с информационным входом накапливающего сумматора и с вторым входом суммирующего блока, вьмод которого соединен с входом второго цифроаналогового преобразователя, выходы первого и второго цифроаналоговых преобразователей являются выходами устройства, а управляющий вход накапливающего сумматора соединен с вторым входом синхронизации устройства.

1124338

Изобретение относится к автоматике, вычислительной и измерительной .технике и может быть использовано для. восстановления непрерывных функций по дискретным отсчетам. 5

Известен линейный интерполятор замкнутого типа, восстанавливающий непрерывную функцию по дискретным отсчетам. Он содержит входной цифро аналоговый преобразователь и замкну 10 тый контур, образованный элементами .сравнения, блоком памяти с ключами записи-считывания, масштабирующим . блоком и интегратором 1).

Недостаток этого устройства за- 15 ключается в невысокой точности, обусловленной наличием аналоговых интеграторов, и в ограниченных функциональных возможностях, связанных с тем, что схема интерполятора не 20 позволяет получать одновременно и экстраполированные значения функции, что бывает необходимо для качественной работы системы управления, которые он обслуживает. 2S ,Наиболее. близким к предлагаемому является устройство для восстановления непрерывных функций по дискретным отсчетам, содержащее цифроаналоговый блок умножения, .два цифроаналоговых преобразователя, блок вычитания, регистр кода упрежденного значения аргумента и два сдвигающих регистра, .один вход первого сдвигающего регистра подключен к входу ор- 35 динат восстанавливаемой функции, второй вход соединен с входом синхронизации устройства, а выход соединен с входом первого цифроаналого- вого преобразователя, с одним из вхо-40 дов блока вычитания и с входом второго сдвигающего регистра, выход которого соединен с другим входом блока вычитания, выход которого соединен с входом второго цифроаналогового 45 преобразователя, выход которого соединен с первым входом цифроаналогового блока умножения, второй и третий входы .этого блока соединены, соответственно, с выходом первого 50 цифроаналогового преобразователя и с выходом регистра кода упрежденного значения аргумента. Восстановление непрерывной функции осуществляется методом ступенчато-линейной экстра-,у поляцин. Это позволяет сформировать выходной сигнал практически без задержки относительно исходного сигна ла. В схеме устройства отсутствует аналоговый интегратор, следовательно, оно характеризуется меньшей величиной инструментальной погрешности f2).

Однако такое устройство имеет существенный недостаток, заключающийся в том, что процесс восстановления непрерывных функций, вторая производная которых не равна нулю, характеризуется появлением значитель- . ной методической составляющей погрешности. Это обусловлено экстраполяционным способом восстановления, методическая погрешность которого ,в большинстве случаев больше соответствующей погрешности интерполяционного способа.

Таким образом, выходной сигнал, формируемый в известном устройстве, характеризуется, с одной стороны, малой величиной времени задержки, а с другой стороны, низкой точностью восстановления. Наличие значительной погрешности не позволяет в большинстве случаев использовать этот сигнал для целей измерения и регистрации информации. Следовательно, известное устройство характеризуется низкой точностью и узкими функциональными возможностями.

Цель изобретения — повышение точности восстановления и расширение функциональных возможностей устройства эа счет одновременного формирования интерполированных и экстраполированных значений.

Указанная цель достигается тем, что устройство для восстановления непрерывных функций по дискретным отсчетам, содержащее блок вычитания, два цифроаналоговых преобразователя и сдвигающий регистр, управляющий вход которого соединен с первым входом синхронизации устройства, содержит суммирующий блок и накапливающий сумматор, первая, вторая и третья группы разрядных выходов которого соединены соответственно с первым входом суммирующего блока, с входом первого цифроаналогового преобразователя и с первым входом блока вычитания, второй вход которого соединен с информационным входом устройства, выход блока вычитания соединен,. с информационным входом сдвигающего регистра, выход которого соединен с информационным входом накапливающе.

1124338 го сумматора и с вторым входом суммирующего блока, выход которого соединен с входом второго цифроаналогового преобразователя, выходь первого и второго цифроаналогового 5 преобразователей являются. выходами устройства, а управляющий вход накапливающего сумматора соединен с вторым входом синхронизации устройства. 10

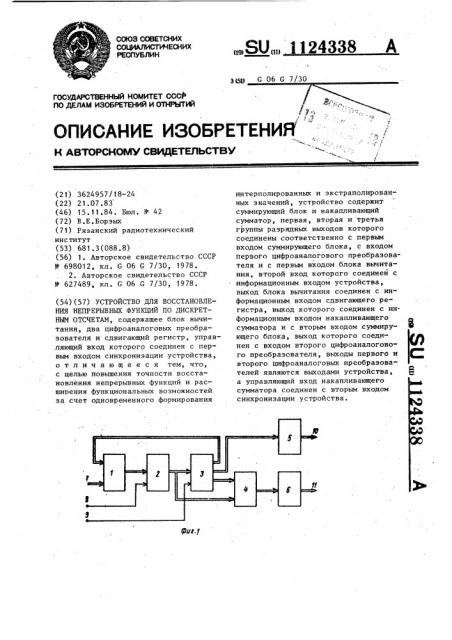

На фиг. 1 представлена блок-схема предлагаемого устройства; на фиг.2— временные диаграммы, поясняющие принцип действия устройства. 15

Устройство содержит блок вычитания 1, сдвигающий регистр 2, накапливающий сумматор 3, суммирующий блок 4,, цифроаналоговые преобразователи 5 и 6. Позицией 7 обозначен 20 вход ординат восстанавливаемой функции устройства (информационный вход), позициями 8 и 9 обозначены, соответственно, первый и второй входы синхронизации устройства, позициями 10 21 и 11 — выходы устройства.

Ординаты восстанавливаемой функции закодированы М-разрядным параллельным кодом, моменты поступления которого на вход 7 совпадают с момен-30 тами поступления импульсов синхронизации на вход 8. Ординаты, соответствующие положительным значениям функции, представлены в прямом коде, а ординаты, соответствующие отрицательным значениям функции, представлены в дополнительном коде. В сдвигающем регистре запоминается код разности, двух соседних ординат восстанавливаемой функции. Накапливающий 40 сумматор содержит в общем случае

М+М разрядов, где М вЂ” число дополни.тельных разрядов, определяемое допустимой погрешностью аппроксимации отрезков прямых линий ступенчатоломаной кривой. Обычно М определяется из уравнения 2 =К, где К вЂ” число

М тактов суммирования на интервале аппроксимации. Суммирование осуществляется в моменты поступления на вход 9 импульсов синхронизации. Частота этих импульсов должна быть в

К раз больше частоты импульсов, поступающих на первый вход 8 синхронизации.

Моменты поступления импульсов на входы 7 и 8 не должны совпадать.

Накапливаемый сумматор имеет три группы выходов. Номера выходов в каждой группе отсчитываются относительно старшего разряда. Первая, вторая и третья группы включают, соответственно, и, N и М выходов старших разрядов йакапливающего сумматора, причем N,.g Н+М, i =1,2,3.

Выбор конкретных значений N< и Й зависит от числа разрядов цифроаналоговых преобразователей. В предельном случае, когда Ni = N2=N+N, аппроксимация отрезков прямых линий осуществляется наиболее точно (в этом случае отсутствует погрешность округления в блоке накапливающего сумматора). Значение N обычно равно М .

На выходах второй группы накапливающего сумматора 3 формируются коды, соответствующие значениям функции, восстановленной методом ступенчато-линейной интерполяции.

Эти коды преобразуются в блоке 5 в аналоговые сигналы, представленные в виде тока и напряжения.

На выходе суммирующего блока 4 формируются коды, соответствующие значениям функции, восстановленной методом ступенчато.-линейной экстраполяции, а преобразователь 6 преобразует эти коды в соответствующие аналоговые сигналы.

Используемые в устройстве цифроаналоговые преобразователи предназначены для преобразования двоичных кодов любого знака в двухполярные аналоговые сигналы.

Рассмотрим принцип действия устройства на примере формирования импульсных переходных функций.

Пусть N„=N =N =К=8 М=З. В этом

1 2 3 случае накапливающий сумматор содержит 11 двоичных разрядов. Сигналы с выхода сдвигающего регистра 2 подаются на входы восьми мпадших разрядов накапливающего сумматора 3.

Три групйы выходов накапливающего сумматора 3 объединяются в одну группу выходов (это справедливо только в рассматриваемом частном случае), снимаемых с восьми старших разрядов блока.

В исходном состоянии накапливающий сумматор 3 и сдвигающий регистр

2 обнулены, поэтому по цепи обратной связи на первый вход блока вычитания 1 поступает код, равный нулю.

S 11

После того, как на вход 7 чстройства поступает параллельный код, соответствующий одиночному отсчету, амплитуда которого равна, например, восьми условным единицам, на выходе блока вычитания 1 появляется код разности между входным кодом и кодом на выходе накапливающего сумматора

3. В момент т„ поступления на вход

8 импульса сийхронизации (фиг.2 e) в сдвигающий регистр записывается код разности 00001000. Это значение кода разности сохраняется в блоке 2 до момента 1 поступления следующего импульса синхройизации на вход 8 устройства.

В момент „ поступления на вход 9 импульса синхронизации (фиг.2 б), код, .хранящийся в сдвигающем регист ре, переписывается в накапливающий сумматор 3. На выходе этого блока образуется кол 00000001. Таким образом, в блоке 3 происходит деление значения полученной разности на

8, (а в общем случае на 2 ). Это

М объясняется тем что входные сигналы подаются на восемь младших разрядов, а выходные сигналы снимаются с восьми старших разрядов блока накапливающего сумматора. С поступле нием следующих импульсов синхронизации на вход 9 устройства значение кода накапливающего сумматора возрастает по линейному закойу. С выхода блока 3 значения кодов подаются на цифроаналоговый преобразователь 5, в котором происходит преобразование последовательности кодов в возраста ющий ступенчато-линейный аналоговый сигнал. Так происходит формирование первого участка импульсной переходной функции устройства по выходу 10.

В момент Ф „ поступления восьмого им-. пульса синхронизации на вход 9 амплитуда сигнала на выходе 10 достигает максимального значения, соответствуощего восьми единицам.

В момент 1 на вход 8 устройства подается следующий импульс синхронизации. В этот момент на входе 7 устройства значение кода равно нулю, а на первый вход блока вычитания 1 подается код, соответствующий восьми единицам. Следовательно, в сдвигающий регистр 2 записывается новое значение кода разности равное восьми единицам. Полученное значение разнос. ти сохраняется до момента t . В мо24338

50 где 4.1-ФФ -То.

f5

35 мент :„содержимое блока накапливающего сумматора уменьшается на.одну единицу, в момент . — на две единигг. цы и т.д. В момент.1 накапливающий сумматор 3 обнуляется. Уменьшающиеся по линейному закону значения кодов преобразуются в блоке 5 в уменьшающийся по амплитуде ступенчато-линейный аналоговый сигнал. Так формируется второй участок импульсной переходной функции устройства по выходу 10.

В момент „ на двух входах блока вычитания значения кодов равны нулю, поэтому в блоке 2 записываетс:. нулевое значение разности. Следовательно, вся схема возвратилась в исходное состояние.

Таким образом, на выходе 10 устройства формируется .импульсная пере хадная функция (фиг.2 ff), имеющая вид равнобедренного треугольника, стороны которого образованы методом ступенчатой аппроксимации отрезков прямых. Длительность по основанию этого треугольника равна 2 Т., где о

Тр — период следования импульсов синхронизации по входу 8. Высота треугольника пропорциональна значению входного кода устройства. Следовательно, при периодическом поступлении на вход 7 устройства кодов дискретных отсчетов на выходе цифроаналогового преобразователя 5 сигнал восстанавливается методом ступенча- . то-линейной интерполяции дискретных отсчетов.

Рассмотрим методику восстановления сигнала на выходе 11 устройства.

На выходе сумматора 4 образуется текущая сумма значений кодов, снимаемых с выходов блока накапливающего сумматора 3 и сдвигающего регистра 2. На отрезке (Ф„р,1 1 эта сумма

10! го изменяется от значения +8 до значения +16, а на отрезке tt«, р)- от значения 0 до значения 8. Йа выходе цифроаналогового преобразователя 6 формируется импульсная переходная функция, изображенная на фиг.2 ъ .

Анализ показывает, что эта функция получена методом ступенчатой аппроксимации импульсной переходной функции линейного экстраполятора вида

8(1+1 Тоi для Ос «(То, -: И1 = % If%„ /Тр ) для 0(+„4Т

0 для остальных знлчений

1124338

Следовательно, на выходе цифроаналогового греобразователя б восстановление непрерывной функции осуществл яется методом ступенчато-линейной

5 экстраполяции.

П инципиальное отличие предлагаер мого устройства от известных заключается в более высокой точности восстановления сигнала методом ступенчато-линейной интерполяции на д выхо е 1О

10.

Наличие двух выходов в предлагаемом устройстве расширяет его функциональные воэможности. Например, 15 сигнал с в с выхода 11 можно использовать в качестве сигнала обратной связи в замкнутых импульсных системах. Из" вестно,что наличие экстраполятора в сис- теме йозволяет улучшить ее динамические характеристики. Сигнал, снимаемый с выхода 10, восстановлен ме тодом интерполяции, поэтому имеет за. держку относительно исходного сигнала, однако методическая составляющая погрешности, обусловленная переходом от метода экстраполяции к методу интерполяции уменьшается при этом в 8 раз. Этот сигнал можно использовать для целей регистрации информации на различных носителях.

Технико-экономический эффект от использования изобретения заключает"я в повышении точности восстановления непрерывных функций и расширении функциональных возможностей устройства.

Il24338

ВЩЗШК Заказ 8284/40 ТнФаа 698 Зоаисзюе

4ааиаа ВШ Ъатаат", а Мйвщед,эй.йвееаюм, 4