Импульсный частотно-фазовый детектор

Иллюстрации

Показать всеРеферат

ИМПУЛЬСНЫЙ ЧАСТОТНО-ФАЗОВЫЙ ДЕТЕКТОР, содержащий первый, второй, третий и четвертый D -триггеры, два блока задержки, входы каждого из коTopi соединены соответственно с входами синхронизации первого и второго 3) -триггеров, два элемента ШШ и интегратор, выход которого является выходом импульсного частотно-фазового детектора, причем инверсные выходы первого.и второго . D триггеров соединены соответственно с D -входами второго и первого 3) -триггеров,а входы синхронизации первого и второго 3)-тиггеров соединены с источниками входных сигналов и подключены соответственно к R -входам второго и первого D -триггеров, отличающий с я тем, что, с целью упрощения , входы интегратора соединены с выходами элементов ШШ, первые входы которых соединены соответственно с прямыми выходами третьего и четвертого D -триггеров, а вторые входы соединены соответственно, с -входами третьего и четвертого D -триггеров, 9 вхрды синхронизации которых соединеш соответственно с выходами первого и второго блоков задержки, при этом прямой выход первого D -триггера соединен cD -входом третьего D триггера , а прямой выход второго D триггера соединен с р -входом четвертого D -триггера.

СОЮЗ СОВЕТСКИХ йй,И ЛЮ ЕСПУБЛИК,.SU„„1124424 A

Зц9 Н 03 3 13/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОЬРЕТЕНИЙ И ОТКРЫТИЙ (21) 3596612/18-09 (22) 26 .05.83 (46) 15.11.84. Бюл. 42 (72) И.В.Колосов, И.П.Корнилов и А.В.Колосов (53) 621.376.6(088."В) (56) 1. Авторское свидетельство СССР

9985929, кл. Н 03 3 13/00, 08.10.80.

2. Авторское свидетельство СССР по заявке 1059662,3483051/18-09, кл. Н 03 3 13/00, 17.08.82 (прототип). (54)(57) ИМПУЛЬСНЫЙ ЧАСТОТНО-ФАЗОВЫЙ

ДЕТЕКТОР, содержащий первый, второй, третий и четвертый П -триггеры, два блока задержки, входы каждого иэ которых соединены соответственно с, входами синхронизации. первого и второго 3 -триггеров, два элемента ИЛИ и интегратор, выход которого является выходом импульсного частотно-Aasosoro детектора, причем инверсные выходы первого.и второго . 2 -триггеров спединены соответственно с 3 "входами второго и первого 3 -триггеров, а входы синхронизации первого и второго

2-тиггеров соединены с источниками входных сигналов и подключены соот- . ветственно к К -входам второго и первого Р -триггеров, о т л и ч а юшийся тем, что, с целью упрощения входы интегратора соединены с выходами элементов ИЛИ, первые входы которых соединены соответственно с прямыми выходами третьего и четвертого D -триггеров, а вторые входы соединены соответственно с Р -входами третьего и четвертого D -триггеров, входы синхронизации которых соединены В соответственно с выходами первого и второго блоков задержки, при этом прямой выход первого Р -триггера соединен cD -входом третьего D триггера, а прямой выход второго 9 - Я триггера соединен с g -входом четвертого Э -триггера.

1124424

Изобретение относится к радиотехнике и может использоваться в быстродействующих схемах фазовой автоподстройки частоты с малым уровнем частот, кратных частоте следования.

Известен импульсный частотно-Аазовый детектор, содержащий два 3 триггера и интегратор, входы которого соединены соответственно с прямым. выходом первого 3 -триггера и инверс-1О ным выходом второго 3 -триггера, а выход интегратора является выходом устройства, при этом входы синхронизации каждого из 3 -триггера являются входами устройства и соединены l5

Ф соответственно с входом установки в ноль другого Я -триггера, инверс ный выход первого 3 -триггера соединен с информационным 3 -входом второго 33 -триггера, а инверсный 20 выход второго П -триггера — с информационным Х) -входом первого2 триггера (1) .

Однако известный импульсный частотно-фазовый детектор имеет низкое 25 быстродействие, обусловленное импульсной подстройкой частоты и фазы при любом сдвиге фаз между опорной и подстраиваемой частотами.

Наиболее близким техническим ре- 30 шением к предложенному является ийпульсный частотно-фазовый детектор, содержащий первый, второй, третий и четвертый О -триггеры, два блока задержки входы каждого из которых 35 соединены соответственно с входами синхронизации первого и второго 3 триггеров, два элемента ИЛИ и интегратор, выход которого является выходом импульсного частотно-фазового детектора, причем инверсные выходы первого и второго D -триггеров соединены соответственно с 3 -входами второго и первого D -триггеров, а входы синхронизации первого и вто- 45 рого D -триггеров соединены с источниками входных сигналов и подключены соответственно к R -входам вто- . рого и первого О -триггеров, третий и четвертый D -триггеры входят в состав двух дополнительных каналов обработки, включенных между выходами элементов ИЛИ и входами интегратора f?);

Однако известный импульсный частотно-фазовый детектор имеет довольно. 55 сложную схему.

Цель изобретения — упрощение импульсного частотно-фазового детектора;

Поставленная цель достигается тем, что в импульсном частотно-фазовом детекторе, содержащем первый, второй, третий и четвертый 2 -триггеры, два блока задержки, входы каждого из которых соединены соответственно с входами синхронизации первого и второго 0 -триггеров, два элемента ИЛИ и интегратор, выход которого является выходом импульсного частотно-фазового детектора, причем инверсные выходы первого и второго 2 триггеров соединены соответственно с 3 -входами второго и первого D триггеров, а входы синхронизации первого и второго D -триггеров соединены с источниками входных сигналов и подключены соответственно к 8 -входам второго и первого 2 триггеров, входы интегратора соединены с выходами элементов ИЛИ, первые входы которых соединены соответственно с прямыми выходами тре-, тьего и четвертого D -триггеров, а вторые входы соединены соответственно с З -входами третьего и четвертого 2 -триггеров, входы синхронизации которых соединены соответственно с выходами первого и второго блоков задержки, при этом прямой выход первого 2 -триггера соединен с Ю -входом третьего З -триггера, а прямой выход второго О -триггера соединен с 3 -входом четвертого

3-триггера.

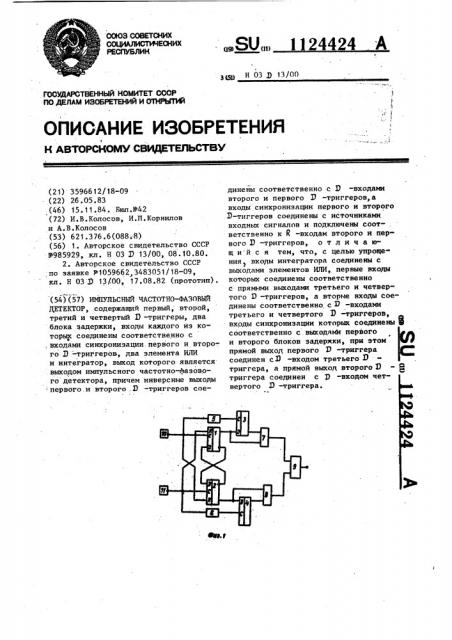

На фиг.1 приведена структурная электрическая схема предложенного импульсного частотно-фазового детектора; на фиг.2 - эпюры напряжений, поясняющие его работу.

Импульсный частотно-фазовый детектор содержит первый -четвертый

D "триггеры. 1-4, два блока 5 и 6 задержки, два элемента ИЛИ 7 и Я, интегратор 9 источники 10 и 11 входных сигналов.

Импульсный частотно-фазовый детектор работает следующим образом.

С источника 10 поступает, например, частота Fi (фиг.2а), с источника 1 1 — частота F() (фиг,26) . Я исходном состоянии на выходах З -триггерон 1-4 и выходах элементов HJIH 7 и 8 присутствует напряжение логического нуля. Пусть частота " опережает по фазе частоту à тогда фронтом первого импульса частоты F D триггер 1 переключается в состояние

1124424 4 улду F(и Fo больше! ° 2 q (то2 ° л логической единицы, и на выходе элемента ИЛИ 7 появляется также уровень логической единицы, причем если разность фаз между F, и F больше л л и — 24> где ь — время задержки в блоке 5 задержки, а Т вЂ” период опорной частоты, то 3 -триггер 3 также переключается в состояние логической единицы, в котором находится до тех пор, пока разность фаз между Г< и F л больше .2, При этом на выходе то элемента ИЛИ 7 также присутствует напряжение логической единицы, пока а(у r — 2Я (фиг.2в). При 4(р (— 2»

С, I5 т, о импульсы частоты Г» переключают в единичное состояние только триггер 1, а импульсы частоты Г в нулевое состояние, при этом З вЂ” 20 триггер 3 остается в нулевом состоянии, и на выходе элемента ИЛИ 7 появляются импульсы, длительность которых пропорциональна фазовой раз:ности частот F, и F ., Причем пока 25 частота Fi + F либо при опережении по фазе частоты Fi при F, = F на выходе элемента ИЛИ 8 поддерживается уровень логического нуля, поскольку 3 -триггеры 2 и 4 находятся в состоянии логического нуля. Напряжение на выходе элемента

ИПИ 7 интегрируется в интеграторе

9 (фиг.2г),напряжение на выходе интегратора 9 увелИчивается- до тех пор, пока не наступит синфазный режим, при этом на выходах элементов

ИЛИ 7 и 8 присутствует напряжение логического нуля. Эти сигналы удерживают интегратор 9 в- закрытом сас- 1 тоянии, при котором напряжение на выходе остается постоянным и пуль- сации напряжения отсутствуют.

Пусть теперь частота Fq (фиг.2д). отстает по фазе от частоты Г 45

-(фиг.2е), тогда фронтом первого импульса частоты о 2 -триггер 2 переключается в состояние логической единицы, и на выходе элемента ИЛИ Я .пбявляется также уровень логической 5О единицы, причем если разность фаз триггер 4 также переключается в сос тояние логической единицы, в котором находится до тех пор, пока раз л ность фен мешду F< н Го больше - )i

4ю

На выходе элемента ИЛИ 8 также присутствует напряжение логической еди»

Ъ ницы (AHI .2æ) ° При 5p c) —" ° 2« H5f» ! а пульсы частоты Го переключают . в единичное состояние только Р -триггер

2, а импульсы частоты Г» в нуле-. вое состояние, при этом 2 -триггер

4 остается в нулевом состоянии, и на выходе элемента ИЛИ 8 появляются импульсы, длительность которых пропорциональна фазовой разности частот Г, и Г„. Причем пока F1 Fj4 либо при опережении по фазе частоты при F на выходе элемента

ИЛИ 7 поддерживается уровень логического нуля, поскольку Я -триггеры

1 и 3 находятся в состоянии логического нуля. Напряжение на выходе элемента ИЛИ Я поступает на другой вход интегратора 9, при этом напряжение на выходе интегратора 9 уменьшается (фиг.2з) до тех пор, пока не наступит синфазный режим.

По сравнению с базовым объектом предлагаемый импульсно) частотнофазовый детектор имеет большее быстродействие, поскольку на выходе одного из элементов ИЛИ в зависимости от знака разности частот или фаз поддержйвается уровень логической единицы все время, пока bq 1-" 2»! и выходное напряжение быстрее достигает уровня, при котором наступает режим синхронизации. В результате значительного упрощения схемы предложенный импульсный частотно-фазовый детектор по сравнению с прототипом при одинаковом быстродействии имеет более низкую себестоимость.

1124424

Составитель И. Грабилин

Редактор Л. Веселовская Техред Т.Иаточка Корректор Г. Решетник

Заказ 8297/44 Тираж 861

ВНИИПИ Государственного комитета ГССР по делам изобретений и открытий !

13035, Москва, Ж-35, Раушская наб., д. 4/5

Подписное

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4