Преобразователь кода в коды функций

Иллюстрации

Показать всеРеферат

1. ПРЕОБРАЗОВАТЕЛЬ КОДА В КОДЫ ФУНКЦИЙ, содержащий первый сумматор, одни входы которого соединены с выxoдa ш источника кода смещения фаз, первое запоминающее устройство , отличающийся тем, что, с целью повышения быстродействия , в него введены дополнительные сумматоры и дополнительные запоминающие устройства, входы первого запоминающего устройства и другие входы первого сумматора являются входами преобразователя кода в коды функщгй, одни входы дополнительных сумматоров соединены с выходами источника кода смещения фаз, выходы каждого дополнительного сумматора подключены к входам соответствующего зaпo инaющeгo устройства и к другим входам последующего сумматора , а выходы первого сумматора подключены к входам первого дополнительного запоминающего устройства и к другим входам первого дополнительного сумматора.

СОЮЗ СОВЕТСКИХ

РЕСПУБЛИК .

„„SUÄÄ 11244 зсю Н 03 К 13/24

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ:

К ABTOPCHOMV СВИДЕТЕЛЬСТВУ (21) 3629542/24-24 (22) 28.07.83 (46) 15. 11. 84. Бюл. И 42 (72) В.Ф. Голопятов, И.А. Егоров и О.Е. Чеботаев (53) 681 . 382 (088. 8) (56) 1. Авторское свидетельство СССР

У 622202, кл.. Н 02 К 13/24, 1977 г.

2 ° Авторское свидетельство СССР по заявке В 3619805-24-24, кл. С 08 С 9/00, 13.07.83 (прототип). (54) (57) 1. ПРЕОБРАЗОВАТЕЛЬ КОДА

В КОДЫ ФУНКЦИЙ, содержащий первый сумматор, одни входы которого соединены с выходами источника кода смещения фаз, первое запоминающее уст.. ройство, отличающийся

) тем, что, с целью повышения быстродействия, в него введены дополнительные сумматоры и дополнительные запоминающие устройства, входы первого запоминающего устройства и другие входы первого сумматора являются входами преобразователя кода в коды функций, одни входы дополнительных сумматоров соединены с выходами источника кода смещения фаз, выходы каждого дополнительного сумматора подключены к входам соответствующего запоминающего устройства и к другим входам последующего сумматора, а выходы первого сумматора подключены к входам первого допол. Е нительного запоминающего устройства и к другим входам первого дополнительного сумматора.

11244 32

2. Преобразователь по п.,1, о тл и ч а ю шийся тем, что sanoминающее устройство содержит первый и второй суйматоры по модулю два, блок постоянной памяти и инвертор, одни входы второго сумматора по модулю два и вход инвертора являются входом запоминающего устройства, соответствующим старшему разряду коДа, а выход инвертора является выходом первого разряда запоминающего устройства, одни входы первого сумматора по модулю два являются входом запоминающего устройства, Изобретение относится к автоматике и вычислительной технике и может быть использовано в преобразователях перемещения в код следящего уравновешивания. 5

Известен преобразователь кода, содержащий генератор импульсов, счетчик, элементы И, одновибраторы, накопитель, дешифратор и запоминающее устройство (1).

Недостатком такого преобразователя кодов является низкое быстродей ст вне.

Наиболее близким к предлагаемому по техническому решению является преобразователь кода в коды функций, содержащий один сумматор, одни входы которого соединены с выходами источника кода смещения фаэ, одно запоминающее устройство, входной регистр, выходные регистры, последовательно соединенные генератор импульсов, счетчик и дешифратор, выходы которого подключены к управляющим входам выходных регистров, входы преобразователя подключены к первым информационным входам входного

-регистра, первый управляющий вход которого соединен с первым выходом дешифратора, вторые, информационные ЗО входы соединены с выходом одного сумматора, второй управляющий вход соединен с выходом генератора импульсов, выходы входного регистра подключены к другим входам суммато" З ра и к входам запоминающего устройсоответствующим предпоследнему старшему разряду кода, другие входы первого сумматора по модулю два являются входами запоминающего устройства, соответствующими остальным разрядам кода, а выходы первого сумматора по модулю два подключены к блоку постоянной памяти, выходы которого подключены к другим входам второго сумматора ло модулю два, выходы второго сумматора по модулю два являются выходами младших разрядов устройства. ства, выходы которого подключены к информационным входам выходных регистров (21 .

В известном устройстве преобразование кода в коды функций каждой фазы происходит последовательно.

Недостатком известного устройства является малое, быстродействие.

Цель изобретения — повышение быстродействия преобразователя.

Поставленная цель достигается тем, что в преобразователь кода в коды функции, содержащий первый сумматор, одни входы которого соединены с выхрдами источника кода смещения фаз, первое запоминающее устройство, введены дополнительные сумматоры и дополнительные запоминающие устройства, входы первого запоминающего устройства и другие входы первого сумматора являются входами преобразователя кода в

1 коды функций; одни входы дополнительных сумматоров соединены с выходами источника кода смещения фаз, выходы каждого дополнительного сумматора подключены к входам соответствующего запоминающего устройства и к другим входам последующего сумматора, а выходы первого сумматора подключены к входам первого дополнительного запоминающего устройства и к другим входам первого дойолнительного сумматора.

Запоминающее устройство содержит первый и второй сумматоры по модулю

432

1124 з два, блок постоянной памяти и инвертор, одни входы второго сумматора по модулю два и вход инвертора являются входом запоминающего устройства, соответствующим старшему раз,ряду кода, а выход инвертора является выходом первого разряда запоминающего устройства, одни входы первого сумматора по модулю два являются входом запоминающего устройства, со- 10 ответствующим предпоследнему старшему разряду кода, другие входы первого сумматора по модулю два являются входами запоминающего устройства, соответствующими остальным разрядам кода, а выходы первого сумматора по модулю два подключены к блоку постоянной памяти, выходы которого подключены к другим входам второго сумматора по модулю два, выходы вто- 2О рого сумматора по модулю два являются sbixîäàèè младших разрядов устройства.

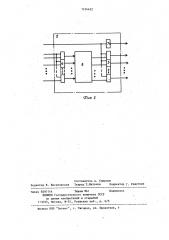

На фиг. 1 представлена структур- . ная схема преобразователя; на 25 фиг. 2 — структурная схема запоминающего устройства.

Преобразователь содержит сумматоры 1, выходы которых подключены к входам запоминающих устройств 2, одни входы сумматоров 1 соединены с выходами источника 3 кода смещения фаз, входы. преобразователя подключены к входам одного иэ сумматороВ и одного иэ запоминающих уст .ройств 2, выходы каждого сумматора подключены к другим входам соседнего сумматора.

Запоминающее устройство 2 содержит первый 4 и второй .5 сумматоры по модулю два, блок 6 постоянной памяти и инвертор 7, вход устройства 2, соответствующий старшему pasряду кода, подключен к одним входам сумматора 5 по модулю два и через 41 инвертор 7 — к выходу первого разряда устройства 2, вход устройства 2, соответствующий предпоследнему старшему разряду кода, подключен к одним входам первого сумматора 4 по, модулю два, другие входы которого соединены с входами устройства 2, соответствующими остальным младшим разрядам кода, а выходы сумматора 4 по модулю два подключены к блоку 6 постоянной памяти, выходы которого подключены к другим входам второго сумматора 5 по ..модулю два, выходы сумматора 5 подключены к выходам младших разрядов устройства.

Преобразователь работает следующим образом.

В первом сумматоре 1 производится сложение входного кода с кодом источника 3. В каждом последующем сумматоре 1 производится сложение выходного кода предыдущего сумматора 1 с кодом источника 3. Величина кода источника 3 соответствует смещению по фазе между выходными кодами преобразователя. Выходные коды каждого из сумматоров 1 представляют собой адрес числа ° хранящегося в запоминающих устройствах

2. При наличии единицы в старшем разряде входного кода эапоминающего устройства 2 выходной код блока

6 инвертируется в сумматоре 5, а при наличии единицы в предпоследнем старшем разряде инвертируются остальные младшие разряды входного кода запоминающего устройства 2 в сумматоре 4..Это позволяет выполо нить блок 6 для углов от 0 до 90

В предлагаемом преобразователе происходит одновременное формирование кодов функций на всех выходах, что увеличивает быстродействие по сравнению с известными преобразователями..

1124432

Ч- Ъ8. 2

Составитель А. Смирнов

Редактор В. Веселовская Техред Т.Маточка Корректор Г. Решетник Заказ 8297/44 Тираж 861 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4