Устройство для блочной синхронизации цифровой системы передачи

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ БЛОЧНОЙ СИНХРОНИЗАВДИ ЦИФРОВОЙ СИСТЕМЫ ПЕРЕДАЧИ, использующей многоуровневые коды с избыточностью, содержащее регистр сдвига, выходы которого подключены к соответствующим входам детектора запрещенных слов, . а также последовательно соединенные делитель частоты на два и умножитель частоты на три, при этом первый , второй и третий входы регистра сдвига являются входами устройства, причем тоетий вхоп регистра сдвига объединен с входом делителя частоты на два, отличающе-еся тем, что, с целью повышения помехоустойчивости передачи информации, . уведены кольцевой счетчик на три, первый, второй, третий и четвертый синхронизируемые кольцевые счетчики на четыре, блок задержки импульсов и блок детектирующей логики, содержащий первый, второй и третий двухвходовые элементы И и трехвкодовый элемент ИЛИ, выход которого через блок задержки импульсов подключен к первому входу четвертого синхронизируемого кольцевого счетчика на четьфе, второй вход которого объединен с третьим входом регистра сдвига .и первыми входами первого, второго и. третьего синхронизируемых кольцевых счетчиков на четыре, к вторым входам которых подключены выходы кольцевого Счетчика на три, к входу которого подключен выход детектора запрещенных слов, при этом выход (О первого синхронизируемого кольцевого счетчика на четыре подключен к первым входам первого и третьего двухвходовых элементов И, выход второго синхронизируемого кольцевого счетчика на четыре прдключен к второму входу первого двухвходового элемента И и первому входу второго двухвходового элемента И, а вьвсод третьегосинхронизируемого кольцевого счетчика на четыре подключен к вторым входам второго и третьего двухвходовых элементов И, выходы которых, а также выход первого двухвходового элемента И подключены к входам трехвходового элемента ИЛИ.

ИМОЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

-SU„„ f244 з(5и H 04 L 7/02

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

hO ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н ABTOPCHOMV СВИДЕТЕЛЬСТВУ (21) 3576072/18-09 (22) 04. 04. 83 (46) 15. 11.84. Бюл. У 42 (72) А.Ю. Лев, Г.С. Маркарян, E.È. Парфенов и Е.Е. Покропивный (71) Одесский электротехнический институт связи им. А.С. Попова (53) 621.394.662(088.8) (56) 1. Стиффлер Дж.Дж. Теория синхронной связи. М., "Связь", 1975, с. 326-33 1.

2 ° Патент Великобритании

У 1564085, кл, Н 4 Р, 1980 (прототип) .. (54)(57) УСТРОЙСТВО ДЛЯ БЛОЧНОЙ

СИНХРОНИЗАЦИИ ЦИФРОВОЙ СИСТЕМЫ ПЕРЕДАЧИ, использующей многоуровневые коды с избыточностью, содержащее регистр сдвига, выходы которого подключены к соответствующим входам детектора запрещеннъ1х слов, а также последовательно соединенные делитель частоты на два и умножи тель частоты на три, при этом первый, второй и третий входы регистра сдвига являются входами устройства, причем тоетий вхоп региства сдвига объединен с входом делителя частоты на два, о т л и ч а ю щ е е с я тем, что, с целью повышения помехоустойчивости передачи информации, введены кольцевой счетчик на три, первый, второй, третий и четвертый синхронизируемые кольцевые счетчики на четыре, блок задержки импульсов и блок дстектирующей логики, содер-! жащий первый, второй и третий двухвходовые элементы И и трехвходовый элемент ИЛИ, выход которого через блок задержки импульсов подключен к первому входу четвертого синхронизируемого кольцевого счетчика на четыре, второй вход которого объединен с третьим входом регистра сдвига и первыми входами первого, второго и. третьего синхронизируемых кольцевых счетчиков на четыре, к вторым входам которых подключены выходы кольцевого счетчика на три, к входу которого подключен выход детектора запрещенных слов, при этом выход первого синхронизируемого кольцевого счетчика на четыре .подключен к первым входам первого и третьего двухвходовых элементов И, вь1ход второго синхронизируемого кольцевого счетчика на четыре прдключен к второму входу первого двухвходового элемента И и первому входу второго двухвходового элемента И, а вькод третьего синхронизируемого кольцевого счетчика на четыре подключен к вторым входам второго и третьего двухвходовых элементов И, выходы которых, а также выход первого двухвходового элемента И подключены к входам трехвходового элемента

ИЛИ.

1124438

15

25

Изобретение относится к технике электрической связи и может быть использовано в цифровых системах передачи, применяющих многоуровневые блочные балансные коды с избыточностью.

Известно устройство блочной синхронизации кодов, в котором для осуществления синхронизации используются запрещенные комбинации, появляющиеся на каждом стыке кодовых слов f1) .

Недостатком известного устройства является избыточность кода, приводящая к низкой экономической эффективности цифровой системы передачи.

Наиболее близким к предлагаемому по техническому решению является устройство для блочной синхронизации цифровой системы передачи, использующей многоуровневые коды с избыточностью, содержащее регистр сдвига, выходы которого подключены к соответствующим входам детектора запрещенных слов, а также последовательно соединенные делитель частоты на два и умножитель частоты на три, при этом первый, второй и третий входы регистра сдвига являются входами устройства, причем третий вход регистра сдвига объединен с входом делителя частоты на два, а также, детектор нарушений, блок расширения импульсов, двоичный счетчик на восемь, кольцевой счетчик на четыре, четыре одновибратора, синхронизирующий блок, блок памяти фазы, четыре элемента ИЛИ-НЕ (2) .

Однако известное устройство обладает низкой помехоустойчивостью.

Цель изобретения — повьппение помехоустойчивости передачи информа" ции, Поставленная цель достигается тем, что в устройство для блочной синхронизации цифровой системы передачи, использующей многоуровневые коды с избыточностью, содержащее регистр сдвига, выходы которого подключены к соответствующим входам детектора запрещенных слов, а также последовательно соециненные делитель частоты на два и умножитель частоты на три, при этом первый, второй и третий входы регистра сдвига являются входами устройства, причем третий вход регистра сдвига объединен с, входом делителя част<.ты на два, введены кольцевой счетчик на. три, первый, второй, третий и четвертый синхронизируемые кольцевые счетчики на четыре, блок задержки импульсов и блок детектирующей логики, содержа. щий первый, второй и третий двухвхадовые элементы И, и трехвходовой элемент ИЛИ, выход которого через блок задержки импульсов подключен к первому входу четвертого синхронизируемого кольцевого счетчика на четыре, второй вход которого объединен с третьим входом регистра сдвига и,первыми входами первого, второго и третьего синхронизируемых кольцевых счетчиков на четыре, к вторым входам которых подключены выходы кольцевого счетчика на три, к входу которого подключен выход детектора запрещенных слов, при этом выход первого синхронизируемого кольцевого счетчика на четырех подключен к первым входам первого и третьего .двухвхадовых элементов И, выход второго синхронизируемого кольцевого счетчика на четыре подключен к второму входу первого двухвходового элемента И и первому входу второго двухвходового элемента

И, а выход третьего синхронизируемаго кольцевого счетчика на четыре подключен к вторым входам второго и третьего двухвходовых элементов И, выходы которых, а также выход первого двухвходового элемента И подключены к входам трехвходового элемента ИЛИ.

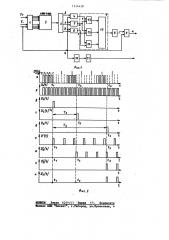

На фиг. 1 представлена структур- ная электрическая схема устройства для блочной синхронизации цифровой системы передачи," на фиг. 2 — временные диаграммы, поясняющие его работу.

Устройство для блочной синхронизации цифровой системы передачи (ЦСП) содержит регистр 1 сдвига, детектор 2 запрещенных слов, кольцевой счетчик 3 на три, первый, — третий синхронизируемые кольцевые счетчики 4-6 на четыре, блок 7 детектирующей логики, блок 8 задержки импуль. сов, четвертый 9 синхронизируемый кольцевой счетчик на четыре, делитель 9 частоты на два, умножитель 11 частоты на три, блок 7 детектирующей логики, содержащий первый — третий двухвхадовые элементы И 12 — 14, трехвходовь -,1 элемент ИЛИ 15.

1124438

Устройство для блочной синхронизации ЦСЛ, использующей многоуровневые коды с избыточностью, работает следующим образом.

Принятые сигналы троичного линей- 5 ного кода (фиг. 2а) через регистр 1 сдвига поступают к соответствующим входам детектора 2 запрещенных слов. ! Принцип работы этих блоков состоит в непрерывном преобразовании последо-10 вательных сигналов положительной и отрицательной полярности, составляющих вместе троичный линейный код, в ь. параллельные блоки этих сигналов и в выделении из последних комбинаций 15 типа "++++" и " ††". Результат обнаружения любой из указанных комбинаций проявляется в подаче импульса с выхода детектора 2 запрещенных слов на вход кольцевого счетчика 3 на три 20 в момент времени, соответствующий приему последнего элемента выделяемой комбинации типа "++++" или

Этот импульс изменяет состояние кольцевого счетчика 3 на три, вызывая 25 появление в этот же момент времени импульса на одном из трех (в зависимости от предшествующего состояния счетчика 3) выходов кольцевого счетчика 3 на три (фиг. 2d-д) и син- 30 хронизацию по этому импульсу соответствующего синхронизируемого кольцевого счетчика на четыре, например, счетчика 4, (фиг. 2е). Результат выделения следующей во времени комбинации отражается на фазе работы синхронизруемого кольцевого счетчика на четыре, в данном случае втброго 5. (фиг. 2ж), третьей комбинации — на фазе работы третьего синхронизируемо-40

ro кольцевого счетчика 6 на четыре (фиг. 2з), а импульс, соответствующий результату выделения четвертой по счету комбинации, вновь синхронизирует первый синхронизируемый кольце вой счетчик 4 на четыре.

Блок 7 детектирующей логики слецит за работой синхронизируемых кольцевых счетчиков 4-Ь на четыре, и,если обнаруживает синфазность работы любых из указанных счетчиков, то коммутирует выходные импульсы синфазных счетчиков на вход блока

8 задержки импульсов, производящего временной сдвиг этих импульсов на два тактовых интервала, т.е. к моментам стыка соседних блоков линейного троичного кода.

Выходные импульсы блока 8 задержки импульсов, появляющиеся случайным

1 образом, но через интервалы времени кратные длительности одного блока линейного троичного кода, и в моменты времени, соответствующие стыку соседних блоков линейного троичного кода, синхронизируют четвертый синхронизиуемый кольцевой счетчик 9 на четыре, на выходе которого получается периодическая последовательностЬ блочных синхроимпульсов (фиг. 2и).

Делитель 10 частоты на два и последовательно соединенный с ним умножитель 11 частоты на три служат для получения колебания тактовой частоты двоичного кода из колебания тактовой частоты троичного кода, также необходимого для работы декодера.

Таким образом, для вхождения устройства в синхронизм достаточно прихода двух комбинаций типа "++++" или " ††", принимаемых в разрешенной фазе. При этом между этими ,комбинациями допустимо присутствие не более одной комбинации типа

11++++11 или 11 — —" у приходящей в фазе, отличной от разрешенной. Появление такой комбинации возможно в результате ошибок в канале передачи.

Предлагаемое устрочство позволяет осуществить блочную синхронизацию декоцеров ЦСП, использующей много- уровневые коды с избыточностью и с низкой величиной текущей цифровой суммы, что приводит к повышению по- мехоустойчивости передачи инАопмации.

1124438

ЗЙИИПИ Ззж 8299 45 аа 634 Ыддисн е

4млыал ПИП Патеит, г.Уагород, ул.Проектиа», 4