Устройство для тактовой синхронизации

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ТАКТОВОЙ СИНХРОНИЗАЦИИ , содержащее последовательно соединенные задакяцнй генератор и управляемый делитель частоты, а также триггер, выход которого подключен к первым входам первого и второго элементов И, О тличающееся тем, что, с целью уменьшения времени вхождения в синхронизм, введены последовательно соединенные блок выделения переходов, счетчик периодов и первый дешифратор и последователь-но соединенные первьй счетчик, блок вычитания, второй счетчик и второй дешифратор, а также блок определения знака сигнала, выходы которого подключены к вторым входам первого и второго элементов И, выходы которых подключены к второму и третьему входам управляемого делителя частоты, выходы которого подключены к входам первого счетчика, выход которого подключен к первому входу блока определения знака сигнала, при этом выход задающего генератора подключен к второму входу второго счетчика , тактовому входу блока вьщеления переходов, информационный вход которого является входом устройства, и второму входу счетчика периодов, вы (Л С ход которого подключен к вторым входам блока вычитания и блока определения знака сигнала, к третьим входам которых и первому входу триггера подключен выход первого дешифратора, а выход второго дешифратора подключен к второму входу триггера. 01 41ь со со L

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН

3 Н 04 1. 7/02

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

flO ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3623134/24-09

tt (22) 14.07.83 (46) 15.11.84. Бюл. N - 42 (72) С.Л. Медведев и А.П. Голенцов (53) 621.394.662(088.8) (56) 1. Авторское свидетельство СССР

У 649148, кл. Н 04 Ь 7/02, 1977.

2. Авторское свидетельство СССР

Ф 681570, кл. Н 04 L 7/02, 1978 (прототип). (54) (57) УСТРОЙСТВО ТАКТОВОЙ СИНХРОНИЗАЦИИ, содержащее последовательно соединенные задающий генератор и управляемый делитель частоты, а также триггер, выход которого подключен к первым входам первого и второго элементов И, о т л и ч а ю щ е е с я тем, что, с целью уменьшения времени вхождения в синхронизм, введены последовательно соединенные блок выделения переходов, счетчик периодов и первый дешифратор и последовательно соединенные первый счетчик, блок

„„SU„„31244 9 А вычитания, второй счетчик и второй дешифратор, а также блок определения знака сигнала, выходы которого ч. подключены к вторым входам первого и второго элементов И, выходы которых подключены к второму и третьему входам управляемого делителя частоты, выходы которого подключены к входам первого счетчика, выход которого подключен к первому входу блока определения знака сигнала, при этом выход задающего генератора подключен к второму входу второго счетчика, тактовому входу блока выделения переходов, информационный вход которого является входом устройства, и второму входу счетчика периодов, выход которого подключен к вторым входам блока вычитания и блока определения знака сигнала, к третьим входам которых и первому входу триггера подключен выход первого дешифратора, а выход второго дешифратора подключен к второму входу триггера.

1124439

Изобретение относится к технике связи и может быть использовано в системах передачи дискретной информации с частотной манипуляцией, Известно устройство синхрониза- 5 ции, содержащее последовательно соединенные генератор импульсов, делитель частоты и блок предварительного вьщеления информации, выходы которого подключены к входам элемента ИЛИ и к входу первого и второго блоков вентилей, а также последовательно соединенные вьщелитель тактовых импульсов и блок управления делителем частоты, выходы которого подключены к другим входам делителя частоты, другой выход которого подключен к первому входу вьщелителя тактовых импульсов, при этом выход элемента ИЛИ через реверсивный распределитель подключен 20 к другим входам первого и второго блоков вентилей и блока управления делителем частоты, а выходы первого и второго блоков вентилей через буферный регистр сдвига подклю-25 чены к второму входу вьщелителя такТОВых импульсОВ, pp ÃОи Выход кОтОро го подключен к другому Входу реверсивного распределителя, а другой вьгход делителя частоты подключен к друго- Зц му входу буферного регистра сдвига f1) .

Однако это устройство обладает большим временем вхождения в синхронизм.

Наиболее близким к предложенному З5 по техническому решению является устройство тактовой синхронизации, содержащее последовательно соединенные задающий генератор и управляемый делитель частоты, а также триггер, 40 выход которого подключен к первым входам первого и второго элементов

И, первый и второй элементы ИЛИ, вы- . ходы которых подключены к второму и третьему входам управляемого делите- 45 ля частоты и входам третьего элемента ИЛИ,выход которого подключен к информационному входу регистра сдвига, к тактовому входу которого и первому входу блока управления подключен вы- 50 ход управляемого делителя частоты, при этом выход приемника подключен к второму входу блока управления и входу датчика перерывов, выход которОГо подключен к BtopbM Входам эле- 55 ментов И, к третьим входам которых йодкнючен выход регистра сдвига, при этом первый и второй Выходы блока управления подключены к входам триггера и вторым входам первого и второго элементов ИЛИ {2) .

Однако такое устройство тактовой синхронизации характеризуется большим временем вхождения в синхронизм.

Цель изобретения — уменьшение

Времени вхождения в синхронизм.

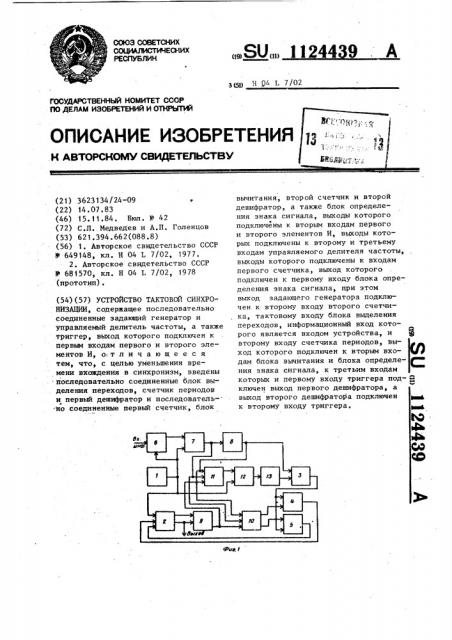

Поставленная цель достигается тем, что в устройство тактовой синхронизации, содержащее послЕдовательно соединенные задающий генератор и управляемый делитель частоты, а также триггер, выход которого подключен к первым входам первого и второ"":о элементов И, введены последовательно соединенные блок выделения переходов, счетчик периодов и первый дешифратор и последовательно соединенные первый счетчик, блок вычитания, второй счетчик и второй дешифратор, а также блок определения знака сигнала, выходы которого подключены к вторым входам первого и второго элементов И, выходы которых подключены к второму и третьему входам управляемого делителя частоты, выходы которого подключены к входам первого счетчика, выход которого подключен к первому входу блока определения знака сигнала, при этом выход задающего генератора подключен к второму входу второго счетчика, тактовому входу блока вьщеления переходов, информационный вход которого является входом устроиства, и второму входу счетчика периодов, выход которого подключен к вторым входам блока вычитания и блока определения знака сигнала, к третьим входам которых и первому входу триггера подкпючен выход первого дешифратора, а выход второго дешифратора подключен к второму входу триггера, На фиг. 1 приведена структурная элен:трическая схема устройства тактовой синхронизации; на фиг. 2 структурная электрическая схема блока выделения переходов. устройство тактовой синхронизации содержит задающий генератор 1, управляемый делитель 2 частоты, триггер

3, элементы И 4 и 5, блок 6 выделения переходов, счетчик 7 периодов, первый дешифратор 8, первый счетчик

9, блок 10 определения знака сигнала, блок 11 вычитания, второй счетчик

1124439

Фс/Г. 2

Составитель Г. Лерантович

Редактор Л.Веселовская Техред Т.Маточка Корректор Е. Сирохман

Заказ 8299/45 Тираж 634 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, И-35, Раушская наб., д. 4/5 филиал ППП "Патент", г. Ужгород, ул. Проектная, 4. 12, второй дешифратор 13, блок 6 выделения переходов, содержащий фильтр

14, ограничитель 15, регистр 16 и элемент совпадения 17.

Устройство тактовой синхронизации работает следующим образом.

Путем деления частоты следования импульсов от задающего генератора 1 на выходы управляемого делителя 2 частоты формируется опорный сигнал, 10 период следования которого соответст. вует скорости передачи информации, т.е. равен длительности одного бита информации.

Первый счетчик 9 подсчитывает 15 количество импульсов за период синхро с иг нала .

Частотно-манипулированный сигнал поступает на информационный вход блока 6 выделения переходов, который 20 в каждый момент перехода сигнала через нуль формирует импульс перехода. Так как входной сигнал представляет собой частотно-манипулированный сигнал, т.е. имеется две частоты f< и f, 25 где f< (f,, то одному биту информации соответствует П периодов частоты f и П, периодов частоты f где П1 с П, Счетчик 7 периодов подсчитывает gp количество импульсов за П., период.

Первый дешифратор 8 определяет моменты сравнения. Он настроен на максимальное число импульсов счетчика 7 периодов, которое будет при частоте f<, В момент сравнения триггер 3 переходит в единичное состояние, показания счетчика 7 периодов и пер.— вого счетчика 9 поступают на первый и второй входы блока 11 вычитания и блок 10 определения знака сигнала, где определяется величина и знак рассинхронизации. Показания блока 11 вычитания переписываются во второй счетчик 12, который считывает это численное значение до нуля.

В момент появления на выходе второго счетчика 12 нулевого значения; на выходе второго дешифратора 13 появляется импульс, который переводит триггер 3 в нулевое состояние.

Таким образом, длительность импульса на выходе триггера 3 пропорциональна величине $ рассинхронизации. В зависимости от знака рассинхронизации корректирующий сигнал через элемент И 4 или элемент H 55 поступает на управляемый делитель

2 частоты, где производится либо добавление, либо .вычитание определенного числа импульсов, пропорциональное величине Й рассинхронизации, из последовательности, поступившей от задающего генератора

Таким образом, предложенное устройство тактовой синхронизации обеспечивает значительное сокращение времени вхождения в синхронизм.