Устройство для приближенного вычисления обратной величины нормализованной двоичной дроби

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ ПРИБЛИЖЕННОГО ВЫЧИСЛЕНИЯ ОБРАТНОЙ ВЕЛИЧИНЫ НОРМАЛИЗОВАННОЙ ДВОИЧНОЙ ДРОБИ, содержащее регистр Аргумента и узел вычитания , о т л и ч а ю щ е е с я тем, что, с целью повьшения быстродействия устройства в него введен блок коррекции, содержащий сумматор-вычи- : татель и группу из (И-2) элементов ИСКЛЮЧАЮЩЕЕ ИЛИ (где п - разрядность аргумента), выходы которых соединены соответственно с пятого по (п+2)-й разрядами первой группы входов сумматора-вычйтателя ,; разряды с первого по четвертый которой соединены с щиной логического нуля устройства. Причем первые входы элементов ИСКЛЮЧАЩЕЕ НИИ группы, объединены и соединены с выходом второго разряда регистра аргумента, вькоды с третьего по tl-й разрядов которого соединены соответственно с вторыми входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ группы, узел вычитания устройства выполнен в виде сумматора-вычитателя, первый, второй и седьмой разряды первой группы входов и второй разряд второй группы входов которого соединены с шиной логической единицы устройства, а остальные разряды первой группы входов и первый разряд второй группы входов узла вьгчитания соединены с шинбй логического нуля устройства, выходы с второго поп -и регистры аргумента соединены соответственно с третьего по (П+2)-й разрядами второй группы входов узла вычитания, выходы разрядов которого соединены соответственно с разрядами второй группы N9 СЛ входов сумматора-вычитателя блока коррекции устройства. О) N9 СО

СОЮЗ СОВЕТСКИХ

И

РЕСПУБЛИК аю 01) arse G 06 F 7 38

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCHOIVIY СВИДЕТЕЛЬСТВУ,V

ГОСУДАРСТВЕННЫЙ НОМИТЕТ CCCP

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3570781/24-24 (22) 01. 04. 83 (46) 23.11.84. Бюп. № 43 (72) И.Ф.Иуравинец, Е.Л.Николаева, А.Н.Романов и А.В.Дрозд (53) 681.325(088.8) (56) 1;. Авторское свидетельство СССР № 732861, кл. Я 06 F 7/38, 1976.

2. Авторское свидетельство СССР № 318940, кл. С 06 F,7/38, 1965 (прототип) . (54) (57) УСТРОЙСТВО ДЛЯ ПРИБЛИЖЕННО-.

ГО ВЫЧИСЛЕНИЯ ОБРАТНОЙ ВЕЛИЧИНЫ НОР- . ИАЛИЗОВАННОЙ ДВОИЧНОЙ ДРОБИ, содержащее регистр аргумента и узел вычитания, о т л и ч.а ю щ е е с я тем, что, с целью повьыения быстродействия устройства, в него введен блок коррекции, содержащий сумматор-вычитатель и,группу из (н-2) элементов

ИСКЛЮЧАЮЩЕЕ ИЛИ (где п - разрядность аргумента), выходы которых соединены соответственно с пятого по (t}+2)-й разрядами первой группы входов сум матора-вычитателя, разряды с первого по четвертый которой соединены с шиной логического нуля устройства, причем первые входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ группы. объединены и соединены с выходом второго разряда регист — ра аргумента, выходы с третьего по

11-й разрядов которого соединены соответственно с вторыми входами элементов ИСКЛЮЧАКЗЦЕЕ ИЛИ группы, узел вычитания устройства выполнен в виде сумматора-вычитателя, первый, второй и седьмой разряды первой группы входов и второй разряд второй группы входов которого соединены с шиной логической единицы устройства, а остальные разряды первой группы вхоO дов и первый разряд второй группы входов узла вычитания соединены с шиной логического нуля устройства, выходы с второго по Н -й регистры аргумента соединены соответственно с третьего по (й+2)-й разрядами второй . Ф группы входов узла вычитания, выходы разрядов которого соединены соответственно с разрядами второй группы входов сумматора-вычитателя блока коррекции устройства. 1125623

Изобретение относится к вычислительной технике и может быть использовано при создании арифметических устройств вычислительных комплексов.

Известно устройство для вычисления обратной величины, содержащее регистр аргумента, сумматоры, элементы ИЛИ и блок анализа разрядов (1) .

Недостатком устройства является

его низкое быстродействие.

Наиболее близким по технической сущности к изобретению является цифровое устройство для. получения начального приближения к обратной вели- 15 чине, содержащее регистр аргумента, выходы которого соединены с входами узла постоянной памяти для хранения .опорных значений обратной величины аргумента и входом узла умножения, узел вычитания, один вход которого соединен с выходом узла постоянной памяти для хранения опорных значе.ний обратной величины аргумента, а другои — с выходом узла умножения, 25 и узел постоянной памяти для хранения значений разрядов приближенных разностей соседних опорных значений обратной величины, входы которого соединены с выходами старших разря30 дов регистра аргумента, а выходы — с входами узла умножения (2) .

Однако известное устройство обладает недостаточным быстродействием.

Целью изобретения является повы.шение быстродействия устройства.

Цель достигается тем, что в устройство для приближенного вычисления обратной величины нормализованной двоичной дроби, содержащее регистр аргумента и узел вычитания, введен блок коррекции, содержащий сумматорвычитатель и группу из (n-2) элементов ИСКЛЮЧАКЩЕЕ ИЛИ (где и — разрядность аргумента), выходы которых соединены соответственно с пятого по (n+2) é разрядами первой группы входов сумматора-вычитателя, разряды с первого по четвертый которой соединены с шиной логического нуля устройства, причем первые входы элементов

ИСКЛЮЧАЮЩЕЕ ИЛИ группы объединены и соединены с выходом второго разряда регистра аргумента, выходы с третьего по 11 -й разрядов Которого соединены соответственно с вторыми входами 55 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ группы, узел вычитания устройства выполнен в виде сумматора-.вычитателя, первый, второй и седьмой разряды первой группы входов и второй разряд второй группы входов которого соединены с шиной логической единицы устройства, а остальные разряды первой группы входов и первый разряд второй группы входов узла вычитания соединены с шиной логического нуля устройства, выходы с второго по n - и регистра аргумента соединены соответственно с третьего по (tl+2) и разрядами второй группы входов узла вычитания, выходы разрядов которого соединены соответственно с разрядами второй группы входов сумматора-вычитателя блока коррекции устройства.

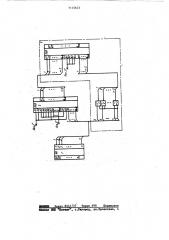

На чертеже представлена функциональная схема устройства для приближенного вычисления обратной величины нормализованной двоичной дроби.

Устройство содержит регистр 1 аргумента, узел 2 вычитания и блок 3 коррекции, причем выход второго разряда регистра 1 аргумента соединен с первыми входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ блока 3 коррекции, вторые входы которых соединены соответственно с выходами-с третьего по 11 -й разрядов регистра 1 аргумента, а выходы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с пятого по (h+2)-й разрядами первой rpуппы входов сумматора-вычитателя блока 3 коррекции, разряды с первого по четвертый которой соединены с шиной логического нуля устройства, первый, второй и седьмой разряды первой группы входов и второй разряд второй группы входов узла 2 вычитания соединены с шиной логической единицы устройства, а остальные разряды первой группы входов и первый разряд второй группы входов узла 2 вычитания соединены с шиной логического нуля устройства, выходы с второго по и-й регистра 1 аргумента соединены соответственно с третьего по (n+2)-й разрядами второй группы входов узла 2 вычитания, выходы разрядов которого соединены соответственно с разрядами второй группы . входов -сумматора-вычитателя блока 3 коррекции устройства.

Устройство работает следующим образом.

В начальный момент в регистр 1 аргумента заносится прямой ход нормализованной двоичной дроби. С выхода регистра 1 аргумента прямой код норма11256 ци

2 (3+2; -2х) -, х-2, если 0,5 х<0,75 где о = 1-(х+2 ), если 0,756ха1.

Величина равна числу в (n-2) младших разрядах прямого кода норма, лизованной двоичной дроби, сдвинутый на один разряд в сторону старших разрядов, поступает на узел 2 вычитания, t где вычитается из постоянной величи-1-5 ны 3+, а разряды с третьего по и-й этого, кода поступают на вторые входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ блока 3 коррекции, на первые входы которых поступает разряд кода с весом 2 2.

С выходов элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 10 код коррекции поступает на вторую группу входов сумматора-вычитателя блока 3 коррекции, на первую группу входов которого поступает код разности с выходов узла 2 вычитания. На 15 выходе блока 3 коррекции формируется прямой код приближенного значения обратной величины нормализованной двоичной дроби.

Узел 2 вычитания осуществляет линейную аппроксимацию функции у=1/х функцией у=3+2 -2х в интервале

О,Ях41.

Блок 3 коррекции производит операю 5

23 4 лиэованной двоичной дроби, если разряд кода с весом 2 2 равен нулю, и инверсии этого числа, если разряд, с весом 2 равен единице.

Время, необходимое для вычисления обратной величины нормализованной двоичной дроби в известном устройстве, составляет ощ Pf "Ag) "ЦМН ВЬЮ где Π— время задержки. переключения регистра аргумента; л nq — время, необходимое для считывания информации из

ПЗУ; л а„- время, необходимое для вычисления произведения двух чисел; л ш- время, необходимое для вычисления разности двух чисел.

- .Время, необходимое для вычисления обратной величины нормализованной двоичной дроби в предлагаемом устройстве, составляет ,Поскольку ь „ заведомо больше

rsbluj быстродействие предлагаемого устройства выше быстродействия известного.

1125623

Я И Закаэ 8541/37 . Ти аж 698 По писиое и Й

4 93вал ППП атамт, t Óàãîðîä, ул. Проектная, 4