Двухканальный формирователь однополосного сигнала

Иллюстрации

Показать всеРеферат

ДВУХКАНАЛЬНЫЙ ФОРМИРОВАТЕЛЬ ОДНОПОЛОСНОГО СИГНАЛА, содержащий в каждом канале первый элемент И, последовательно соединенные формирователь импульсов и инвертор, последовательно соединенные второй элемент И и первый триггер,второй вход которого соединен с первым входом второго элемента И, при этом выход формирователя импульсов первого канала подключен к первым входам второго элемента И первого канала и первого элемене . та И второго канала, выход инвертора первого канала подключен к первым входам первого элемента И первого канала и второго элемента И второго канала, а выходы первых элементов И каждого канала подключены к выходам общего элемента ИЛИ, отличающийся тем, что, с целью его упрощения путем включения блоков формирующих квадратурные сигналы, в него введен в каждом канале второй триггер, причем вход и выход инвертора второго канала соединены с вторыми входами второго элемента И соответственно второго и первого каналов, а в каждом канале первый, второй входы и выходы второго тригге (О ра соединены соответственно с выхода-, ми первого триггера, формирователя импульсов и с вторым входом первого элемента И, третий вход второго триггера одного канала соединен с выходом первого элемента И другого канала.

„.SU„„1125737

СОЮЗ СО8ЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

1 60

OllHCAHNE ИЗОБРКтКНиЯ /, Н АВТОРСНОМУ СВИДЕТЕЛЬСТВУ

C r

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

flO ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3499236/18-09 (22) 06.10.82 (46) 23.11.84. Бюл. Ф 43

"(72) В.С.Островский, В.M.Âàñèëüåâ и В.Д.Козловская (53) 621.376.24(088.8) (56). 1. Авторское свидетельство СССР

Ф 746861, кл. Н 03 С 1/60, 1978.

2. Авторское свидетельство СССР

Ф 879735, кл. Н 03 С 1/60, 1979. (прототип). (54)(57) ДВУХКАНАЛЬНЫЙ ФОРМИРОВАТЕЛЬ

ОДНОПОЛОСНОГО СИГНАЛА, содержащий в каждом канале первый элемент И, последовательно соединенные формирователь импульсов и инвертор, последовательно соединенные второй элемент И и первый триггер, второй вход которого соединен с первым входом второго элемента И, при этом выход формирователя импульсов первого канала подключен к первым входам второго элемента И первого канала и первого элеменР та И второго канала, выход инвертора первого канала подключен к первым входам первого элемента И первого канала и второго элемента И второго канала, а выходы первых элементов И каждого канала подключены к выходам общего элемента ИЛИ, о т л и ч а юшийся тем, что, с целью его упрощения путем включения блоков формирующих квадратурные сигналы, в него введен в каждом канале второй триггер, причем вход и выход инвертора второго канала соединены с вторыми входами второго элемента И соответственно второго и первого каналов, а в каждом канале первый, Я второй входы и выходы второго триггера соединены соответственно с выхода-, Ц 1 ми первого триггера, формирователя С импульсов и с вторым входом первого элемента И, третий вход второго триг- Я гера одного канала соединен с выходом первого элемента И другого канала.

1125737

И зобретение относится к радиотехнике и может найти применение в устройствах цифровой обработки сигналов, Известен формирователь однополосйого сигнала, содержащий первый формирователь импульсов, выходы которого непосредственно и через первый и второй инверторы подключены к входам дополнительного формирователя импульсов, выходы которого, а также выходы вто 1О рого формирователя импульсов непосредст венно через третий и четвертый инверторы подключены к входам четырех элементов И, выходы которых подключены к входу элемента ИЛИ (1 3.

Недостатком данного формирователя однополосного сигнала является низкая точность формирования разностной частоты.

Наиболее близким к изобретению является двухканальный формирователь однополосного сигнала, содержащий в каждом канале первый элемент И, последовательно соединенные формирователь импульсов и инвертор, пос25 ледовательно соединенные второй элемент И и первый триггер, второй вход которого соединен с первым входом второго элемента И, при этом выход формирователя импульсов первого канала подключен к первым входам второго элемента И первого канала и первого элемента И второго канала, выход инвертора первого канала подключен к первым входам первого 35 элемента И первого канала и второго элемента И второго канала, а выходы первых элементов И каждого канала подключены к входам общего элемента

ИЛИ (2 j. 40

Недостатком известного двухканального формирователя однополосного сигнала является необходимость формирования квадратурных симметричных импульсных последовательностей умень-45 шаемой и вычитаемой частоты.

Цель изобретения — упрощение двухканального формирователя однополосного сигнала путем исключения блоков, формирующих квадратурные сигналы. 50

Поставленная цель достигается тем, что в двухканальный формирователь однополосного сигнала, срдержащий в каждом канале первый элемент И, последовательно соединенные формирова- 55 тель импульсов и инвертор, последовательно соединенные второй элемент И и первый триггер, второй вход которого соединен с первым входом второго элемента И, при этом выход формирователя импульсов первого канала о подключен к первым входам второго элемента И первого канала и первого элемента И второго канала, выход инвертора первого канала подключен к первым входам первого элемента И первого канала и второго элемента И второго канала, а выходы первых элементов И каждого канала подключены к входам общего элемента ИЛИ, введен в каждом канале второй триггер, причем вход и выход инвертора второго канала соединены с вторыми входами второго элемента И соответственно, второго и первого каналов, а в каждом канале первый и второй входы и выходы второго триггера соединены соответственно с выходами первого триггера, формирователя импульсов и с вторым входом первого элемента И, третий вход второго триггера одного канала соединен с выходом первого элемента И другого канала.

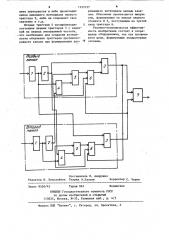

На чертеже изображена функциональная электрическая схема двухканального формирователя однополосного сигнала.

Формирователь содержит первый и второй каналы, каждый из которых

-содержит формирователь 1 импульсов, инвертор 2, первый 3, второй 4 элементы И, первый 5 и второй 6 триггеры, а также общий элемент ИЛИ 7.

Устройство работает следующим образом.

Для формирования разностной часто ты достаточно иметь информацию о

; взаимном временном положении полупериодов сигналов уменьшаемой и вычитаемой частот, Если четверть периода сигнала уменьшаемой частоты целиком попадает внутрь соответствующей четверти периода сигнала вычитаемой частоты, то полупериод, к которому принадлежит данная четверть сигнала уменьшаемой частоты, целиком лежит внутри соответствующего полупериода сигнала вычитаемой частоты.

Таким образом, создается возможность перейти от анализа временного положения соответствующих четвертей периода сигналов уменьшаеыой и вычитаемой частот к анализу временного положения соответствующих полупериодов. Формирователь 1 импульсов и инвертор 2 преобразуют входные сиг ю

11257

3 налы в симметричные импульсные последовательности, сдвинутые одна относительно другой на полупериод, которые поступают на входы элементов

И 3 и 4. Триггеры 5 и 6 фиксируют в виде потенциала моменты совпадения по времени полупериодов сигнала уменьшаемой частоты с соответствующими нолупериодами сигнала вычитаемой частоты. В зависимости от несов- 10 падения на выходе второго триггера 6 появляется либо разрешающий, либо запрещающий потенциал, который управляет прохождением одной из симметричных импульсных последовательностей уменьшаемой частоты на выход устройства. Так как информацию о совпадении соответствующих полупериодов сигналов уменьшаемой и вычитаемой частот можно получить лишь в конце интер- 20 вала времени, занимаемого соответствующим полупериодом сигнала уменьшаемой частоты, то информация о моменте совпадения используется для управления прохождением на выход устройства симметричной импульсной последовательности, задержанной по отношению к участвующей в сравнении. Это может быть импульсная последовательность, задержанная на полупериод и .30 формируемая в семействе симметричных импульсных последовательностей первого канала.

Таким образом, симметричные импульсные последовательности, формируемые формирователем 1 импульсов и инвертором 2 первого канала, поступают на первые входы первых элементов

И 3, на вторые входы которых поступают сигналы с выходов вторых триг- 40 геров 6. Выходной сигнал устройства формируется в результате логического сложения в общем элементе ИЛИ 7 напряжений, действующих на выходах первых элементов .И 3. Каждому моменту45 совпадения полупериодов входных сигналов соответсвует прохождение на выход одного из первых элементов И 3 одного импульса соответствующей симметричной импульсной последователь- 50 ности уменьшаемой частоты. Исключение

„составляет лишь случай совпадения ближайших полупериодов сигнала уменьшаемой частоты с соответствующими сигналами вычитаемой частоты. Такая 55 ситуация должна привести к появлению на выходе устройства одного импульса сигнала разностной частоты. Поскольку

37 4 совпадают ближайшие полулериоды, то на выходе элементов И 3 должны появиться следующие один за другим импульсы соответствующих симметричных импульсных последовательностей уменьшаемой частоты, формируемые на выходах формирователя 1 импульсов н инвертора 2 первого канала, которые при сложении в общем элементе ИЛИ 7 должны бы образовать один импульс длительностью, равной периоду уменьшаемой частоты. Однако ввиду наличия задержки при формировании инвертированного симметричного сигнала в инверторе 2 первого канала полного слияния импульсов на выходе общего элемента ИЛИ 7 в данном случае не произойдет. Наличие "врезки" между импульсами приводит к сбою цифровых устройств, обеспечивающих последующую обработку выходного сигнала.

Для исключения возникновения ложных импульсов на выходе предлагаемого устройства сигналы с выходов первых элементов И 3 поступают на третьи входы вторых триггеров 6, устраняя формирование разрешающего потенциала на их выходах при совпадении ближайшего последующего полупериода сигнала уменьшаемой частоты с соответствующим полупериодом сигнала вычитаемой частоты. Передний фронт симметричной импульсной последовательности, поступающей на второй вход первого триггера 5, вызывает сраба- . тывание и установку его в. "1" лишь в том случае, если этот фронт по времени лежит внутри полупериода сигнала вычитаемой частоты. В противном случае второй элемент И 4 формирует сигнал установки первого триггера 5 в нулевое состояние. Если задний фронт соответствующего полупериода сигнала уменьшаемой частоты выходит за пределы соответствующего полупериода сигнала вычитаемой частоты, то второй элемент И 4 также формирует сигнал установки первого триггера .5 в нулевое состояние. Если полупериод сигнала уменьшаемой частоты полностью лежит внутри интервала времени, занимаемого соответствующим полупериодом сигнала вычитаемой частоты, то первый триггер 5 устанавливается в "1" и удерживает это состояние до прихода следующего однотипного полупериода сигнала уменьшаемой частоты. С приходом нового полупериода процесс ана1125737

Составитель О. Андрушко

Редактор И. Николайчук Техред И.Кузьма Корректор С. Черни

Заказ 8556/43 Тираж 861 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4 лиза повторяется и либо происходит смена выходного потенциала первого триггера 5, либо он сохраняет свое значение и т.д.

Вторые триггеры 6 воспроизводят 5 состояния первых триггеров 5 с эадеркой на период уменьшаемой частоты, что необходимо для создания возможности обнуления триггеров противоположного канала при формировании разрешающего потенциала данным кана" лом. Обнуление производится импуль сом, формируемым на выходе первого элемента И 3, поступающим на третий вход триггера 6.

Технико-экономическая эффективность изобретения состоит в сокращении оборудования, так как исключаются цепи, формирующие квадратурные сигналы.