Цифровой фильтр

Иллюстрации

Показать всеРеферат

ЦИФРОВОЙ ФИЛЬТР, содержащий регистр сдвига, выходы разрядов которого подключены к входам многовходового сумматора, а также первый двухвходовой сумматор, выход которого подключен, к входу р егистра задержки, выход которого соединен с первым входом первого двухвходового сумматора , отличающийся тем, что, с целью расширения функциональньк возможностей путем обеспечения согласованной фильтрации псевдослучайных последовательностей, в него введены второй и третий двухвходовые сумматоры и умножитель на два, при этом первый вход второго двухвходового сумматора подключен к вькоду первого разряда регистра сдвига, второй вход - к выходу последнего разряда регистра сдвига, а выход к первому входу третьего двухвходового сумматора, второй вход которого соединен через умножитель на два с выходом многовходового сумматора, а выход - с вторым входом первого двухвходового сумматора, третий вход которого является входом сигна§ ла логической единицы, при этом входы многовходового сумматора подключены к выходам разрядов регистра с сдвига в соответствиис К + Ц - , где К - весовой коэффициент. iNd СЛ а

союз советских

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК.Я0„3 325

3(59 Н 03 Н 17/00 госудм ствеккый комитет ссср по делАм иэОБРетекий и ОткРытий

ОЛИСАНИЕ ИЗОБРЕ

К ABTOPCHOMV СВИДЕТЕЛЬСТВУ (21) 3513313/24-09 (22) 19. 11. 82 (46) 23.11.84. Бюп.143 (72) А.Н.И1полянский (53) 621.396 ° 6(088.8) (56) 1. Слока В.К. Вопросы обработки радиолокационных сигналов. М., "Советское радио", 1970, с.214-215, рис.8.10.

2. Патент США -4237463, кл.-.Н 04 В 1/12, опублик. 1980. (54)(57) ЦИФРОВОЙ ФИЛЬТР, содержащий

° регистр сдвига, выходы разрядов которого подключены к входам многовходового сумматора, а также первый двухвходовой сумматор, выход которого ° подключен, к входу регистра задержки, выход которого соединен с первым входом первого двухвходового сумматора, отличающийся тем, что, с целью расширения функциональных возможностей путем обеспечения согласованной фильтрации псевдослучайных последовательностей, в него введены второй и третий двухвходовые сумматоры и умножитель на два, при этом первый вход второго двухвходового сумматора подключен к выходу первого разряда регистра сдвига, второй вход — к выходу последнего разряда регистра сдвига, а выход— к первому входу третьего двухвходового сумматора, второй вход которого соединен через умножитель на два с выходом многовходового сумматора, а выход — с вторым входом первого двухвходового сумматора, третий вход которого является входом сигна ла логической единицы, при этом вхо- Е ды многовходового сумматора подклю- чены к выходам разрядов регистра с сдвига в соответствии с K + К;

+1

1 где К вЂ” весовой коэффициент.

1 11257

Изобретение относится к технике оптимального приема сигналов и может быть использовано в устройствах цифровой обработки сигналов, а также в радиолиниях в качестве согласованного фильтра для выделения кодовьм слов в виде псевдослучайных последовательностей (ПСП).

Известен цифровой фильтр, содержащий регистр сдвига и многовходовой lO сумматор, состоящий из блоков совпадения, подключенных к выходам разрядов регистра сдвига, вторые входы блоков совпадения соединены с выходами элементов хранения кода веса, 15 а выходы — с входами мнрговходового сумматора (1 .

Недостатком данного цифрового фильтра является его низкое быстродействие, что объясняется необходи- 20 мостью выполнения за один такт работы (такт сдвига) суммирования боль— шого числа,(М) кодов, что снижает частотный диапазон обрабатываемых сигналов. Кроме того, цифровой . 25 фильтр имеет низкую надежность из-за большого числа связей, вызванных необходимостью иметь отводы от каждого разряда регистра сдвига. Отмеченные недостатки устройства тем значительнее, чем больше длина обф батываемой ПСП.

Наиболее близким к изобретению по технической сущности является цифРовой фильтР., содержащий последовательно соединенные регистр сдвига и многовходовой сумматор, дополнительный вход которого соединен с выходом первого селектора знака, второй селектор знака, вход которого > подключен к выходам разрядов регистра сдвига, а выход — к первому входу двухвходового сумматора, второй вход которого подключен к выходу регистра задержки, вход которого соединен с выходом двухвходового сумматора (2).

Однако известный цифровой фильтр не может обеспечивать согласованную фильтцию ПСП, что сужает его функциональные возможности. (1) (1) где X — отсчеты входного сигнала, ь принимающие значения +1 и -1;

К. = 4 . — весовые коэффициенты, К-1 i принимающие значения +1 и -1;

+ — значения ожидаемой ПСП.

Выполнение фильтрации непосредственно по выражению (1) при обработке

ПСП требует избыточного количества операций. Для сигнала на выходе цифЦель изобретения — расширение функциональных возможностей устройства путем обеспечения согласованной фильтрации псевдослучайных после-55 довательностей.

Поставленная цель достигается тем, что в цифровой фильтр, содержа.

46 2 щий регистр сдвига, выходы разрядов которого подключены к входам многовходового сумматора, а также первый двухвходовой сумматор, выход которого подключен к входу регистра задержки, выход которого соединен с первым входом первого двухвходового сумматора, введены второй и третий двухвходовые сумматоры и умножитель на два, при этом первый вход второго двухвходового сумматора подключен к выходу первого разряда регистра сдвига, второй вход — к выходу по следнего разряда регистра сдвига, а вьмод — к первому входу третьего двухвходового сумматора, второй вход которого соединен через умножитель на два с выходом многовходового сумматора, а вьмод — с вторым входом первого двухвходового сумматора третий вход которого является входом сигнала логической единицы, при этом входы многовходового сумматора подключены к выходам разрядов регистра сдвига в соответствии с К;+K 1

+1 где К вЂ” весо2 вой коэффициент.

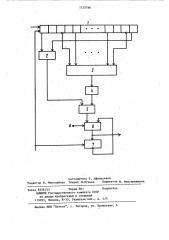

На чертеже представлена структурная электрическая схема цифрового фильтра.

Цифровбй фильтр содержит регистр

1,сдвига, второй двухвходовой сумматор 2, многовходовой сумматор 3, умножитель 4 на два, третий 5 и первый 6 двухвходовые сумматоры, регист

7 задержки и вход 8 сигнала логической единицы, . Устройство работает следующим образом.

При согласовании фильтрации бинарных сигналов вычисляется взвешенная сумма

1125746

И-1

К K -1

1=1

-у„„, (4} могут принимать одно из трех значений +1, -1,0. Известное свойство

ПСП состоит в том, что в них общее

40 число пар соседних позиций (К; 1,К;} принимающих значения (+1,-1), (-1, +1), (+1, +1), (-1, - 1), практически одинаково, Поэтому в выражении (4) примерно половина коэффициентов

K1+ К1-1 равна нулю, что существенно ,(почти в два раза) сокращает число необхолимых операций при фильтрации, 3 рового согласованного фильтра в и . (n-1) -м тактах:

П-« 1-2 2 " и-(М-2} N-2

11-(N-1} N-1 (2}

=х K +х K+...+x к +, ь-1 n-a î п-2 1 " n (N-2} х (М }КN-2+Х МКм 1 (Я

После суммирования выражений (2) и (3) и приведения подобных членов, получаем

=х К +x {К +к )+ {к к„) --+ .

-(М"1} N-1 К-2 n- N М-1

+Х К К +х

Леренеся „1 в левую часть, используя знак суммирования и вынося коэффициент g из-под знака суммы, получаем разностное уравнение работы согласованного цифрового фильтра: (В выражении (4) в отличие от выражения (1) для получения очередного значения выходного сигнала v используются не только настоящее и предыдущее значения входного сигнала х„ „ но и полученное в предыдущем такте значение выходного сигнала „ 1.Коэф; к.+к

35 фициенты 1 1-1 в выражении (4)

Перед началом работы регистр 1 сдвига и регистр 7 задержки устанав-. ливаются в исходное состояние.

Фильтрующий сигнал х„ поступает на вход регистра 1 сдвига. В каждом такте работы сигналы с выходов первого и последнего (N+1)-го разрядов регистра 1 сдвига суммируются вторым двухвходовым сумматором 2, а сигналы с промежуточных выходов регистра 1 сдвига — многовходовым сумматором 3. Образовавшееся на выходе многовходового сумматора 3 число умножается на два в умножителе 4 и складывается в третьем пвухвхоповом сумматоре 5 с результатом, полученным на втором двухвходовом сумматоре 2. Сигнал в виде прямого параллельного кода с выхода третьего двухвходового сумматора

5 поступает на второй вход первого двухвходового сумматора 6, на первый вход которого поступает задержанный на один такт выходной сигнал, сформированный в предыдущем такте работы фильтра (Ч„, „j. .Задержанный на такт выходной сигнал поступает с инверсных выходов регистра 7 задержки и потому представлен в обратном коде. На входе переноса младшего разряда двухвходового сумматора

6 постоянно действует единичный потенциал, поданный с входа 8 сигнала логической единицы, образующий вместе с поступающим обратным кодом дбполнительный код числа „ „.,В результате на первом двухвходовом сумматоре 6 выполняется операция ,вычитания числа „ „, так что на выходе первого двухвходового сумматора

6 оказывается сформированным выходной отфильтрованный сигнал чп, который записывается в регистр 7 задержки для использования в следующем такте работы.

Таким образом, предлагаемый цифровой фильтр обеспечивает согласованную фильтрацию псевдослучайных после-. довательностей.

1125746

Подписное

Заказ 8556/43 Тираж 861

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35. Раушская наб., д. 4/5

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4

Составитель Т. Афанасьева

Редактор И. Николайчук Техред b1,Кузьма Корректор м. максимищинец