Многоканальная система связи

Иллюстрации

Показать всеРеферат

СОЮЗ СО8ЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН (1Ю (11) эра Н 04 В 9/00

OllHGAHHE ИЗОБРЕТЕНИЯ

Н ABTOPCHOMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТ8ЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3265462/18-09 (22) 23.07.81. (46) 23.11 ° 84. Бюл. ¹- 43 (72) А.-M.À.М.Абдулаев, В.Ю.Барановский, И.В. Галкин и А.К. Мамедов (71) Азербайджанский политехнический институт им. Чингиза Ильдрыма (53) 621.396.6(088.8) (56) 1. "Электроника"., 1976, № 5, с. 38.

2. Основы многоканальной связи.

Под ред. И.Н. Бобровской, М., "Связь", .1975, с. 26/30, рис. 1.10 (прототип). (54)(57) МНОГОКАНАЛЬНАЯ СИСТЕМА СВЯЗИ, содержащая на передающей стороне генератор тактовых импульсов, соединенный с входом блока выборки и хранения, выходы которого соединены с входами блока ключей, формирователь импульсов и модулятор, а на приемной стороне последовательно соединенные формирователь импульсов, блок задержки, элемент И-НЕ, а также дискриминатор и блок демодуляторов, о т л и— . ч а ю щ а.я .с я тем, что, с целью повышения помехозащищенности путем обеспечения гальванической развязки при одновременном увеличении пропускной способности, на передающей стороне введены счетчик, дешифратор, элемент ИЛИ, триггер и блок развязки, причем выход генератора тактовых импульсов. через последовательно соединенные формирователь импульсов, счетчик, дешифратор, блок ключей, модулятор, триггер и блок развязки соединен с каналом связи, выход модулятора соединен с входом "Сброс" счетчика, выход формирователя импульсов через элемент ИЛИ соединен с входом

"Сброс" триггера, выход дешифратора соединен с вторым входом элемента

ИЛИ, а модулятор выполнен- в виде компаратора, выход которого через интег- I ратор соединен с входом компаратора, вход и выход которого. являются соответственно входом и выходом модуляФ тора, а на приемной стороне введены

Р счетчик и дешифратор, причем выход . Я формирователя импульсов через дискримиыатор соединен с вторым входом элемента И-НЕ и входом счетчика, разрядные выходы которого через дешифратор соединены с входами блока демодуляторов, а дискриминатор выполнен в виде последовательно соединенных интегратора и компаратора.

1125

Изобретение относится к технике электрической связи.и может использоваться в линейных электронных системах, в частности в многоканальных системах сбора и обработки информацИНе

Известно устройство передачи сигналов, содержащее генератор тактовых импульсов, одновибратор логичесянй оптроя, демодулятор (!

Однако такое устройство о ладает низкой помехоустойчивостью.

Наиболее близким техническим решением к предложенному является многоканальная система связи, содержащая на передающей стороне генератор тактовых импульсов, соединенный с входом блока выборки и хранения, выходы которого соединены с входами блока ключей, формирователь импульсов и модулятор, а на приемной стороне последовательно соединенные формирователь импульсов, блок задержки, элемент И-НЕ, а также дискриминатор и блок демодуляторов (2 .

Однако известное устройство имеет низкую помехозащищенностье . Цель изобретения — повышение помехозащищенности путем обеспечения гальванинеской развязки при одновре30 менном увеличении пропускной способности.

Цель достигается тем, что в многоканальной системе связи, содержащей на передающей стороне генератор тактовых импульсов, соединенный с входом бло- З5 ка выборки и хранения, выходы которого соединены с входами блока ключей формирователь импульсов и модулятор, а на приемной стороне последовательно соединенные формирователь импульсов, блок задержки, элемент И-НЕ, а также дискриминатор и. блок демодуляторов, на передающей стороне введены счетчик, дешифратор, элемент ИЛИ, триггер и блок развязки, причем выход генератора тактовых. импульсов через последовательно соединенные формирователь импульсов, счетчик, дешифратор, блок ключей, модулятор, триггер и блок развязки соединен с каналом связи, выход модулятора соединен с входом "Сброс" счетчика, выход формирователя импульсов через элемент ИЛИ . соединен с входом "Сброс" триггера, выход дешифратора соединен с вторым входом элемента ИЛИ, а модулятор выполнен в ниде компаратора, выход которого через интегратор соединен с

754 входом компаратора, вход и выход которого являются соответственно входом и выходом модулятора, а на приемной стороне введены счетчики и дешифратор, причем выход формирователя импульсов через дискриминатор соединен с вторым входом элемента И-НЕ и входом, счетчика, разрядные выходы которого через дешифратор соединены с входами блока демодуляторов, а дискриминатор выполнен в виде. последовательно соединенных интегратора и компаратора.

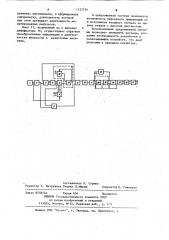

На чертеже изображена структурная электрическая схема предложенной системы;

Многоканальная система связи содержит генератор 1 тактовых импульсов, формирователь 2 импульсов, счетчик 3, дешифратор 4, блок 5 ключей, блок 6 выборки и хранения, модулятор 7, элемент ИЛИ 8,.триггер 9, блок 10 развязки, формирователь 11 импульсов, дискриминатор 12, блок 13 задержки, элемент И-НЕ 14, счетчик

15, дешифратор 16, блок 17 демодуляторов, компаратор 18, интеграторы 19 и 20, компаратор 21.

Система работает следующим образомм.

Импульсом с выхода генератора 1 блок 6 переводится в режим выборки.

Минимальное значение длительности тактовых импульсов определяется временем включения блока 6. С окончанием тактового импульса блок 6 переводят в режим хранения. По заднему фронту тактового импульса формирователь 2 формирует импульс, положительным потенциалом которого счетчик 3 и триггер 9 по прямым входам устанавливают- ся в нулевое состояние, которому соответствует состояние дешифратора 4— единица на первом выходе, вызывающая замыкание одного ключа в блоке 5, через который на выход блока 5 проходит напряжение с выхода блока 6 от первого сигнала. До поступления напряжения с выхода блока 5 на вход компаратора 18, который находится в нулевом состоянии и этим нулем поддерживает интегратор 19 в состоянии

"Сброс". С поступлением напряжения от блока 6 компаратор 18 перебрасывается в единичное состояние, при котором интегратор 19 переводится в режим интегрирования пастояинс.го напряжения, при котором происходит

112575; формирование линейнонарастающего напряжения .на выходе интегратора 19.

Величина напряжения должна быть больше. максимального значения напря- жения входного сигнала. Одновременно перепад импульса с выхода компаратора 18, подаваемый на счетный вход счетчика 3, переключает счетчик 3 в состояние, которому соответствует единица на втором выходе де- 10 шифратора 4. В результате на вход компаратора 18 поступает напряжение с выхода блока 6 от второго сигнала.

Задержки переключения счетчика 3, дешифратора 4, и блока 5 подобраны 15 таким образом, что к моменту окончания сброса в интеграторе 19 на входе компаратора 18 уже появится напряжение с выхода блока 6. Процесс повторяется для и сигналов. После 20 окончания преобразования напряжения от блока 6 компаратор 18 пере- ключается в нулевое состояние, пере- ключается счетчик З.и дешифратор 4 устанавливается в состояние "едини-" 25

tt ца на и+1 выходе. При этом на входе компаратора 18 появится нулевое напряжение, а в интеграторе 19 произойдет сброс. В состоянии синхро-— паузы компаратор 18 будет находиться 30 до поступления следующего импульса от формирователя 2 на счетчик 3.

Число состояний дешифратора 4 равно, коэффициенту пересчета счетчика 3 и равно числу источников входного 35 сигнала плюс единица Выход компаратора,18 соединен со счетным входом триггера 9, который переключается от каждого перепада импул -са. Переключение триггера 9 после преобразования40 п сигналов осуществляется за счет единичного, потенциала с и+1 выхода дешифратора 4. Чтобы состояние синхропаузы на выходе триггера 9 всегда было нулевым, необходимо число источ- 45 ников входного сигнала выбирать нечетным. Таким образом, за один. период квантования; задаваемый генератором 1 на выходе триггера 9, образуется. непрерывная последовательность из и состояний единиц и нулей, длительности которых пропорциональны напряжениям, хранящимся в блоке 6 и состояния синхропаузы. При этом минимальная. длительность синхропаузы задается 55 такой, чтобы она заведомо превышала максимальную длительность модулированных импульсов. После прохождения через блок 10 модулированная последовательность поступает на вход формирователя 11, выход которого соединен с интегратором 20. До поступления модулированной последовательности на выходе формирователя 11 нулевой уровень и на вь ходе интегратора 20 происходит формирование линейно-. нарастающего напряжения. При достижении порогового напряжения на выходе интегратора 20 компаратор 21 переключится в нулевое состояние, запрещая прохождение импульсов на счетчик 15, который устанавливается в нулевое состояние, которому соответствует единица. на и+1 выходе дешифратора 16. Это состояние неинформационное.

Когда с выхода формирователя 11 поступает импульс, в интеграторе

20 осуществляется сброс, компаратор

21 снимает запрет на прохождение импульсов с выхода формирователя 11 на счетчик 15. Задержанный импульс. с выхода формирователя 11 через блок

13 переключит счетчик 15 в состояние, соответствующее единице на первом выходе дешифратора 16, который соответствует первому источнику входного сигнала. Во время паузы между импульсами с формирователя -11.èíòåãðàтор 20 находится.в режиме интегрирования. Однако переключения компаратора

21 не произойдет так-как пороговое напряжение выбрано таким, что выходное напряжение интегратора 20 достигает его только при условии, если длительность паузы превысит минимальную дли- тельность синхропаузы. Таким образом, йа выходах дешифратора 16 выделяются импульсы, длительности которых пропорциональны напряжению блока 6. После выделения на выходе дешифратора 16 импульса, соответствующего и-му ис-. точнику входного сигнала, дешифратор

16 переходит в и+1состояние.Напряже% ние с выхода интегратора 20 через время, превышающее максимальную дли- тельность модулированных импульсов, переключает компаратор 21 в нулевое состояние. В этом состоянии дешифратор 16 удерживается до поступления импульса с формирователя 11.

Период квантования, задаваемый генератором I выбирается таким, чтобы за время одного периода успеть преобразовать напряжения от всех элементов блока 6, когда они все одно1125754

Составитель Е. Сурина

Редактор С. Патрушева Техред Л.Иикеш Корректор В. Синицкая

Заказ 8558/44 Тираж 634 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5 филиал ППЛ "Патент", r. Ужгород, ул. Проектная, 4

Э временно.максимальны, и сформировать синхропаузу, длительность которой при.этом превышает длительность модулированных импульсов.

Блок 17, включенный на п выходах 5 дешнфратора 16, осуществляет обратное преобразование информации в .длительностях импульсов в .аналоговые величины.

В предложенной системе появляется возможность передавать информацию от и источников входного сигнала по одному каналу с высокой плотностью.

Использование предложенной системы позволяет уменьшить расходы, устранив необходимость разработки п развязывающих устройств, что дает экономию в народном хозяйстве.