Компаратор на мдп-транзисторах

Иллюстрации

Показать всеРеферат

КОМПАРАТОР НА МДП-ТРАНЗИСТОРАХ , содержащий дифференциальный .каскад, два конденсатора, два транзистора , каждый из которых подключен соответственно меядцу прямым входом и инверсным выходом и между инверсным входом и прямым выходом дифференциального каскада, прямой и ин .версный входы которого подключены соответственно к первым выводам первого и второго конденсаторов, а затворы транзисторов подключены к шине управляющих сигналов, о т л и ч а ющ и и с я тем, что, с целью повышения точности за счет увеличения коэффициента усиления, в него введены третий, четвертый, пятый, шестой транзисторы и два дополнительных конденсатора, при зтом каждый дополнительный конденсатор подключен соответственно между прямыми входом и. выходом и инверсным входом и выходом дифференциального каскада, -а третий и четвертый, пятый и шестой транзисторы включены последовательно и подключены к шинам входных сигналов , а затворы третьего ишестого, четвертого и пятого транзисторов подключены соответственно к шинам парафазного управляющего сигнала а точки соединения .третьего и четвертого , пятого и шестого транзисторов подключены соответственно к вторым выводам второго и -первого конденсаторов.

СОЮЗ СОВЕТСКИХ

В,ИЦ»

РЕСПУБЛИН

С 05 В 1/01

ОПИСАНИЕ ИЗОБРЕТЕНИЯ /

К ABTOPGHQMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3565236/24-21 (22) 17.03.83 (46) 30.11.84. Бюл.й 44 (72) Е.И.Андреев, А.И.Бухштаб и Э,З.Гинзбург (53) 621.374.34(088,8) (56) 1. Патент США N - 3882326, кл. 307-235, 1975.

2. Патент GHA N - 4264872,кл.230-253, 1981 (йрототип). (54) (57) КОМПАРАТОР НА ИДП-ТРАНЗИСТОРАХ, содержащий дифференциальный каскад, два конденсатора, два транзистора, каждый иэ которых подключен соответственно между прямым входом и инверсным выходом и между инверсным входом и прямым выходом дифференциального каскада, прямой и ин,версный входы которого подключены соответственно к первым выводам первого и второго конденсаторов, а затворы транзисторов подключены к шине

„„SU„„1126943 А управляющих сигналов, о т л и ч а юшийся тем, что, с целью повышения точности эа счет увеличения коэффициента усиления, в него введены третий, четвертый, пятый, шестой транзисторы и два дополнительных конденсатора, при этом каждый дополнительный конденсатор подключен соответственно междупрямыми входом и выходом и инверсным входом и выходом дифференциального каскада, а третий и четвертый, пятый и шестой транзисторы включены последовательно и подключены к шинам входных сигналов, а затворы третьего и шестого четвертого и пятого транзисторов подключены соответственно к шинам парафаэного управляющего сигнала, а точки соединения. третьего и четвертого, пятого и шестого транзисторов подключены соответственно к вторым выводам второго и -первого конденсаторов.

1 )?6943

Изобретение относится к области импульсной техники и может быть использовано в устоойствах пгеобразования информации, а также контрольно-измерительных устройствах.

Известны компараторы, содержащче каскад с прямым и инверсным входом и зыхоцом, два коммутационных транзистора в цепи обратной связи в каждом плече дифференциального каскада > ) j.

Недостатком известных схем является низкая точность ввиду невысокого коэффициента усиления дифференциального каскада, Наиболее близким по технической сущности к данному является компаратор на ИДП"транзисторах, содержащий дифференциальный каскад, два конденсатора, два транзистора, каждый из которых подключен соответстьенно между прямым входом и инверсным вы- . ходом и между инверсным входом и прямым выходом дифференциального каскада, прямой и инверсный выходы которого подключены соответственно к первым выводам первого и второго конденсатора, а затворы транзисторов подключены к шине управляющт х си! налов (2 ), Недостатком такого устроиства

ЯВ>ттт-:Ет Я НИЗКаЯ ТОЧНОСТЬ ВВИД..> НЕвысокого коэффициента усиления.

Цель изобретения †. Говышение Оч"J C .нотти путем увеличения коз;. >фициента усиления.

P„fÿ достижения поставленной цели в !co»rrаратор на КДП-транзисторах, содержащия дифференц;-.:,альный каскад„, дв=-..-..;онде: †."атора два транзистора,, КаЛДЬ!тт Иэ КОТОРЫХ ПОДКЛЮЧЕН СООТВЕтствет.!-;..: между прямым вхсдом %. инверсным выходом и между инверсным вхо-.

ДОМ И . „РЯМЬ!М ВЬ!ХОДО!:т ДнффЕРe,нт)наЛт ного каскада, прямой и инверсный зхОды котс-:Ого пОдключены сОстзе f ственйо к первым выводам первогс и второгс конденсаторов, а за.. ворь. транзисторов подключены к шине -;правлякших сигналов, введены третий„ етвертый, пятый и шестой транзис; 01b, . два дополнительных конденсатора,. при этом каждый,цополнительный конденсатор подключен соответственно между прямыми вхоцом и выхсдом

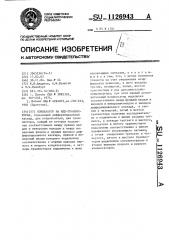

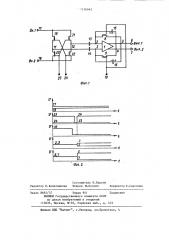

H неве,ioным вхОдом H вьГходом диффе ренциально-..с каскада. а третий и че"::àf ðf é,, пят-тй н же=той транзист«ры включены последовательно и подключены к шинам входных сигналов, а затворы третьего и ш.-стого, четвертого и пятого транзисторов подключены coîòâåòñòf-:àfrío к шинам парафазнаго управляющего сигнала, а точки соединения третьего и четвертого„ пятого и шестого транзисторов подключены соответственно к вторым выводам второго и первого конденсаторов, На фиг,1 представлена принципиальная электрическая схема предлагаемого компаратора на ЩП-транзисторах, на фиг,2 — эпюры напряжений управляющих, входных и выходных сигналов.

Компаратор на МДП-транзисторах содержит дифференциальный каскад 1 с прямыми и инверсными входами ?, 3 и выходами 4 и 5„ годключеннымтт к выХОДНЫМ ШниаМ б И 7 КОМ!таРатОРа, а между прямым входом 2 и инверсным выходом 5 и между инверсным входом прямым выходом 4 включены ком1 мутационные транзисторы 8 и 9 обратной связи, затворы которых подключень к ш не 10 упразлякщет о сигнала,. прч этом между входами ., 3 ттифо>ерев :.".Яально а каскада ) к тс чкы и !

)2 соеди";ения подключены перва;й и втооой конценсаторы !3 !4, конденсаторы )3, )б, а к шинам входных ИГНаЛОВ 1 т ., 18 ПОдКЛЮ-:ЕНЬ; rfO< fe>>Oлат ель ;0 соединенные грет- и . 9 -.; чет;.:::.- тый 20,, пя ть, . 2 . я шес;ой 22 тран"-исторь, а =-атворы тре; . его I9 и шесТОГО 22., четвертОГО 20 и лятОт..о 2 )

- .ранз-;сторов подключены соо,aåтственно к ш =,нам ?3. 24 парафазного управЛЯЮЩЕГО Снт.-;I, ДнаГраММЫ НалвяжЕНттй В уЗЛаХ КОМ.тарато >р приттэедены на >та!", 2, Коьтпаратс.. им. .ет два режима работы: на-: рой.-,и -f ar-:ò oêoðof>êUêf: и р; бочий зежим

РажHe ИЯ „т- CK. "MУ,, dCTРойктв ти KGPPEK—

ЦИИ,ООТЗЕТСТ ) ЕТ ВЫСОКИЙ 5тРОB(НЬ нат )>яжения !>а шине 1 0 уп)>авляющего с-:=.Г!-. тта. При этом транзис".Орь 8 и

9 в цепи обратной связи дифференЦИЙЛЬНОГО Кае ;аца 0ÒÊ)>b:fbf, а. т- .а е с входах и зыходах устанавливаетОЯ приблизи сель -. 0 Один и тот же "Do= вень напряжения. соответствующий ра".:очей точке дифференциа;тьного кас-т,,,--,=-:, ), rro ПОСТОЯННОМУ ТОКУ. Пст-,в!Е обкттадки конденсаторсВ и ) 4 с-вяЗИ OÊаЗЫВаштСЯ ттОДКЛ!тЧЕННЫМИ,; ibIX0дам 5 и 4 дифференциаль «or 0 каска!! 26943 да I, а вторые обкладки конденсаторов 13 и !4 через открытую пару транзисторов ??апример, 20, 21 ) подклю-чены к шинам 17 и 18 входного сигнала. Транзисторы 20 и 21 открыты 5 высоким уровнем коммутационного парафазного сигнала на шине 23 ° Транзисторы 19 и 22 заперты. В режиме настройки и корректировки конденсаторы 13 и.14 заряжаются до разных значений ??апряжений, эта разность равна разности напряжений на вход-, ных шинах 17, 18 компаратора, При появлении на шине 10 управляющего сигнала низкого уровня напряжения 5 транзисторы 8 и 9 обратной связи запираются. Компаратор выходит из режима настройки и корректировки, однако напряжение на выходных шинах

6 и 7 не изменяется, поскольку на- 20 пряжение на входах 2 и 3 дифференциального каскада 1 остается прежним. Ситуация на входах и выходах дифференциального каскада 1 не изменяется с появлением низкого уровня напряжения на шине 23. При этом оказываются запертыми транзисторы 19 — 22, С появлением высокого уровня напря-. жения на шине 24 отпираются транзисторы 19, 22 и конденсаторы 13, 14 связи оказываются подключенными каждый к входу компаратора, противоположному тому, к которому этот конденсатор был подключен в режиме настройки. Через конденсаторы связи 13, 14 на входы 2 и 3 дифференциального каскада 1 поступает перепад напряжения, равный разности напряжений на входных шинах и, кроме того, разности напряжений, на которую были за- 4> ряжены конденсаторы связи в режиме настройки.

Таким образом, на входах 2, 3 дифференциального каскада 1 происходит удвоение разности входных напряжений компаратора.

Коэффициент усиления компаратора определяется не только размерами нагрузочных и управляющих транзисторов дифференциального каскада 1, но и отношением емкостей конденсаторов связи к паразитным межэлектродным емкостям, и в первую очередь емкостям затвор — сток управляющих транзисторов, поскольку они находятся в цепи обратной связи дифференциального каскада. Кроме того, коэффициент усиления дифференциального каскада ограничинается ввиду нелинейности нагрузочных транзисторов.

Все эти ограничения, присущие прототипу и снижающие коэффициент усиления дифференциального каскада, устраняются введением в компаратор конденсаторов 15 и 16 положительной обратной связи. Емкость конденсаторов 15,16 выбирается такой, чтобы

eMKocT?iBÿ положительная обратная связь скомпенсировала все.элементы отрицательной обратной связи дифференциального каскада, Использование в компараторе предлагаемой схемы коммутатора входного сигнала позволит в два раза увеличить коэффициент усиления и, следовательно, повысить точность сравнения, Введение компенсирующих конденсаторов положительной обратной связи повышает коэффициент усиления в

3-4 раза без опасности появления триггерного эффекта.

1126943

Зых 1

Составитель Н.Маркин

Редактор О,Колесникова Техред М.Кузьма.

Корректор Е.Сирохман

Заказ 8692/31 Тираж 841

ВНИИПИ Государственного комитета СССР цо делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Подписное

Филиал ППП "Патент", г.ужгород, ул.Проектная, 4