Устройство для ввода информации

Иллюстрации

Показать всеРеферат

1. УСТРОЙСТВО ДПЯ ВВОДА ИНФОРМАЦИИ , содержащее регистр, коммутатор и блок управления, выходы первой группы которого соединены с входами первой группы коммутатора, отличающееся тем, что, с целью повышения быстродействия, в него введенгы счетчик, мультиплексор , группа счетчиков и блок памяти, входы счетчиков группы являются входами устройства, первые выходы счетчиков группы соедине.ны с входами первой группы регистра, входы второй группы которого соединены с выходами группы коммутатора, входы второй группы которого соединены с выходами регистра, выходы первой группы блока управления соединены с входами первой группы мультиплексора, входы второй группы которого соединены с вторыми выходами счетчиков группы, вход коммутатора соединен с третьим выходом блока управления, первый выход которого соединен с входом мультиплексора и является управляющим выходом устройства, выход коммутатора соединен с входом счетчика , выходы группы которого соединены с входами второй группы блока памяти и являются информационными выходами группы устройства, выходы второй группы блока управления соединены с входами первой группы блока памяти и являются адрескь ъш выходами устройства, первый вход блока памяти соединен с четвертым выходом блока управления, второй выход которого соединен с вторым вхо дом. блока памяти, выходы группы которого соедрпшны с входами группы счетчика , выход мультиплексора является информационным выходом устройства. 2. Устройство по п.1, о т л и чающееся тем, что блок управления содерж1-5т счетчик адресов, дешифратор, первый, второй, третий и четверть элементы задержки, генератор импульсов, выход которого соединен с входом счетчика адресов и входом первого элемента задержки, выход которого соединен с входом второго элемента задержки и являетю о ся четвертым -выходом блока управления , выход второго элемента задержсо 4; ки соединен с входом третьего элемента задержки и является третьим ел выходом блока управления, выход третьего элемента задержки соединен с входом четвертого элемента задержки и является первым выходом блока управления, выход четвертого элемента задержки является вторым выходом блока управления, выходы счетчика адресов соединены с входами дешифратора и являются выходами второй группы блока управления, выходы дешифратора являются выходами первой группы блока управления.

СОЮЗ СО6ЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ

ОПИСАНИЕ ИЗОБРЕ

И ABTOPCHOMV СВИДЕТЕЛЬСТВУ

;21) 3624447/24-24 (22) 19.07.83 (46) 30.11.84. Бюл.М 44 (72) В,П.Пачугин, А.Ю.Веревкин и 10.С Мануйлов (53) 681.326,34(088.8) (56) 1, Авторское свидетельство СССР

У 352270, кл. G 06 F 3/04, 1972.

2, Авторское свидетельство СССР

У 561954, кл. С 06 F 3/04., 1977 (прототип). (54)(57) 1. УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ, содержащее регистр, коммутатор и блок управления, выходы первой группы которого соединены с входами первой группы коммутатора, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия, B него введены счетчик, мультиплексор, группа счетчиков и блок памяти, входы счетчиков группы являются входами устройства, первые выходы счетчиков группы соединены с входами первой группы регистра, входы второй группы которого соединены с Выходами группы коммутатора, входы второй группы которого соединены с выходаии регистра, выходы первой группы блока управления соединены с входами первой группы мультиплексора, входы второй группы которого соединены с вторыми выходами счетчиков группы., вход коммутатора соединен с третьим выходом блока управления, первый выход которого соединен с входом мультиплексора и является управляющим выходом устройства, выход коммутатора соединен с входом счетчика, вьгходы группы которого соеди„„Я0„„1126945 иены с входами второй группы блока памяти и являются информационными выходами группы устройства, выходы второй группы блока управления соединены с входами первой группы блока памяти и являются адресными выходами устройства, первый вход блока памяти соединен с четвертым выходом блока управления, второй выход которого соединен с вторым входом блока памяти. выходы группы которого соединены с входами группы счет" чика, выход мультиплексора является информационным выходом устройства.

2. Устройство по п.1, о т л и— ч а ю щ е е с я тем, что блок управления содержит счетчик адресов, дешифратор, первый, второй, третий и четвертый элементы задержки, гене ðàòîð импульсов, выход которого соединен с входом счетчика адресов и входом первого элемента задержки, выход которого соединен с входом второго элемента задержки и является четвертым выходом блока управления, выход второго элемента задержки соединен с. входом третьего эгемента задержки и является третьим выходом блока управления, выход третьего элемента задержки соединен с входом четвертого элемента задержки и является первым выходом блока управления, выход четвертого элемента задержки является вторым выходом блока управления, выходы счетчика адресов соединены с входами дешифратора и являются выходами второй группы блока управления, выходы дешифратора являются выходами первой группы блока управления, М 11269

Изобретение относится к автоматике .и вычислительной технике и может быть использована как входное устройство в цифровых вычислительных машинах.

Известно устройство многоканального приема и накопления дискретной информации, содержащее блок накопления, блок. сопряжения с датчиками, выход которого соединен с первым вхо- 1О дом блока местного управления, причем два входа блока сопряжения с датчиками соединены с входами устройства, второй вход и второй выход блока местного управления соединены соответственно с третьим входам и управляющим выходом устройства 1 ).

Недостаток устройства — большие аппяратурные затраты, значительно возрастающие с увеличением числа подключаемых датчиков.

Наиболее близким к предлагаемому является устройство для ввода инфор-. мации, содержащее приемный регистр, . входной коммутатор, выходной коммутатор, сумматор и регистры по числу подключаемых датчиков, причем информационный выход приемного регистра соединен с информационным входом входного коммутатора информационные входы сумматора соединены соответственно с выходами входного коммутатора и выходного коммутатора, инфор— мационные входы которого соединены с выходами регистров, информационные входы которых соединены с выхо- 35 дом сумматора и информационным выходом устройства, первый вход приемного регистра соединен с выходом блока сопряжения с датчиками, управляющие входы приемного регистра, входного и выходного коммутаторов, сумматора.и регистров соединены с первым выходом блока местного управ пения, второй выход которого является управляющим выходом устройства, а вход соединен с выходом блока сопряжения с датчиками (2 1.

Недостаток устройства — низкое, быстродействие, что не позволяет применять его для ввода сигналов вы- Ы сокой частоты либо для ввода низкочастотных сигналов, но с большого числа датчиков.

Цель изобретения — повышение быстродействия устройства. 55

Поставленная цель достигается тем, что в устройство для ввода информации, содержащее регистр, кок45 2 мутатор и блок управления, выходы первой группы которого соединены с входами первой группы коимутатора, введены счетчик, мультиплексор, группа счетчиков и блок памяти, входы счетчиков группы являются входами устройства, первые выходы счетчиков группы соединены с входами первой группы регистра, входы второй группы которого соединены с выходами группы коммутатора, входы второй гр:пны которого соединены с выходами регистра, выходы первой группы блока управления соединены с входами первой группы мультиплексора, входы второй группы которого соединены с вторыми выходами счетчиков группы, вход коммутатора соединен с третьим выходом блока управления, первый Выход которого соединен с зходом мультиплексора и является управляющим выходом устройства, выход коммутатора соединен с входом счетчика, выходы группы которого соединены с входами второй группы блока гамяти и являются информационными выходами группы устройства, выходы второй группы блока управления соединены с входами первой группы блока памяти и являются адресными выходами устройства, пер"ый вход блока памяти соединен с четвертым выходом блока управления, второй выход которого соединен с вторым входом блока памяти, выходы группы которого соединены с входами группы счетчика, выход мультиплексора является информационным выходом устройства, при этом блок управления содержит счетчик адресов, дешифратор, первый, второй, третий и четвертый элементы задержки, генератор импульсов, выход которого соединен с входом счетчика адресов и входом первого элемента задержки, выход которого соединен с входом второго элемента задержки и является четвертым выходом блока управления, выход второго элемента задержки соединен с входом третьего элемента задержки и является третьим выходом блока управления, выход третьего элемента задержки соединен с входом четвертого элемента задержки и является первым выходом блока управления, выход четвертого элемента задержки явля< тся вторым выходом блока управления, выхо-,цы счетчика адресов соедиве:.ы с входами дешифратора и являются выходавает к аткрытию j-й элемент И !О, и одновременно поступает на вход 2 ° мультиплексора 2, подготавливал к открытию элементы И 8 во всех его разрядах.

Через время задержки „ с элемента 14 задержки снимается управляющий сип!сл чтения, который, посту пив »а вход 2! блока 7 "àìÿòè, осуществляет запись содержимого 1-ой ячейки в счетчик 6.

Через время %2 сигнал с элеме ша

15 задержки поступает на вход 25 коммутатора 4. Если 1-й разряд регистра 3 находится в единичном состоянии, та через !-й элемент И 10 и элемент ИЛИ 11 этот сигнал поступает на вход счетчика 6, прибавляя (вычитая ) единицу, и поступает на вход установки в нулевое состояние

)-го разряда рег.-.стра 3, Через время i, с элемента 16 задержки снимается управляющий сигнал, который, поступив на вход 26 мультиплексора 2 по ранее установленному

)-му адресу, осуществляет выдачу содержимого j-ro счетчика 1 на выход мультиплексора 2. В результате указан ых действий на выходе 27 устройства в этот момент времени присутствует управляющий сигнал, сопровождающий выдачу информации.

Через время i,1 с элемента 17 задержки снимается управляющий сигнал записи, который, поступив на вход 22 блока 7 паь яти, осуществляет запись в i-ю ячейк . памяти полученного, кода с счетчика 6.

С гриходам следующегс, импульса от генератора 18 формируется (j+1I -й адрес H работа устройства повторяет-. ся.

Введение в устройство блока памяти, счетчика, мультиплексора и группы счетчиков но числу подключаемых дат IKGB позволяет повысить быстродействие устройства эа счет буферизации входных сигналов на входных счетчиках и накопления в ячейках блока памяти только числа переполнений этих счетчиков.

Предлагаемое устройство не требует дополнительных аппаратурных затрат, т.к, затраты на введение

Ю- разрядных входных счетчиков компенсируются соответствующим уменьшением разрядности ячеек блока памя. ти, а также пр.-менением в предлагаемом устройстве вместо (6 +в)-разряд15

3 1126945 4 . ми второй группы блока управления, выходы дешифратора являются выходами первой группы блока управления.

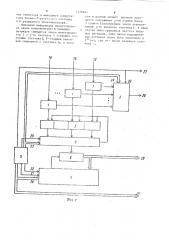

На фиг.l изабражеча структурная схема устройства для ввода информации, на фиг,2 — структурная схема

5 одного из мультиплексоров, на фиг,3— структурная. схема коммутатора, на фиг.4 - структурная схема блока управления.

1О

Блок-схема устройства (фиг,!) содержит счетчики 1 группы, мультиплексор 2, регистр 3, коммутатор 4, блок 5 управления, счетчик 6, блок

7 памяти °

Мультиплексор 2 содержит фиг,2) группу элементов И 8, элемент ИЛИ 9.

Коммутатор 4 содержит (фиг.3) группу элементов И 10, элемент ИЛИ

1l.

Блок 5 управления содержит дешифратор 12, счетчик 13 адресов, первый 14, второй 15, третий 16, четвертый 17 элементы задержки, генератор 18 импульсов.

На фиг,l- — 3 обозначены .соответственно. входы 19 устройства, вторые

20 выходы группы блока 5 управления,. первый 21 и второй 22 выходы блока 5 управления, первые 23 входы группы коммутатора 4, первые 24 входы группы мультиплексора 2, третий 25 выход блока 5 управления, вход 26 мультиплексора 2, управляющий 27 выход устройства, информационный 28 выход устройства, информационные 29 выха- 35 ды группы устройства, адресные 30 выходы устройства.

Устройство работает следующим образом, Входные сигналы, поступив на вхо- 40 ды 19 устройства, накапливаются в счетчиках l,число которых соответствует числу подключенных датчиков.

Сигналы переполнения счетчиков 1 запоминаются в регистре 3. Счетчик 45

13 адресов блока 5 управления последовательно формирует адреса ячеек блока 7 памяти.

Прн формировании j-го адреса происходит следующее, 50

Импульс от генератора 18 поступает на счетчик 13 адресов и эле- . мент 14 задержки. Сформированный на счетчике 13 адрес подается на вход

2G блока 7 памяти, на выход 30 ус- 55 тройСтва и одновременно на дешифратор 12,сигнал с которого, поступив нг вход 23 коммутатора 4, подготавли1126945

« пых сумматора и выходного коммутатора только Г-развядного счетчика и п-разрядного мультиплексора.

Выходная информация представляе".» ся двумя компонентами:rn -младших разрядов снимаются через мультиплексор 2 с -го счетчика t (текущее состояние счетчика 1, 1 †старш разрялов снимаются с счетчика б„ в котором в данный момент времени находится содержимое j-ой ячейки блока

7 г:амяти (накопленное число переполнений «-го входного счетчика f. В этом случае либо граничная частота входных сигналов, либо число подключенных датчиков может быть увеличено в

2 " раз, где tn — число разрядов счетчика

1126945

Раж 698 БОЩЛСКОЕ