Цифровой экстраполятор

Иллюстрации

Показать всеРеферат

ЦИФРОВОЙ ЭКСТРАПОЛЯТОР, содержащий блок управления, первый регистр, информационные входы которого подключены к первым входам соответствующих элементов И первой группы , выходы которых подключены к со- . ответствующим информационным входам первой группы первого сумматора, информационный выход которого подключен к информационному входу второго регистра, информационные выходы которого подключены к первым входам соответс вующих элементов И второй группы, выходы которых подключены к соответствующим информационным входам первой группы второго сумматора, информационный выход которого подключен к информационному входу преобразователя код-частота,- информационньш выход которого подключен к счетному входу реверсивного счетчика, информационньй вход которого поразрядно соединен с информационными входами второй группы первого сумматора , информационным входом первого регистра и является информационным входом экстраполятора, первьш и второй знаковый выходы второго сумматора подключены соответственно к суммирующему и вычитающему входам реверсивного счетчика, информационный выход которого является информационным выходом экстраполятора, отличающийся тем, что, с целью упрощения экстраполятора, он содержит третью группу элементов И, информационньй выход первого сумматора подключен поразрядно к первым входам соответствующих элементов И третьей группы, выходы которых подключены к соответствую 191м информационным входам второй группы второго сумматора, причем блок управления содержит элемент ИЛИ, формирователь (Л импульсов, триггер, генератор опор ной частоты, элемент И и сдвиговый регистр, тактовый вход которого подключен к выходу элемента И, первый вход которого подключен к выходу триггера, вход установки в единицу которого подключен к выходу формирователя импульсов, вход которого подключен к выходу элемента ИЛИ, входы которого соединены поразрядно с информационным входом первого регистра, выход генератора опорной частоты подключен к второму входу элемента И, . выход четвертого разряда сдвигового регистра подключен к входу обнуления сдвигового регистра, входу установки в ноль триггера и синхровходу преобразователя код-частота, выход первого разряда, .сдвигового регистра подключен к вторым входам элементов И первой группы и установочному входу реверсивного счетчика, выход второго разряда сдвигового регистра подклю

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (1% (И) А

g(51) С 06 F 15/353

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

И АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ GGCP пО делАм изоБРетений и oTHpblTMA (21) 3618213/24-24 (22) 11.07.83 (46) 30. 11.84. Бюл. И - 44 (72) В.Н.Попов, Н.А.Сипягин, В.Н.Лебедев и Б,А.Савельев (71) Пензенский политехнический институт (53) 681.32(088.8) (56) 1. Авторское свидетельство СССР

N - 694865, кл. G 06 F 15/20, 1979.

2. Авторское свидетельство СССР

N - 896632, кл. G 06 F 15/353, 1982 (прототип}. (54)(57} ЦИФРОВОЙ ЭКСТРАПОЛЯТОР, содержащий блок управления, первый регистр, информационные входы которого подключены к первым входам соответствующих элементов И первой группы, выходы которых подключены к соответствующим информационным входам первой группы первого сумматора, информационный выход которого подключен к информационному входу второго регистра, информационные выходы которого подключены к первым входам соответствующих элементов И второй группы, выходы которых подключены к соответствующим информационным вхо-. дам первой группы второго сумматора, информационный выход которого подключен к информационному входу преобразователя код-частота, информационный выход которого подключен к счетному входу реверсивного счетчика, информационный вход которого пораз-. рядно соединен с информационными входами второй группы первого сумматора, информационным входом первого регистра и является информационным входом экстраполятора, первый и второй знаковый выходы второго сумматора подключены соответственно к суммирующему и вычитающему входам реверсивного счетчика, информационный выход которого является информационным выходом экстраполятора, о т л ич а ю шийся тем, что, с целью упрощения экстраполятора, он содер>кит третью группу элементов И, информационный выход первого сумматора подключен поразрядно к первым входам соответствующих элементов И третьей группы, выходы которых подключень> к соответствующим информационным входам второй группы второго сумматора, причем блок управления Й содержит элемент ИЛИ, формирователь у импульсов, триггер, генератор опор- %Ф Ф

1ной частоты, элемент И и сдвиговый С регистр, тактовый вход которого подключен к выходу элемента И, первый . вход которого подключен к выходу триггера, вход установки в единицу которого подключен к выходу формирователя импульсов, вход которого подключен к выходу элемента ИЛИ, входы которого соединены поразрядно с информационным входом первого регистра, выход генератора опорной частоты подключен к второму входу элемента И, выход четвертого разряда сдвигового регистра подключен к входу обнуления сдвигового регис1ра, входу установки в ноль триггера и синхровходу преоб-,фВ разователя код-частота, выход первого разряда .сдвигового регистра подключен к вторым входам элементов И первой группы и установочному входу реверсивного счетчика, выход второго разряда сдвигового регистра подклю1126970 раполятора. чек K синхровходу перво"о регистра, синхронходу первого сумматора, вторым входам элементов И третьей группы, вторым входам элементов И второй группы и синхровходу реверсивного

Изобретение относится к вычислительной технике и может использовать ся в цифровых системах автоматического, управления.

Известен цифровой экстраполятор, 5 содержащий регистр памяти, элемент И, параллельный сумматор, преобразователь код-частота, реверсивный счетчик и устройство управления (1) .

Недостатком известного цифрового экстраполятора является низкая тач" ность экстраполяции, что обуславливается игнорированием информации на предпоследнем шаге экстраполяции.

Наиболее близким к предлагаемому являетсн цифровой экстраполятор, содержащий первый регистр, первую группу элементов И, первый (параллельный) сумматор, преобразователь код-частота, реверсивный счетчик, И второй (параллельный) сумматор, третий (параллельный) сумматор, второй регистр, вторую группу элементов И., блок управления, первый, второй, третий, четвертый, пятый выходы блока управления годключены к управляющим входам соответствующих узлов экстраполятора, первый регистр, первая группа элементов И, первый сумматор, второй регистр, первая 30 группа элементов И, второй сумматор, преобразователь код-частота,. реверсивный счетчик соединены последовательно (2) .

Недостатками данного устройства являютсн низкая скорость работы (для реализации алгоритма вычисления экстраполируемого отсчета требуется пять тактов, что наряду с большим числом необходимых операций суммирования определяет низкую скорость работы устройства), ограниченная область примепения н системах обработки информации, работающих в реаль ном масштабе времени, необходимость счетчика, выход третьего разряда сдвигового регистра подключен к третьим входам элементов И третьей группы и синхровходу второго регистра. применения третьего сумматора, что усложняет аппаратурную реализацию и снижает надежность работы всего устройства.

Цель изобрегения — упрощение экстПоставленная цель достигается тем, что цифровой экс panoлятор, содержащий блок управления, первый регистр, информационные выходы которого подключены к первым входам соответствующих элементов И первой группы, выходы которых подключены к соответствующим информационньм входам первой группы первого сумматора, информационный зыход которого подключен

R HíôñðìÿöHoííoìó входу второго регистра, информационные выходы которого подключены к первым входам соответствуюпулх элементов И второй труппы, выходы которых подключены к соответствующим информационным входам первой группы второго суммагора, информационнык выход котoporo подключен к информационному входу преобразователя код-частота, информационный выход которого подключен к счетному входу реверсивного счетчика, информационный вход которого поразрядно соединен с информационными входами второй группы первого сумматора, информационным входом первого регистра и является информационным входом экстраполятора, первый и второй знаковый выходы второго сумматора подключены соответственно к суммирующему и вычитающемс. входам реверсивного счетчика, информационный выход которого является информационным выходом экстрапаля гора, содержит третью группу элементов И, информационный выход первого сумматора подключен поразрядно к первым входам соответствующих элементов И

126970

К.5 gn(nN;(nj-n N;(n)(.

С выхода 16 блока 10 управления поступает четвертый тактовый импульс, запускающий преобразователь 4 код55 частота, на первый вход которого поступает с выхода сумматора 3 код.разности К, который преобразуется в частоту следования импульсов..третьей группы, выходы которых под-ключены к соответствующим,информационным входам второй группы второго сумматора, причем блок управления содержит элемент ИЛИ, формирователЬ импульсов, триггер, генератор опорной частоты, элемент И и сдвиговый регистр, тактовый вход которого подключен к выходу элемен; та И, первый вх д которого подключен к выходу триггера,,вход установки в единицу которого подключен к выходу формирователя импульсов, вход которого подключен к выходу элемента ИЛИ, входы которого соединены поразрядно с информационным входом первого регистра, выход генератора опорной частоты подключен к второму входу элемента И,. выход четвертого разряда сдвигового регистра подключен к входу обнуления сдвигового регистра, входу установки в ноль триггера и синхровходу преобразователя код-частота, выход первого разряда сдвигового регистра подключен к вторым входам элементов И первой группы и установочному входу реверсивного счетчика, выход второго разряда сдвигового регистра подключен к синхровходу первого регистра, синхровходу первого сумматора, вторым входам элементов И третьей группы, вторым входам элементов И второй группы и синхровходу реверсивного счетчика, выход третьего разряда сдвигового регистра подключен к третьим входам элементов И третьей группы н синхровходу второго регистра.

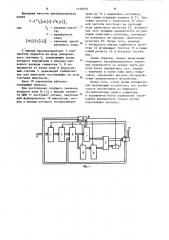

На фиг. 1 представлена структурная схема цифрового экстраполятора; на фиг. 2 — блок-схема блока управления.

Экстраполятор содержит регистр 1, гру((у 2 элементов И, параллельный сумматор 3, преобразователь 4 кодчастота, реверсивный счетчик 5, параллельный сумматор 6, группу 7 элементов И, регистр 8, группу 9 элементов И, блок 10 управления, информационный вход 11, ичформационный выход 12, выходы 13 — 16 блока управления.

Блок 10 управления содержит элемент ИЛИ 17, формирователь 18 импульсов, триггер 19, генератор 20 опорной частоты, элемент И 21, сдвиговый регистр 22, 4

Устройство работает следующим образом.

При поступлении текущего значения входного кода N; Pn), его предшествующее значение (1, $n) по тактовому импульсу с первого выхода 13 блока 10 управления переписывается в сумматор 6 а реверсивный счетчик 5 обнуляется. После этого, вторым так10 товыи импульсом с выхода 14 блока 10 управления, текущее значение N;(n) записывается в регистр 1, в реверсивный счетчик 5 и заносится в суииатор 6, в котором вычисляется первая

15 конечная разность ьи,(.g.è,(.)-н;,(.1.

Код разности g N<(n) третьим тактовым импульсои с выхода 15 блока 10

20 управления записывается в регистр 8 и заносится в сумматор 3, причем занесение происходит через группу 9 элементов И с сдвигом на один разряд в сторону старших разрядов, чем достигается умножение на два. В это время в сумматоре 3 уже находится код а, 11;, (n) = 1;, Ж -, "; 2 p n), 1юлученный в предыдущеи цикле работы экстраполятора и переписанный в него по второму тактовому импульсу через группу 9 элементов И иэ регистра 8.

В сумматоре 3 вычисляется разность

35 k --sign(paé; п)-aN,(n))

Перепишеи выражение в фигурных

,скобках управления (1) следующим образом:

24Н;И-aN;,Я=

=(ьй; jn)isign(aH;Kn)-((,11;, Pn)$ где Ь Н;(н)-Ь 8;,Я =В И;() — разность

45 второго порядка.

Окончательно перепишем (1) в виде:

112б970

Выходная частота преобразователя равна

F° - 2 "F (aH;(n)-ьай,(„)) — опорная частота; и — разрядность кода.; (aH;(n)-d; (n)5 — значение преобразуемого кода. где

С выхода преобразователя (4 кодчастота подается на вход реверсивного счетчика 5, управляющие входы которого подключены к выходам. знакового разряда сумматора 3. В зависимости от знака кода К реверсивный счетчик 5 производит суммирование или вычитание поступающих на вход счетчика импульсов.

Блок t0 управления работает следующим образом.

При поступлении .текущего значения входного кода И (qj с выхода элемен2 та ИЛИ 17 поступает сигнал, запускающий формирователь 18 импульсов, сигнал,с выхода которого устанавливает триггер )9 в единичное состояние, тем самым открывая элемент И 2 1. Тактовая частота с генератора 20 опорной частоты пост пает на тактовый вход сдвигового регистра 22., вследствие чего единица продвигается по разрядам сдвигового регистра, поочередно появляясь на выходах сдвигового регистра 22. Кроме того, единица

)О с четвертого выхода сдвигового регистра 22 возвращает триггер 19 и сдвиговый регистр 22 в исходное состояние.

Таким образом, задача вычисления очередного экстраполируемого значения реализуется эа четыре такта работы блока управления, что, наряду с наличием в схеме лишь двух сумматоров, определяет высокое быстродействие предлагаемого .устройства.

Кроме того, стала проще аппаратурная реализация устройства, что цости" гается исключением из цифрового экстраполятора одного сумматора

25 и упрощением блока управления (необходимо формировать только четыре управляющих сигнала).

"Составитель А.Баранов

Редактор А.Ревин Техред О.Ващинпсна Корректор И.Муска

Заказ 8741/38 Тирах 698 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г.ухгород, ул. Проектная, 4