Устройство для организации очередности приема информации

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИ4ЕСНИХ

РЕСПУБЛИН

M 59 G 06 F 9 46 С«:-д

ОПЙСАНИЕ ИЗОБРЕТЕНИ

H АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И OTHPblTHA (21) 3626941/24-24 (22) 27.07,.83 (46) 07,12.84. Бюл. Р 45 (72) А.В.Балаболин;. В.И.дронов, В.В.Левчук и В.A.Hèêèòàí (53). 681.325 (088.8) (56) 1.Авторское свидетельство СССР

9 834701,кл. G 06 F 9/46; 1981.

2. Авторское свидетельство СССР

9 851409,кл. G F 9/46,1981 (прототип). (54)(57 ) УСТРОЙСТВО . (ЛЯ ОРГАНИЭАЦИИ

ОЧЕРЕДНОСТИ ПРИЕМА .ИНФОРМАЦИИ, содержащее шифратор, элемент задержки, дешифратор, блок памяти, блок управления записью и считыванием, группу элементов И, распределитель импульсов, регистр, первый и второй элементы ЙЛИ, блок управления записью и считыванием содержит первый счетчик, счетный вход которого соединен с выходом первого элемента. ИЛИ, причем группа выходов дешифратора является группой информационных вйХОДОВ Устройства, выходы элементов И группы соединены с группой входов дешифратора и входами первого .элемента ИЛИ, выход каждого разряда регистра соединен с первым входом одноименного элемента И группы, вто- роа вход каждого элемента И группы . соединен с одноименным выходом рас- . пределителя импульсов, о т л и

„„SU„„j 128255 А ч а ю щ е е с я тем, что, с целью . повышения надежности, в него введена группа одновибраторов, вход каждого одновибратора соединен с запросным входом устройства к третьим входом соответствующего элемента И группы, выходы распределителя импульсов соединены с входами сброса соответствующих разрядов регистра, информационные входы которых соединены с выходами соответствующих одновибраторов группЫ, выходы регистра соединены с .входами второго элемента ИЛИ, выход которого через .элемент задержки подключен к запускаю- . щему входу распределителя импульсов", группа выходов -шифратора соединена @

И с группой информационных входов бло.ка памяти,, группа выходов которого соединена с входами дешифратора, блок управления записью и считывани- С ем содержит второй счетчик и схему сравнения, причем групгы выходов перЯ вого и второго счетчйков. соединены соответственно с первой и второй . ® группами входов схемы сравнения, вы- ход которой соединен с входом:бло-. кировки второго счетчика, счетный 3Я вход которого соединен с тактовым ("ф входом устройства, группы выходов первого и второго счетчиков соединены соответственно с группой вхо- (Я дов адреса считывания и с группой входов адреса записи блока памяти,, ЧФ .

1128255

Изобретение относится к области автоматики и вычислительной техники и может быть использовано в устройствах управления очередностью обслуживания.

Известно устройство для организации очередности, содержащее элемент ИЛИ, два счетчика, узел сравнения, причем группа входов элемента ИЛИ является группой запросных входов устройства, первый выход каждого счетчика соединен с соответствующим входом узла сравнения.

Устройство также содержит блок памяти, шифратор и дешифратор, причем адресный- выход шифратора соединен - 15 с адресным входом блока памяти, блокирующий выход шифратора соединен с первым нходом первого счетчика, выход- элемента ИЛИ соединен с вторым входом первого счетчика, первый. выход узла сравнения соединен с третьим входом первого счетчика, второй выход узла сравнения соединен с первым входом счетчика, второй вход которого является управляющим 25 входом устройства, второй выход каж- . дого счетчика соединен с соответст— вующим входом блока памяти, выход блока памяти соединен с входом де— шифратора, группа выходов дешифратора является группой выходов устройства, а группа входов шифратора — группой запросных входов устройст на 1 3. Однако данное устройство не обеспечивает органиэации очереди при

35 одновременном поступлении нескольких сигналов заявок, т.е. поступившие заявки остаются без обслуживания, что снижает надежность работы устройства. 40

Наиболее близким к изобретению по технической сущности и достигаемому результату является устройство для управления очередностью обслуживания запросов, содержащее ре- 45 гистр, группу элементов И, распределитель управлялщих сигналов, коммутатор, блок памяти, причем группа информационных входов регистра является группой информационных входов устройства, разрядные выходы регистра соединены с первыми входами соответствующих элементов И группы, группа выходов блока памяти соединена с первой группой входов коммутатора, первый выход распределителя управляющих сигналов соединен с входом коммутатора,.второй выход распределителя управляющих сигналов соединен с входом блока памяти. Устройстно также содержит генератор импульсов, шифратор, дешифратор, два элемента ИЛИ, счетчик, блок разделения сигналов, причем второй вход каждого элемента И группы соединен с соответствующим выходом генерато- 65 ра импульсов, третий вход каждого элемента И группы соединен с третьим выходом распределителя управляющих сигналов, выходы элементов И группы соединены с группой входов шифратора, группа выходов шифратора соединен с второй группой входов коммутатора, первая группа выходов коммутатора соединена с группой входон блока памяти, группа выходов элементов И группы соединена с группой управляющих входов регистра и с входами первого элемента ИЛИ, выход первого элемента ИЛИ соединен с пер вым входом коммутатора, с суммирующим входом счетчика и с первым входом блока разделения сигналов, группа входов второго элемента ИЛИ является группой управляющих входов устройства, выход второго элемента ИЛИ соединен с вторым входом блока разделения сигналов, выход которого соединен с вторым входом распределителя управляющих сигналов и с вычитающим входом счетчика, управляющий вход устройства соединен с управляющим входом счетчика и с третьим входом распределителя управляющих сигналов, выход счетчика соединен с четвертым входом распределителя управляющих сигналов, группа выходов дешибратора является группой информационных. выходов устройства (21.

Однако известное устройство не защищено от помех, наличие которых на входах устройства запоминается в регистре и обрабатывается как поступающие запросы. Кроме того, в случае присутствия на входах устройства запросов, длительность которых превышает цикл работы опросового генератора, возникает повторная обработка одних и тех же запросов, что также приводит к ложной регистрации запросов, снижающей достоверность передаваемой устройством информации.

Целью изобретения является повышение надежности.

Поставленная цель достигается тем, что в устройство для организации очередности приема информации, содержащее шифратор, элемент задержки, дешифратор, блок памяти, блок управления записью и считыванием, группу элементов И, распределитель импульсов, регистр, первый и второй элементы ИЛИ, блок управления записью и считыванием содержит первый счетчик, счетный вход которого соединен с выходом первого элемента ИЛИ, причем группа выходов дешифратора является группой информационных выходов устройства, выходы элементов И группы соединены с группой входов шифратора и входами первого элемента ИЛИ, выход каждого разряда регистра соединен с первым

1228255 входом одноименного элемента И груп- пы, второй вход каждого элемента И группы соединен с одноименным выходом распределителя .импульсов, введена группа одновибраторов, вход каждого одновибратора соединен с за.просным входом устройства и третьим входом соответствующего элемента И группы, выходы распределителя импуль сов соединены с входами сброса соответствующих разрядов регистра, информационные входы которых соединены с .выходами соответствующих одно.вибраторов группы, выходы регистра ,соединены с входами второго элемента ИЛИ, выход которого через элемент задержки подключен к запускающему входу распределителя импульсов, груп па выходов шифратора соединена с группой информационных входов блока памяти, группа выходов которого соединена с входами дешифратора, блок управления записью и считыванием содержит второй счетчик и схему сравнения, причем группа выходов пер вого и второго. счетчйков соединены соответственно с первой и второй группами входов схемы сравнения, выход которой соединен с входом блокировки второго счетчика, счетный вход которого соединен с тактовым входом устройства, группы выходов первого и второго счетчиков соединены соответственно с группой входов адреса считывания и -с группой входов адреса записи блока памяти.

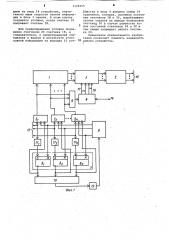

На фиг.1 представлена функциональная схема предложенного устройства; на фиг,2 — то же, блока управления записью и считыванием.

Устройство для организации очередности приема информации содержит шифратор 1, дешифратор 2, блок 3 памяти, блок 4 управления записью и считыванием, элементы И 5,-5 „ группы, распределитель б импульсов, .Регистр 7, триггеры 8 -8„ регистра 7, элементы ИЛИ 9 и 10, группу одновибраторов 11„-11„, элемент 12 задержки, запросные входы 13 устройства, тактовый вход 14 устройства, .информационные выходы 15 устройства, группы входов 16 и,17 адреса записи и считывания блока 3, Блок управления записью и считыванием (фиг.2) содержит счетчик 18, схему 19 сравнения, счетчик 20, Устройство работает следующим образом.

Перед началом работы устройствоприводится в исходное состояние, в результате чего триггеры 8 регист- ра 7, счетчики 18 и 20 блока 4 находятоя в исходном нулевом состоянии.

На информационных .входах триггеров 8 регистра 7 присутствует нулевой сигнал.

Затем информация поступает.на запросные входы 13 и далее на входы элементов И 5 группы и входы одновибраторов 11„ -11 „ гщ ппы, которые срабатывают по переднему фронту поступающего сигнала и выдают импульсы на информационные входы соответствующих триггеров 8 регистра 7, ко- торые срабатывают и выдают сигналы на входы соответствующих элементов И 5 группы и входы элемента ИЛИ 10.

Сигнал с выхода элемента ИЛИ 10 через элемент 12 задержки поступает на запускающий вход распределителя б, на выходах которого появляются сдвинутые друг относительно друга по времени импульсы.

Распределитель б по очереди оп- рашивают Элементы И 5 и одновременно сбрасывают соответствующие триггеры 8 регистра 7. Так как одновибраторы 11 по переднему фронту поступающего запроса формируют на вы ходах сигналы определенной длительности, поэтому присутствие на входах одновибраторов 11 длительных сигналов запроса не приводит к повторному срабатыванию триггеров 8. . С выходов соответствующих элементов И 5 сигналы по очереди поступают на входы шифратора 1 и через элемент ИЛИ 9 на счетный вход счетчика 18 блока .4.

Блок 4 работает следующим образом. Состояние выхода 16 изменяется сигналами, поступающими с выхода элемента HJIH 9, и считыванием. Этим самым определяется адрес ячейки па- ,мяти блока 3 памяти, куда осуществляется запись информации. Считыва40 ние информации из блока 3 памяти осу.ществляется по адресу, устанавливаемому на выходах счетчика 20, состояние которого изменяется сигналами, поступающими с входа 14 устройства.

45 В шифраторе 1 сигналы преобразуются в параллельный двоичный код., соответствующий номеру элемента И 5 и, следовательно, номеру запроса, поступающего на вход 13 устройства.

Этот код записывается в блок 3 памяти по адресу, установленному на выходах 16 блока 4.

Сигналы на считывание информации, из.блока 3 памяти поступают по входу 14 в блок 4, который на выходах 17 устанавливает адрес ячейки памяти, из которой необходимо считать информацию. Считанная из блока 3 памя- . ти информация после преобразования дешифратором 2 в позиционный код выставляется на информационных выходах 15 устройства.

Предлагаемое устройство предназначено для работы в условиях, когда скорость считывания информации из

65 блока 3 памяти сигналами, поступаю1128255 щими на вход 14 устройства, значи.тельно выще скорости записи информации в блок 3 памяти. В этом. случае создаются условия, когда счетчик 20 опережает счетчик 18, Для предотвращения условия опережения счетчиком 20 счетчика 18, -а следовательно, и предотвращения считывания и выдачи в результате этого ложной информации на выходах 15 устройства в блок 4 введена схема 19 сравнения, которая, оценивая состояние счетчиков 18 и 20, вырабатывает сигнал запрета на выходе блокировки счетчика 20 в случае равенства кодов состояний счетчиков 18 и 20 и тем самым запрещает работу счетчика 20. Применение предлагаемого изобретения позволяет повысить надежность работы устройства.

Составитель М.Кудряшев

Редактор А.Гратилло Техред M.Kóçüìà Корректор М.Максимишинец

Заказ 9063/37 Тираж 698 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, >(-35, Раушская наб., д. 4/5

Филиал ППЧ "Патент", г. Ужгород, ул. Проектная, 4