Дешифратор на мдп-транзисторах

Иллюстрации

Показать всеРеферат

ДЕШИФРАТОР НА МДП-ТРАНЗИСТОРАХ , содержащий группы транзисторов прямой и обратной проводимости, шины прямых входов, шины инверсных входов, выходные шины и шины питания, о тчличающийся тем, что, с целью повьшения надежности, первая и вторая группы транзисторов состоят из транзисторов прямой, а третья группа - ИЗ транзисторов обратной проводимости, истоки транзисторов первой группы соединены с первой шиной питании, сток первого транзистора первой г|)уппы соединен с истоками первого и второго транзисторов второй группы, а его затвор соединен с первой шиной прямого входа, сток второго транзистора первой группы соединен с истоками третьего и четвертого транзисторов второй группы. а его затвор - с первой шиной инверсного входа, стоки первого, второго третьего и четвертого транзисторов третьей группы соединены с второй шиной питания, затворы второго и третьего транзисторов второй группы соединены с затворами второго и третьего транзисторов третьей группы и с второй шиной инверсного входа, затворы первых и четвертых транзисторов второй и третьей группь соединены с второй шиной прямого входа,первая .выходная шина соединена со стоками первого транзистора второй группы и пя .того транзистора третьей группы, исi ток которого соединен со стоком второго транзистора второй группы, истоком второго транзистора третьей группы и второй выходной шиной, затвор пятого транзистора третьей группы соединен с затвором первого транS зистора первой группы, третья выходная шина соединена с истоком четвертого транзистора -третьей группы, стою ком четвертого транзистора второй Х группы и стоком шестого транзистора э ч ;о третьей группы, затвор которого соединен с первой шиной инверсного вхоi;t ,исток йёстого. транзистора третьей Ьруппы соединен с истоком третьего транзистора третьей группы, стоком третьего транзистора второй группы и четвертьй выходной шиной.

СОЮЗ COBETCHHX

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК.ОЮ (11) ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ фц „, ГОСУДАРСТВЕННЫЙ КОМИТЕТ. СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И OTHPbfAO (21) 3537748/24-21 (22) 10. 01. 83 (46) 07.12.84. Бюл. и 45 (72) С.В. Быков (53) 681.325.63(088.8) (56) 1. Евдокимов И.С. Цифровые вычислительные .машины. М., Госиздат, 1961, с. 437, фиг. 280.

2. Преснухин Л.Н., Нестеров П.В.

Цифровые вычислительные машины. М., "Высшая школа", 1981, с. 186, рис. 3/38 (прототип). (54)(57) ДЕШИФРАТОР НА МДП-ТРАНЗИСТОРАХ, содержащий группы транзисторов прямой и обратной проводимости, шины прямых входов, шины инверсных входов, выходные шины и шины питания, о т..— л и ч а ю шийся тем, .что, с целью повышения надежности, первая и вторая группы транзисторов состоят из транзисторов прямой, а третья группа — из. транзисторов обратной проводимости, истоки транзисторов первой группы соединены с первой шиной питания, сток первого транзистора первой группы соединен .с истоками первого и второго транзисторов второй группы, а его затвор соединен с первой шиной прямого входа, сток второго транзистора первой группы соединен с истоками третьего и- чет- вертого транзисторов второй группы, ЗСЮНОЗКО.НОЗК1324 а его затвор — с первой шиной инверс ного входа, стоки первого, второго, третьего и четвертого транзисторов третьей группы соединены с второй шиной питания, затворы второго и третьего транзисторов второй группы соединены с затворами второго и третьего транзисторов третьей группы и с второй шиной инверсного входа, затворы первых и четвертых транзисторов второй и третьей группы соеди-, нены с второй шиной прямого входа,йервая .выходная шина соединена со стоками первого транзистора второй группы и пя.того транзистора третьей группы, исток которого соединен со стоком вто- I рого транзистора второй группы, истоком второго транзистора третьей группы и второй выходной шиной, затвор пятого транзистора третьей группы соединен с затвором первого тран- д зистора первой группы, третья выходная шина соединена с истбком четвертого транзистора -третьей группы, стоком четвертого транзистора второй группы и стоком шестого транзистора третьей группы, затвор которого сое.. динен с первой шиной инверсного вхо- да,исток шестого. транзистора третьей

1руппы соединен с истоком третьего транзистора третьей группы, стоком третьего транзистора второй группы и четвертой выходной шиной.

1 1128

Изобретение относится к вычислительной технике и может быть использовано при разработке универсальных и специализированных цифровых вычислительных машин. 5

Известен дешифратор, содержащий ,резисторы, диоды и транзисторы, выходы которых подключены к соответствующим шинам дешифрато х через диоды Ц.

f0

Недостатком этого устройства является низкая надежность из-за большого количества компонентов в схеме.

Наиболее близким техническим ре- 15 шением к изобретению является дешифратор на МДП-транзисторах, содержащий группы транзисторов прямой и обратной проводимости, шины прямых входов, шины инверсных входов, вы- 10 ходные шийы, шины .питания и элементы И-НЕ, входы которых подключены к содтветствующим шинам прямых и инверсных входов, а выходы соединены с соответствующими выходными шина- 25 ми (2) .

Недостатком известного устройст-. ва является его низкая надежность.

Целью изобретения является повышение надежности.

Поставленная цель достигается тем, что в дешифраторе на ИДП-транзисторах, содержащем группы транзисторов прямой и обратной проводимости, шины прямых входов, шины инверсных вхо- 35 довх выходные шины и шины питания, первая и вторая группы транзисторов состоят из транзисторов прямой, а третья группа — из транзисторов об" ратной проводимости, истоки транзис- 40 торов первой группы соединены с пер-. вой шиной питания, сток первого транзистбра первой группы — с истоками первого и второго транзисторов второй группы, а его затвор — с пер- 45 вой шиной прямого входа, сток второго транзистора первой группы соединен с истоками третьего и четвертого транзисторов второй группы, а

его затвор — с первой шиной инверс- 50 ного. входа, стоки первого, второго, третьего и четвертого транзисторов третьей группы соединены с второй шиной питания, затворы второго и третьего транзисторов второй группы — 55 с затворами второго и третье.го транзисторов,третьей группы и с второй шиной инверсного вхо-

379 2 да, затворы первый и четвертых транзисторов второй и третьей группы— с второй шиной прямого входа, первая выходная шина — со стоками первого транзистора второй группы и пя- того транзистора третьей группы, исток которого соединен со стоком второго транзистора второй группы, истоком второго транзистора третьей группы и второй выходной шиной, зат- вор пятого транзистора третьей группы соединен с затвором первого транзистора первой группы, третья выходная шина — с истоком четвертого транзистора третьей группы, стоком четвертого транзистора второй группы и стоком шестого транзистора третьей группы, затвор которого соединен с первой шиной инверсного входа, исток шестого транзистора третьей группы соединен с истоком третьего транзистора третьей группы, стоком третьего транзистора второй группы и четвертой выходной шиной.

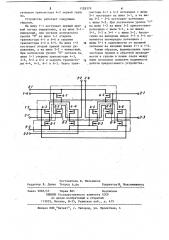

На чертеже представлена принципиальная электрическая схема дешифратора на МДП-транзисторах.

Дешифратор содержит шины 1.1 и 1.2 прямых входов, шины 2.1 и 2.2 инверсных входов, выходные шины 3.1 — 3.4, транзисторы 4.1 — 4.2, истоки транзисторов 4.1 и 4.2 подключены к первой шине питания, затвор транзистора

4.1 соединен с первой шиной 1.1 прямого входа, затвор транзистора 4.2— с первой шиной 2.1 инверсного входа, истока транзисторов 4.3 и 4.4 — со стоком транзистора 4-1 первой группы, транзисторы 4.5 и 4.6 истоками подключены к стоку транзистора 4-2 первой группы, стоки транзисторов 4-3— .4-6 — соответственно к выходным шинам

3.1 — 3.4, шины 5-1 и 5-2 — шины питания, причем истоки транзисторов

6-1 — 6-4 подключены к шине 5-2 питания, а затворы — к затвором транзисторов 4-3 — 4-6 второй группы соответственно затворы транзисторрв 4-3

1 и 4-5 соединены с второй шиной 1-2 прямого входа, затворы транзисторов

4-4 и 4-6 — с второй шиной 2-2 инверсного входа, между стоками транзисторов 4-3 и 4-4 включен транзистор 6-5, затвор которого подключен к затвору транзисторов 4-1 первой группы, между стоками транзисторов

4-5 и 4-6 включен транзистор 6-6

И-типа, затвор которого подключен к

Я У-4

Составитель Б. Мельников, Редактор В. Данко Техред А.Ач Корректор М. Максимишинец т

Заказ 9083/43 Тираж 861 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП,"Патент", г. Ужгород, ул. Проектная, 4

3 11283 затворам транзистора 4-2 первой груду пы.

Устройство работает следующим образом.

Hа шину 1-1 поступает первый пря1 ой сигнал управления, а на шину 2-1— инверсный, при сигнале логического уровня "0" на шине 1-1 открыты транзисторы 4-1 и 6-6 и закрыты транзисторы 4-2 и 6-5. На шину 1-2 1О поступает второй прямой сигнал управления, а на шину 2-2 — инверсный.

При логическом уровне "О™ сигнала на ! шине 1-1 открыты транзисторы 4-3, 4-6, 6-2 и 6-4 и закрыты транзисто,ры 4-4, 4-5, 6-1 и 6-3. Через тран79 4 зисторы 4-1 и 4-3 потенциал с шины

5-1 поступает на шину 3-1, а на шины 3-2 — 3-4 поступает потенциал с шины 5-2. При логическом уровне "1" на шине 1-2 на шине 3-2 присутствует потенциал с шины 5-1, а на шинах

3-1, 3-3 и 3-4 — с шины 5-2. Аналогично на выходных шинах 3-3 и 3-4 появляется поочередно потенциал с шины 5-1 в зависимости от уровней сигналов на входных шинах 1-1 и 1-2.

Таким образом, формирование транзисторов прямой и обратной проводимости в группы и новые связи между ними позволило повысить надежность работы предлагаемого устройства.