Преобразователь дельта-модулированного сигнала в сигнал с импульсно-кодовой модуляцией

Иллюстрации

Показать всеРеферат

ПРЕОБРАЗОВАТЕЛЬ ДЕЛЬТАМОДУЛИРОВАННОГО СИГНАЛА В СИГНАЛ С ИМПУЛЬСНО-КОДОВОЙ МОДУЛЯЦИЕЙ, содержащий реверсивный счетчик, первый Б-триггер,Р-вход которого соединен с выходом старшего разряда реверсивного счетчика, a вход синхронизациис шиной синхронизации, счетчик и первый логический блок, о т л и ч a ю щ и и с я тем, что, с целью повы-v шения помехоустойчивости, s него введены второй логический блок, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ и второйD-триггер , вход синхронизации которого соединен с шиной синхронизации, входом синхронизации реверсивного счетчика и входом счетчика, выход кбторого соединен с первьщ входом второго логического блока,,a вход установки в О счетчика - с выходом элемента ИСКЛЮЧАЮЩЕЕ ЙЛИ-НЕ, первый вход которого соединен с выходом первогоD-триггера, a второй вход подключен кD-входу первогоD-триггера и первому входу первого логического блока, второй вход которого соединен с вторым входом второго ло (Л гического блока и выходом второго D-триггера, третий вход первого логического блока соединен с входом устройства и входом управлейия ревер§ сивного счетчика, a выход - с входом запрета счета реверсивного счетчика и третьим входом второго лоЮ гического блока, выход которого сое00 динен с D-входом второго D-триггера, со сх ел

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУ БЛИН

0% (11) ОПИСАНИЕ ИЗОБРЕТ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

К ABTOPCHOMY СВИДЕТЕЛЬСТВУ

i (21) 3589898/24-21 (22) 06.05.83 (46). 07.12 ° 84 ° Бюл. № 45 (72) А,В. Брунченко, Ю.С. Власюк и Е.П..Охинченко (71) Ленинградский электротехнический институт связи им. проф. M.À. Бонч-Бруевича (53) 621.376.5(088.8) (56) 1. IEEE. Transactions on SolidState Circuits. 1981, v. 2 № 4, р. 31.

2. Авторское свидетельство СССР

¹ 930664, кл. Н 03 К 13/22,24.09 ° 80 (прототип). (54)(57) ПРЕОБРАЗОВАТЕЛЬ ДЕЛЬТАМОДУЛИРОВАННОГО СИГНАЛА В СИГНАЛ С

ИМПУЛЬСНО-КОДОВОЙ МОДУЛЯЦИЕЙ, содержащий реверсивный счетчик, первый

З-триггер, 3 -вход которого соединен с выходом старшего разряда реверсив-. ного счетчика, а вход синхронизации— с шиной синхронизации, счетчик и первый логический блок, о т л и ч а— ю шийся-тем, что, с целью повы- . шения помехоустойчивости, s него введены второй логический блок, элемент

ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ и второй Э-триггер, вход синхронизации которого соединен с шиной синхрОнизации входом синхронизации реверсивного счетчика и входом счетчика, выход которого соединен с первым входом второго логического блока, а вход уста" нонки в "0" счетчика — с выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ, первый вход которого соединен с выходом первогоП-триггера, а второй .вход подключен кВ -входу первого Р-триггера и первому входу первого логического блока, второй вход которого сое- Е динен с вторым входом второго логического блока и выходом второго

D-триггера, третий вход первого логического блока соединен с входом устройства и входом управления ревер- д сивного счетчика, а выход — с входом запрета счета реверсивного счетчика и третьим входом второго ло.гического блока, выход которого соединен сЗ -входом второгоЭ -триггера; !

1128385

Изобретение относится к импульсной технике и может быть использовано в системах обработки и передачи цифровых сигналов, в которых применяется дельта-модуляция (@PI) и импульсно-кодовая модуляция (ИКМ).

Известно устройство для преобразования ДМ сигналов в ИКМ, содержащее сумматоры, резисторы, умножители и постоянные запоминающие устройства (1) 10

Недостатком этого устройства является невысокая помехоустойчивость.

Наиболее близким к изобретению техническим решением является устройство для преобразования дельта- 15 модулированных сигналов в сигнал с

ИКМ, содержащее реверсивный счетчик, D-триггер, 3 -вход которого соединен с выходом старшего разряда реверсивного счетчика, а вход синхронизации — 20 с шиной синхронизации, управляемый делитель частоты, например, счетчик и первый логический блок, а также высокочастотный дельта-модулятор, прямой и инверсный выходы которого 25 через элементы И подключены к входу управления реверсивного счетчика, и генераторы тактовых импульсов (2) .

Недостатком известного устройства является низкая помехоустойчивость, gp что вызывает изменение уровня постоянной составляющей s выходном ИКМ сигнале при возникновении сбоев в ДМ сигнале и приводит к искажению передаваемых сигналов. Это обусловлено тем, что р :.версивные счетчики являются идеальными интеграторами, вследствие чего они накапливают ошибки. с

Цель изобретения — повышение помехоустойчивости.

Цель достигается тем, что в преобразователь дельта-модулированного сигнала в сигнал с импульсно-кодовой модуляцией, содержащий реверсивный счетчик, первыйЗ -триггер,2— вход которого соединен с,выходом старшего разряда реверсивного счетчика, а вход синхронизации — с шиной синхронизации, счетчик и первый логический блок, введены второй логи.ческий блок, элемент ИСКЛЮЧАЮЩЕЕ

ИЛИ-НЕ и второй 2 -триггер, вход синхронизации которого соединен с шиной синхронизации, входом синхронизации реверсивного счетчика и входом счет- 55 чика, выход которого соединен с первым входом второго логического блока,,а вход установки в "0" счетчика — с выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ, первый вход которого соединен с выходом первого D -триггера, а второй вход подключен к D -входу первого D -триггера и первому входу первого логического блока, второй вход которого соединен с вторым входом второго логического блока и выходом второго

))-триггера, третий вход первого блока соединен с входом устройства и входом управления реверсивного счетчика, а выход — с входом запрета счета реверсивного счетчика и третьим входом второго логического блока, выход которого соединен сD -входом второго д -триггера, На чертеже представлена функциональная схема устройства.

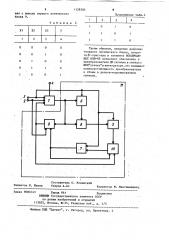

Устройство содержит реверсивный счетчик 1, вход управления которого соединен с входом 2 устройства, вход синхронизации соединен с шиной 3 синхронизации, выходы реверсивного счетчика 1 являются выходом 4 устрой. ства, счетчик 5, первый и второй Ртриггеры 6 и 7, элемент 8 ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ, первый и второй логические блоки 9 и 10, причем шина 3 синхронизации соединена с входом счетчика 5 и входами синхронизации первого и второго 2 -триггеров 6 и 7, а выход старшего разряда реверсивного счетчика 1 подключен к первому входу первого логического блока 9, к первому входу элемента 8 ИСКЛЮЧАЮЩЕЕ

ИЛИ-HE и к входу первогоЮ -триггера

6, выход которого соединен с вторым входом элемента 8 ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ, выход которого подключен к входу установки в "0" счетчика 5, а выход счетчика 5 — к первому входу второго логического блока 10, выход которого соединен с 3 -входом второго 0триггера 7, выход которого подключен к вторым входам первого и второго логических блоков 9 и 10, третий вход первого логического блока 9 подключен к входу 2 устройства, а выход — к входу запрета счета реверсивного счетчика 1 и третьему входу второго логического блока 10.

Счетчик 5, D -триггеры 6 и -7, элемент 8 ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ, блоки 9 и 10 образуют блок 11 автоматического уменьшения уровня постоянной составляющей в выходном ИКМ сигнале.

Устройство работает следующим образом.

3 11283

Входной сигнал в виде ДМ последо.вательности поступает на вход управ-. ления реверсивного счетчика 1, который является и входом 2 устройства.

Реверсивный счетчик 1 может быть любым реверсивным счетчиком, который имеет вход управления направлением- счета, вход управления запрета счета и вход синхронизации, на который с шины 3. синхронизации поступают 10 синхроимпульсы, выходной ИКМ код снимают с выходов реверсивного счетчика 1, которые являются выходом ч устройства.

Вход управления запрета счета ре,версивного счетчика 1 подключен к выходу блока 11 автоматического уменьшения уровня постоянной составляющей в выходном ИКМ сигнале. Работа блока

11 основана на определении того, измеияется ли знак (старший разряд реверсивного счетчика 1) выходного

ИКМ сигнала в режиме молчания за период Т > 1/f, где f — наименьшая частота передаваемого сигнала.

Период Т определяется коэффициентом пересчета счетчика 5, который делит частоту синхроимпульсов. Счетчик 5 может быть счетчиком любого типа требуемой разрядности с выхо30 дом дешифрации состояния заполнения и входом установки в "0". 0 1 !

В зависимости от знака HEM сигна1 ла на конец периода Т и от уровня входного ДМ сигнала блоком 11 авто- 35 матического уменьшения уровня постоянной составляющей вырабатывается дополнительный сигнал, управляющий работой реверсивного счетчика 1, 1 такой, 4то в случае, если старший 40 разряд реверсивного счетчика не из- 1 меняет своего значения за период Т, состояние реверсивного счетчика 1 изменяется на единицу младшего разряда в сторону уменьшения постоянной 45 составляюшей. Фиксация ИКМ сигнала в двух соседних тактах синхронизации осуществляется первыми -триггером 6, фиксация сигнала с выхода счетчика

5, означающего, что прошел период Т,, 50 осуществляется вторым U- триггером 7.

Оба l3 -триггера являются синхронными

D-триггерами, на входы синхрониза,ции которых подаются инхроимпульсы с шины 3 синхронизации. Если за пери-Я од Т происходит изменение знака ИКМ сигнала, тс элементом 8 ИСКЛЮЧАРЩЕЕ ,ИЛИ-НЕ вырабатывается сигнал, сбрасы85 4 вающий в "0" счетчик 5. В этом случае не происходит фиксации вторым Dтриггером 7 сигнала, сообщающего об истечении периода Т. Сигнал, дополнительно управляющий работой реверсивного счетчика 1 по входу запрета счета, вырабатывается первым логическим блоком 9. Это комбинационное устройство, которое в зависимости от выбранной элементной базы может реализовываться на тех или иных логических элементах в соответствии с таблицей истинности его работы (табл. 1), где У вЂ” выходной .сигнал первого логического блока 9,. причем нулем закодирован сигнал "Счет разрешен", а единицей — "Запрет счета";

X1 — сигнал на выходе старшего разряда реверсивного счетчика 1; Х2— сигнал на выходе второго2 -триггера 7; ХЗ вЂ” входной ДМ сигнал.

Т а б л и ц а 1

ХЗ у

0 0

1 0

0 0

0

Второй логический блок 10 необ1 ходим для. записи во второй3 -триггер

7 сигнала с выхода счетчика 5 и. уста. новки этого триггера в первоначальное состояние после того, как реализуется функция по дополнительному управлению реверсивным счетчиком

Второй логический блок 10 также является комбинационной схемой, реализация котооой может быть осуществлена на основе таблицы истинности(табл.2), где У вЂ” выходной сигнал второго логического блока 10; Х1 — сигнал с выхода счетчика 5; Х2 — сигнал с выхода второго3 -триггера 7; ХЗ вЂ” сиг1128385 нал с выхода первого логического блока 9.

Продолжение табл.2

Э 4

Таблица 2, 0

Х1 Х2

ХЗ у

Таким образом, введение дополнительного логического блока, второro3 -триггера и элемента ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ позволяет обеспечить в преобразователе ДМ сигнала в сигнал с

ИКМ"утечку"в интеграторе,что повышает помехоустойчивость преобразователя к сбоям в дельта-модулированном сигнале.

0

0

0

Тираж 861 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ 9083/43 филиал ППП "Патент", г. Ужгород, ул. Проектная, 4

Составитель О. Ревинский

Редактор И. Шулла Техред А.Ач Корректор И. Максимишинец