Устройство для контроля амплитудных характеристик

Иллюстрации

Показать всеРеферат

1. УСТРОЙСТВО ДЛЯ КОНТРОЛЯ АМПЛИТУДНЫХ ХАРАКТЕРИСТИК, содержащее источник линейно-убывающего п ступенчатого напряжения, выход которого подключен к входной клемме устройства , детектор, вход которого под ключей к выходной клемме устройства, и регистратор,о тличающееся тем, что, с целью сокращения времени контроля, в него введены блок памяти. линейный делитель напряжения, п-1 элементов сравнения и ключей, элемент ИЛИ и адаптивный блок синхронных импульсов , при этом первый выход детектора подключен к первым входам элементов сравнения и к входу блока памяти, выход которого подключен к входу линейного делителя напряжения,а п-1 выходов делителя напряжения соединены с вторьми входами элементов сравнения, выход каждого элемента сравнения через соответствующий ключ подключен к входу элемента ИЛИ, выход которого соединен с входом регистратора, второй выход детектора подключен к входу адаптивного блока синхронных импульсов , п-1 выходов которого соединены 5g с управлякяцими входами ключей, а п-й выход подключен к управляющему сЛ входу блока памяти.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

Ф (19) (11) ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCKOMY СВИДЕТЕЛЬСТВ!Ф

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

IlO ДЕЛАМ ИЗОБРЕТЕНИЙ И OTHPblTHA (21) 3619563/24-21 (22) 11.07.83 (46) 15.12.84. Бюл.)146 (72) В.Г.Чащин и И.Н.Криворучко (53) 621.317.757(088.8) (56) 1.Авторское свидетельство СССР

9 987827, кл. Н 04 В 3/46, 1981.

2. Авторское свидетельство СССР

9 842635, кл. G 01 R 27/28, 1979 (прототип). (54)(57) 1. УСТРОЙСТВО ДЛЯ КОНТРОЛЯ

АМПЛИТУДНЫХ ХАРАКТЕРИСТИК, содержащее источник линейно-убывающего () ступенчатого напряжения, выход которого подключен к входной клемме устройства, детектор, вход-которого подключен к выходной клемме устройства, и регистратор,о т л и ч а ю щ е е с я тем, что, с целью сокращения времени контроля, в него введены блок памяти, Ц51) G 01 R 27 28; Н 04 В 3/46 линейный делитель напряжения,п-1 элементов сравнения и ключей, элемент

ИЛИ и адаптивный блок синхронных импульсов, при этом первый выход детектора подключен к первым входам элементов сравнения и к входу блока памяти, выход которого подключен к входу линейного делителя напряжения,а р -1 выходов делителя напряжения соединены с вторыми входами элементов сравнения, выход каждого элемента сравнения через соответствующий ключ подключен к входу элемента ИЛИ, выход которого соединен с входом регистратора, второй выход детектора подключен к входу адаптивного блока синхронных импульсов, и-1 выходов которого соединены Е с управляющими входами ключей, а и-й выход подключен к управляющему входу блока памяти.

С::

1129555

2. Устройство по п.1, о т л и— ч а ю щ е е с я тем, что адаптивный блок синхронных импульсов выполнен в виде формирователя напряжения, вход которого является входом блока, а. выход формирователя подключен к входу триггера коммутации блока паИзобретение относится к технике измерений и может быть использовано для контроля амплитудных характеристик каналов связи с переменными параметрами. 5

Известно устройство для измерения амплитудной характеристики канала связи многоканальной системы,:которое содержит генератор синусоидального сигнала, аттенюатор и последовательно соединенные генератор импульсного сигнала и преобразователь частоты, блок Регулировки уровня и последовательно соединенные первый квадратор, первый интегратор и второй квадратор и последовательно соединенные третий квадратор, второй интегратор и измеритель отношений уровней, при этом выход гвнератора синусоидального сигнала соединен с вторым входом преобразователя частоты, выход которого соединен с входом аттенюатора, выход блока регулировки уровня соединен с входом первого квадратора, выход которого соединен с входом третьего квадратора, а выход второго квадратора соединен с вторым входом измерителя отношения уровней (1) .

Однако это устройство характеризуется недостаточными скоростью и точностью измерений.

Наиболее близким к предлагаембму ,является измеритель амплитудных характеристик, содержащий источник ступенчато меняющегося напряжения, выход которого подключен к йсследуемому и эталонному четырехполюсникам, последовательно соединенные детектор, коммутатор и интегратор, а также источник опорного напряжения, выход 40 которого соединен с коммутатором, последовательно..соединенные делитель, дополнительный коммутатор и логарифмический усилитель, последовательно соединенные управляемый генератор, 45 реверсивный счетчик и регистрирующий узел, причем выходы эталонного и исследуемого четырехполюсьиков подключены к дополнительному коммутатору и делителю соответственно, выход логарифмического уси.лителя — к мяти, выход которого является и-м входом блока, и к и-1 входам тригге-. ров-формирователей времени, выход каждого из которых соединен с входом соответствующего триггера-формирователя управляющих напряжений, выходы которых являются и-1 выходами блока. детектору, а выход интегратора — к управляемому генератору j21 .

Недостатками этого устройства являются низкая точность измерений и значительное время контроля. . Цель изобретения — сокращение времени контроля амплитудных характеристик каналов связи с переменными параметрами.

Цель достигается тем, что в устройство для контроля амплитудных характеристик, содержащее источник линейно убывающего и-ступенчатого напряжения, выход которого подключен к входной клемме устройства, детектор, вход которого подключен к выходной клемме устройства, и регистратор, введены блок памяти, линейный делитель напряжения, и-1 элементов сравнения и ключей, элемент ИЛИ и адаптивный блок синхронных импульсов, при этом первый выход детектора подклю- чен к первым входам элементов сравнения и к входу блока памяти, выход которого подключен к входу линейного делителя напряжения, а и-1 выходов делителя напряжения соединены с вторыми входами элементов сравнения, выход каждого элемента сравнения через соОтветствующий ключ подключен к входу элемента ИЛИ, выход которого соединен с входом регистратора, второй выход детектора подключен к входу адаптивного блока синхронных импульсов, и-1 выходов которого соединены с управляющими входами ключей, а и-й выход подключен к управляющему входу блока памяти.

При этом адаптивный блок синхронных импульсов выполнен в виде формирователя напряжения, вход которого является входом блока, а выход формирователя подключен к входу триггера коммутации блока памяти, выход которого является и-м выходом блока, и к И -1 входам триггеровформирователей времени, выход каждого из которых соединен с. входом соответствующего триггера-формирователя управляющих напряжений, выходы которых являются h -1 выходами блока.

1129555

25 а б

В г д е

t

t.

)"аг. 2

Составитель Л. Муранов

Техред Л.Микеш Корректор A.Òÿcêo

Редактор Н.Киштулинец

Заказ 9445/36 Тираж 710 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5

Филиал ППП Патент, г.ужгород, ул.Проектная, 4

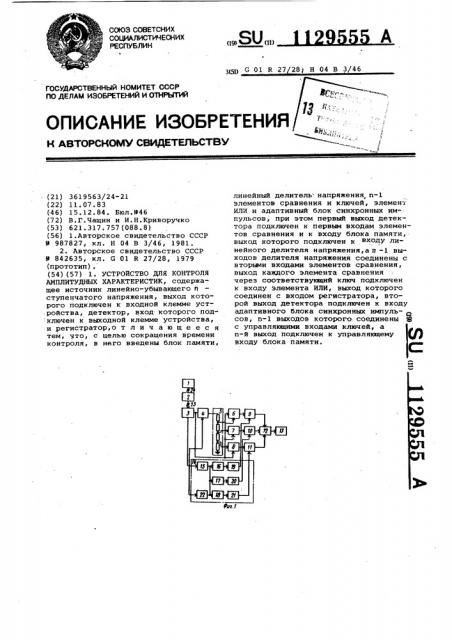

На фиг.1 представлена структурная схема устройства; на фиг.2 временные диаграммы напряжений в различных узлах устройства.

Устройство содержит источник 1 линейно убывающего И -ступенчатого напряжения, объект 2 контроля, детектор 3, выходом соединенный с входЬм блока 4 памяти, линейный двигатель 5 напряжения, элементы 6,7 и

8 сравнения, первые входы которых соединены с соответствующим выходом линейного делителя 5 напряжения, а вторые входы — с выходом детектора ,3, ключи 9, 10 и 11, входы которых соединены с соответствующими вы- 15 ходами элементов 6,7 и 8 сравнения, а выходы — с входами элемента 12 ИЛИ, регистратор .13, входом соединенный с выходом элемента 12 ИЛИ, адаптивный блок 14 синхронных импульсов, включающий в себя формирователь 15 напряжения, триггеры-формирователи

16,17 и 18 времени, триггеры-формирователи 19,20 и 21 управляющих напряжений и триггер 22 коммутации блока памяти, входная 23 и выходная

24 клеммы устройства.

Устройство работает следующим образом.

На вход .детектора 3 поступает контрольный сигнал в виде последовательности равномерно убывающих ступенчатых напряжений. С выхода детектора огибающая контрольного сигнала поступает на вход блока 4 памяти и на входы элементов 6,7 и 8 сравнения. В блоке памяти определяется величина первой максимальной ступеньки контрольного напряжения и сохраыяется на весь цикл измерений.

Это напряжение делится равномерно 4р на долевые части в линейном делителе 5 напряжения, вырабатывая как бы

I эталонный сигнал по равномерности характеристики. Количество частей определяется количеством ступенек контрольного сигнала. С выходов делителя напряжение поступает на вто" рые входы элементов 6,7 и 8 сравне ния. Таким, образом, на одних входах элементов сравнения постоянно присутствуют напряжения ступенек квазиэталонного напряжения, а на других входах — напряжения ступенек непосредственно с выхода детектора. Результат сравнения через ключи 9,10

1 и 11 и элемент 12 ИЛИ поступает на регистратор 13. Когерентность работы элементов устройства обеспечивается адаптивным блоком 14 синхронных импульсов. С этой целью напряжение со второго выхода детектора поступает на вход формирователя 15, который вырабатывает напряжение, определяющее начало цикла, контроля (фиг.2а), и запускает триггеры-формирователи а

16,17 и 18 и т.д. (фиг.2б,г,е), которые определяют последовательность и момент пробы результатов сравнения каждой ступеньки напряжения.

Задним фронтом эти триггеры запускают триггеры-формирователи 19,.20 и 21 и т.д. (фиг.2в,д,ж), которые определяют временную продолжительность пробы . и управляют ключами

9,10 и 11 и т.д. По окончании контрольного напряжения формирователь 15 вырабатывает импульс, запускающий триггер 22 (фиг.2з), который освобождает блок памяти от контрольного напряжения и подготавливает его к следующему циклу.

Предлагаемое устройство обеспечивает сокращение времени контроля амплитудных характеристик в каналах связи с переменными параметрами до единиц секунд.