Интерполятор

Иллюстрации

Показать всеРеферат

ИНТЕРПОЛЯТОР, содержащий . регистр аргумента и два блока памяти, отличающийся тем, что, с целью сокращения затрат аппаратуры за счет уменьшения требуемого объема памяти, в него введены дешифратор, шифратор, матричный умножитель, элемент ИЛИ и два коммутатора, причем входы регистра аргумента соедийены с входами интерполятора, первая группа выходов регистра аргумента соединена с первой группой информационных входов первого коммутатора и входами дешифратора, выходы которого подключены к входам элемента ИЛИ и входам щифратора, выходы которого соединены с входами старших разрядов адреса первфго и второго блоков памяти, входы младших разрядов адреса которых подключены к выходам первого коммутатора , вторая группа выходов регистра аргумента соединена с второй группой информационных входов первого коммутатора и старшими разрядами первой группы информационных входов второго коммутатора, выход которого подключен к первому входу матричного умножителя, второй вход которого подключен к выходу первого блока памяти, а третий вход - к выходу вторрга блока памяти, выход матричного умножителя соединен с выходом интерполятора, (Л третья группа выходов регистра аргумента соединена с входами младших разрядов первой группы информационных входов и входами старших разрядов второй группы информационных входов второго коммутатора, входы младших разрядов второй группы информационных входов которого подключены к шине логического нуля интерполятора, выход элемента ИГШ соединен с управляющими входами первого и второго коммутаторов .

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН

„SU„„112 622

gyp G 06 F 15/353

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н ABTOPCHOMV СВИДЕТЕЛЬСТВУ (21) 353525 1/24-24 (22) 10.01.83 (46) 15.12,84. Бюл. № 46 (72) А.В. Анисимов, А.В. Крайников, Б.А. Курдиков и В.Б. Смолов (71) Ленинградский ордена Ленина электротехнический институт им. В.И. Ульянова (Ленина) (53) 681.321(088.8) (56) 1. Авторское свидетельство СССР №- 736076, кл. С 07 F 15/32, 1977.

2. Патент Великобритании № 2010545, кл. С 06 F 15/32, опублик.

1975 (прототип). (54)(57) ИНТЕРПОЛЯТОР, содержащий регистр аргумента и два блока памяти, отличающийся тем, что, с целью сокращения затрат аппаратуры за счет уменьшения требуемого объема памяти, в него введены дешифратор, шифратор, матричный умножитель, элемент ИЛИ и два коммутатора, причем входы регистра аргумента соединены с входами интерполятора, первая группа выходов регистра аргумента соединена с первой группой информационных входов первого коммутатора и входами дешифратора, выходы которого подключены к входам элемента ИЛИ и входам шифратора, выходы которого соединены с входами старших разрядов адреса первого и второго блоков памяти, входы младших разрядов адреса которых подключены к выходам первого коммутатора, вторая группа выходов регистра аргумента соединена с второй группой информационных входов первого коммутатора и старшими разрядами первой группы информационных входов второго коммутатора, выход которого подключен к первому входу матричного умножителя, второй вход которого под.ключен к выходу первого блока памяти, а третий вход — к выходу вторрго-блока памяти, выход матричного умножителя соединен с выходом интерполятора, третья группа выходов регистра аргумента соединена с входами младших разрядов первой группы информационных .входов и входами старших разрядов С2 второй группы информационных входов второго коммутатора, входы младших разрядов второй группы информационных

° б входов которого подключены к шине логического нуля интерполятора, выход элемента ИЛИ соединен с управляющими входами первого и второго ком- фф мутаторов. Ю

1129622

Изобретение относится к вычислительной технике.

Известен цифровой генератор функции f1 3, в котором для воспроизведения функции используются три первых члена ряда Тейлора, что позволяет заменить вычисляемую функцию f(x) формулой (х1 g 10

Цх) = (х,+ x)=f (х,) г (x,)ах+ — (и), Ъ где fix ) — значение функции в точО ке х

f (х ) — значение первой производ- 15 о ной функции;

f (õ ) — значение второй производо ной функции.

Недостатком известного генератора

20 является использование для генерирования функции Ряда Тейлора, что ограничивает область его применения и не позволяет использовать это устройство для воспроизведения функций, получа25 емых в результате экспериментальных исследований и не имеющих аналитического описания нелинейной зависимости, Наиболее близким к предлагаемому является устройство для расчета. совокупности интерполяционных значений, содержащее процессор, блок памяти, схему адресации и вычислительную схему, которая состоит из регистра аргумента, сумматора, счетчика и вычислительного блока, причем выходы регист- 35 ра аргумента соединены с входами вычислительного блока и схемы адресации, выходы которой подключены к входам блока памяти, выходы которого подключены к входам вычислительного 40 блока, выходы которого соединены с входами сумматора и счетчика (2 ).

Недостатком этого устройства является то, что оно позволяет интерполировать функции только с равноуца-45 ленным расположением узловых точек, что удобно при воспроизведении ряда элементарных. функций, но приводит к неэффективному использованию памяти вычислительной системы при воспро-50 изведении нелинейных зависимостей, снимаемых экспериментально и имеющих особенности, обуславливающие необходимость применения неравноудаленного расположения узловых точек, к числу 55 которых, в первую очередь, относятся импульсные выбросы и резкие изменения производных функции.

Цель изобретения — сокращение затрат аппаратуры за счет уменьшения

1 требуемого объема памяти, Поставленная цель достигается тем, что в интерполятор, содержащий регистр аргумента и два блока памяти, введены дешифратор, шифратор, матричный умножитель, элемент ИЛИ и два коммутатора, причем входы регистра аргумента соединены с входами интерполятора, первая группа выходов регистра аргумента соединена с первой группой информационных входов первого коммутатора и входами дешифратора, выходы которого подключены к входам элемента ИЛИ и входам шифратора, выходы которого соединены с входами старших разрядов адреса первого и второго блоков памяти, входы младших разрядов адреса которых подключены к выходам первого коммутатора, вторая группа выходов регистра аргумента соединена с второй группой информационных входов первого коммутатора и старшими разрядами первой группы информационных входов второго коммутатора„ выход которого подключен к первому входу матричного умножителя, второй вход которого подключен к выходу первого блока памяти, а третий вход — к выходу второго блока памяти, выход матричного умножителя соединен с выходом интерполятора, третья группа выходов регистра аргумента соединена с .входами младших разрядов первой группы информационных входов и входами старших разрядов второй группы информационных входов второго коммутатора, входы младших разрядов второй группы информационных входов которого подключены к шине логического нуля интерполятора, выход элемента

ИЛИ соединен с управляющими входами первого и второго коммутаторов.

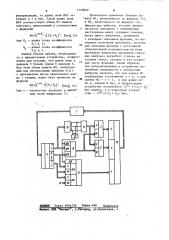

На чертеже схематически представлен предлагаемый интерполятор.

Интерполятор содержит процессор 1, первый и второй блоки 2 и 3 памяти, регистр 4 аргумента с первой, второй и третьей группами выходов 5, 6 и 7 соответственно, первый и второй коммутаторы 8 и 9, дешифратор 10, шифратор 11, матричный умножитель 12, элемент ИЛИ 13.

Устройство работает следующим образом.

Интерполяция функции Z(x), заданной на множестве точек х„, х>, хз, 1129622 где Х « Х Х +., 1 если Х = 1» .

r-X-X =

1 если Х 4 L з я j >

Adr, =

3 х;... х „двумя координатами Е (x ) и Г .(х ), производится на основе формул линейной интерполяции. Особенностью предлагаемого уст-. ройства является возможность уменьшить расстояние между узловыми точками функции путем включения дополнительных узловых точек между 1 парами равномерно расположенных узлов интер-. полируемой функции. Количество пар 10 узлов 1, между которыми уменьшается расстояние между узловыми точками, и их номера определяются количеством выходов дешифратора 10, поданных на шифратор 11, и их номерами. Количест- 15 во узловых точек, вставляемых между каждой парой узлов, постоянно и равно 2 b †. 1, где Ь вЂ” количество разрядов выходов 6. При выполнении интерполяции разряды выходов 6 используются либо для адресации памяти, либо в виде части аргумента интерполяционной формулы. Интерполяционная формула, используемая в устройство, имеет вид 25 (1= =„(i) Р (";)г () где Ь вЂ” количество разрядов вьгкодов 8; . с — количество разрядов выходов 7;

«а

ХЯ вЂ” код, выдаваемый с выходов 5, h. — одно из значений кода Х» определяющее участок с уменьшением расстояния между узловыми точками. 45

Вычисление адреса функции Р„(х.) и Р (Х ) Ас1г2 производится на осйо1 ванин выраженйй вида

В=ХА /=О, если ХяФ, (1 5О слй Х,= L.

1 1 А j где V — - старшие разряды адреса блоков 2 и 3 памяти;

W — - младшие разряды адреса блоков 2 и 3 памяти;

Х вЂ” код, выдаваемый с выходов 6.

Реализация интерполяционных выражений (1), (2), (3) и адресной функции (4) производится в предлагаемом устройстве следующим образом., При поступлении аргумента на регистр 4 при помощи дешифратора 10 определяется, относится ли данное значение кода к участку с основным или уменьшенным расстоянием между узловыми точками.

Если код относится к участку с основным расположением узловых точек, то на выходе элемента ИЛИ, на который подаются выходы дешифратора, появляется нулевой сигнал, поступающий на входы управления коммутаторами

8 и 9. При этом на выход коммататора

8 подается код с выходов 5, а на выход коммутатора 9 — конкатенация (объединение} кодов выходов 6 (старшие разряды) и выходов 7 (младшие разряды). Выход коммутатора 8 подается на адресные входы блоков 2 и 3, где поступает на входы W младших разрядов адреса, на входы Ч старших разрядов адреса поступает выходной сигнал шифратора 11, на который подаются выходы дешифратора 10, со1 ответствующие интервалами с уменьшенным расстоянием между узловыми

i точками. Такое распределение кодов на шинах устройства обеспечивает аппаратурную реализацию уравнений (1), (2), (3) и (4) для случая Х, 4сК.

В противном случае на выходе элемента ИЛИ 13 присутствует единичный сигнал и на выходах коммутаторов 8 и 9 появляются коды, обеспечивающие аппаратную реализацию уравнений (1}, (2), (3) и (4) для случая Х„= L.

На выход коммутатора 8 выдается код с выходов 6, а на выходе коммутатора 9 — код с выходов 7 (старшие разряды), объединенный с кодом, состоящим из нулей (младшие разряды).

Результат вычислений по интерполяционной формуле (1) формируется, на выходе матричного умножителя 12 и подается в процессор 1.

По сравнению с прототипом в предлагаемом устройстве достигается экономия в объеме памяти констант, что доказывают следующие расчеты.

Если использовать известное уст1 ройство и на всем интервале изменения аргумента обеспечить уменьшенное расстояние между узлами, необходимое для обеспечения требуемой точности

1129622

B2(HK28 Заказ 9454/39 Зубак 698 Поииисиаа

ы аи нтерполяции9 то длина поля NPS со)ставит а + Ь бит. Такой длине поля

МРБ соответствует объем Ю памяти констант, вычисляемый в соответствии с формулой 5

М! ° (2 -1) (5 +52) I (бита (5) где S — длина слова коэффициента

1.

F,(Х, );

S - длина слова коэффициента

F2(Xi )

Оценку объема памяти, необходимого в предлагаемом устройстве, осуществляем при условии, что длин) поля а вьимдов 5 больше длины Ь выходов 6.

При этом объем памяти N2, необходимый для интерполяции функции Е()() с уменьшенным шагом квантования между 1 узлами, может быть вычислен по формуле 4(24 - ) (1 З) ) (бит4 (6) з

)) ge r — количество разрядов в выход ном слове шифратора 11.

Произведем сравнение объемов па1 мяти М1, вычисляемого по формуле (5), и N2, вычисля емо го по формуле (6 ) .

Импульсные выбросы, которые предполагается описывать с уменьшенным расстоянием между узловыми точками, могут иметь амплитуду, сравнимую с исходным значением функции, на интервале изменения аргумента, поэтому для описания функции с постоянной относительной погрешностью на всем интервале изменения аргумента описание импульса потребует столько же узловых точек, сколько и вся остальная часть функции. Таким образом, при воспроизведении в устройстве нелинейной зависимости с импульсным выбросом получим, что при оценке N) справедливо соотношение а = Ь, а при оценке N2 — r -= -1, и при длине поля а, равной 8 бит, в предлагаемом устройстве потребуется (29- 1)(Б + S )

1 2 бит памяти, а в известном устройстве — (2 -1)(S + S2) бит.