Запоминающее устройство с обнаружением ошибок

Иллюстрации

Показать всеРеферат

ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ОБНАРУЖЕНИЕМ ОШИБОК, содержащее накопитель, входы которого подключены соответственно к выходам адресного регистра и к выходам первого информационного регистра, а выходы - к входам второго информационного регистра, первый и второй блоки свертки по модулю два, выходы которых соединены с входами сумматора по модулю два, элементы ИЛИ, выходы которых подключены к входам второго блока свертки по модулю два, а одни из входов - к выходам второго информационного регистра , и счетчик, причем входы первого блока свертки по модулю два и адресного регистра являются адресными входами устройства, другие входы элементов ИЛИ и входы первого информационного регистра являются информационными входами устройства, информационными выходами которого являются выходы второго информационного регистра , отличающееся тем, что, с целью упрощения устройства, в него введены триггер, элемент И-ИЛИ-НЕ, элемент И, элемент И-НЕ и ключи, причем выход элемента И-ИЛИ-НЕ подключен к первому тактовому входу счетчика, первый вход - к первому управляющему входу накопителя, а .второй вход - к выходу сумматора по модулю два и первому входу элемента И, второй вход которого соединен с вторым управляющим входом накопителя, а выход - с первым входом элемента И-НЕ и третьим входом элемента И-ИЛИ-НЕ, четвертый вход которого подключен к прямому I выходу триггера, инверсный выход которого соединен о вторым входом элемента И- (Л НЕ, выход которого подключен к второму тактовому входу счетчика, выход обратного переноса которого соединен с тактовым входом триггера, вход сброса которого подключен к выходу первого ключа, вход сброса счетчика подключен к выходу второго ключа , первые входы ключей соединены с щиной нулевого потенциала, второй вход первого ю ключа и управляющие входы накопителя явсо а ляются управляющими входами устройства, контрольными выходами которого являются счетные выходы счетчика. 01 сд

COIO3 СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

G 11 С 2900

ОПИСАНИЕ ИЗОБРЕТЕНИ

К А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ

«3 "«

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3603463/24-24 (22) 09.06.83 (46) 15.12.84. Бюл. № 46 (72) Л. В. Дербунович и И. Г. Либерг (71) Харьковский политехнический институт им. В. И. Ленина (53) 681.327 (088.8) (56) 1. Авторское свидетельство СССР № 672655, кл. G 11 С 29/00, 1978.

2. Авторское свидетельство СССР № 88i876, кл. G 11 С 29/00, 1980 (прототип). (54) (57) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ОБНАРУЖЕНИЕМ ОШИБОК, содержащее накопитель, входы которого подключены соответственно к выходам адресного регистра и к выходам первого информационного регистра, а выходы — к входам второго информационного регистра, первый и второй блоки свертки по модулю два, выходы которых соединены с входами сумматора по модулю два, элементы ИЛИ, выходы которых подключены к входам второго блока свертки по модулю два, а одни из входов— к выходам второго информационного регистра, и счетчик, причем входы первого блока свертки по модулю два и адресного регистра являются адресными входами устройства, другие входы элементов ИЛИ и входы первого информационного регистра являются

„„SU„„1129655 A информационными входами устройства, информационными выходами которого являются выходы второго информационного регистра, охличаюи ееся тем, что, с целью упрощения устройства, в него введены триггер, элемент И вЂ” ИЛИ вЂ” НЕ, элемент И, элемент

И вЂ” НЕ и ключи, причем выход элемента

И вЂ” ИЛИ вЂ” НЕ подключен к первому тактовому входу счетчика, первый вход — к первому управляющему входу накопителя, а второй вход — к выходу сумматора по модулю два и первому входу элемента И, второй вход которого соединен с вторым управляющим входом накопителя, а выход— с первым входом элемента И вЂ” НЕ и третьим входом элемента И вЂ” ИЛИ вЂ” НЕ, четвертый вход которого подключен к прямому выходу триггера, инверсный выход которого соединен вторым входом элемента И—

НЕ, выход которого подключен к второму тактовому входу счетчика, выход обратного переноса которого соединен с тактовым входом триггера, вход сброса которого подключен к выходу первого ключа, вход сброса счетчика подключен к выходу второго ключа, первые входы ключей соединены с шиной нулевого потенциала, второй вход первого ключа и управляющие входы накопителя являются управляющими входами устройства, контрольными выходами которого являются счетные выходы счетчика.

1129655

«(5

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам, и может использоваться для построения модулей оперативной памяти с обнаружением ошибок.

Известно запоминающее устройство с обнаружением ошибок, содержащее накопитель, входной и выходной регистры данных, адресный регистр, блоки свертки по модулю два, сумматоры, счетчики и вычитатель (1).

Однако известное устройство характеризуется большими аппаратурными затратами.

Наиболее близким техническим решением к изобретению является запоминающее устройство с обнаружением ошибок, содержащее накопитель, входы которого подключены к выходам адресного регистра и входного регистра данных, а выходы — к входам выходного регистра, данных, первый и . второй блоки сверток по модулю два, выходы которых соединены с входами сумматора, вход первого из них соединен с входом адресного регистра, являющимся первым входом устройства, а вход второго блока свертки по модулю два подключен к выходу элементов ИЛИ, входы которых соединены с выходом выходного регистра данных и входом входного регистра данных, являющимся вторым входом устройства, счетчик вход которого подключен к выходу сумматора, первый выход — к одному из входов вычитателя, выход которого является выходом устройства, а второй выход счетчика соединен с входом контрольного регистра, выход которого подключен к другому входу вычитателя (2).

Недостатками данного устройства являются большие аппаратурные затраты и, вследствии этого, низкая надежность работы, Кроме того, информация о количестве возникших ошибок поступает с выхода вычитателя в зависимости от содержимого счетчика и контрольного регистра то в прямом двоичном коде, то в инверсном, что значительно усложняет ее дальнейшую обработку и снижает эксплуатационные характеристики устройства.

Цель изобретения — упрощение устройства.

Поставленная цель достигается тем, что в запоминающее устройство с обнаружением ошибок, содержащее накопитель, входы которого подключены соответственно к выходам адресного регистра и к выходам первого информационного регистра, а выходы— к входам второго информационного регистра, первый и второй блоки свертки по модулю два, выходы которых соединены с входами сумматора по модулю два, элементы

ИЛИ, выходы которых подключены к входам второго блока свертки по модулю два, а одни из входов — к выходам второго информационного регистра, и счетчик, причем входы первого блока свертки по модулю

i5

35 два и адресного регистра являются адресными входами устройства, другие входы элементов ИЛИ и входы первого информационного регистра являются информационными входами устройства, информационными выходами которого являются выходы второго информационного регистра, введены триггер, элемент И вЂ” ИЛИ вЂ” НЕ, элемент И, элемент И вЂ” НЕ и ключи, причем выход элемента И вЂ” ИЛИ вЂ” НЕ подключен к первому тактовому входу счетчика, первый вход —. к первому управляющему входу накопителя, а второй вход — к выходу сумматора по модулю два и первому входу элемента И, второй вход которого соединен с вторым управляющим входом накопителя, а выход — с первым входом элемента И вЂ” НЕ и третьим входом элемента И вЂ” ИЛИ вЂ” НЕ, четвертый вход которого подключен к прямому выходу триггера, инверсный выход которого соединен с вторым входом элемента И вЂ” НЕ, выход которого подключен к второму тактовому входу счетчика, выход обратного переноса которого соединен с тактовым входом триггера, вход сброса которого подключен к выходу первого ключа, вход сброса счетчика подключен к выходу второго ключа, первые входы ключей соединены с шиной нулевого потенциала, второй вход первого ключа и управляющие входы накопителя являются управляющими входами устройства, контрольными выходами которого являются счетные выходы счетчика.

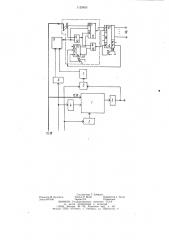

На чертеже представлена функциональная схема предложенного устройства.

Устройство содержит накопитель 1, первый 2 и второй 3 информационные регистры, адресный регистр 4, элементы ИЛИ 5, первый 6 и второй 7 блоки свертки по модулю два, сумматор 8 по модулю два, счетчик 9 с счетными выходами 10, элемент И вЂ” ИЛИ—

НЕ 11, элемент И вЂ” НЕ 12, элемент И 13, триггер 14. На чертеже обозначены первый

15 и второй 16 управляющие входы накопителя 1. Устройство содержит также первый

17 и второй 18 ключи. Элементы И вЂ” ИЛИ—

НЕ 11, И вЂ” НЕ 12, И 13 и триггер 14 могут быть выполнены на основе серийно выпускаемых микросхем типа К155 ИЕ7.

Устройство работает следующим образом.

В исходном состоянии счетчик 9 и триггер 14 сброшены в нуль. В режиме записи на входе 15 накопителя 1 появляется сигнал, соответствующий уровню логической

«1», который разрешает прохождение суммарного бита четности, поступающего с выхода сумматора 8 на вход «+ l» счетчика 9.

Если результирующий бит четности имеет единичное значение, то на выходе элемента

И вЂ” ИЛИ вЂ” HE 11 появляется отрицательный импульс, который своим передним фронтом увеличивает содержимое счетчика 9 на единицу. В режиме записи на входе 16 на1129655 копителя 1 находится постоянный уровень логического «О». Таким образом, выход элемента И вЂ” НЕ, 12, который соединен с вторым тактовым входом («-1») счетчика 9, находится в состоянии логической «1». В режиме считывания результирующий бит четности поступает через элементы И 13, И—

НЕ 12 на вход «-1» счетчика 9 и (в случае единичного значения) уменьшает состояние счетчика 9 на единицу. В это время выход элемента И вЂ” ИЛИ вЂ” НЕ 11 находится в сос- 1п тоянии логической «1». В режиме записи, который задается накопителю 1 по входам

15 и 16, счетчик 9 работает в режиме «Прямой счет». Код адреса и код записываемых данных подаются соответственно на входы регистра 4 и регистра 2 и осуществляется запись слова в соответствующую ячейку накопителя 1. Одновременно код адреса и код данных подаются соответственно на блок 6 и через элементы ИЛИ 5 на блок 7, которые вырабатывают биты четности адреса и 20 записываемых данных. При этом во всех разрядах регистра 3 хранится код «Все нули». Биты четности объединяются сумматором 8 в результирующий бит, который поступает в счетчик 9 через элемент И 13, элемент

И вЂ” ИЛИ вЂ” HE 11 и (в случае его единичного значения) увеличивает содержимое счетчика на единицу. Таким образом, к концу записи всего массива данных в накопитель 1 счетчик 9 фиксирует количество результирующих одиночных битов, равных единице.

Пока соответствующий массив данных хранится в накопителе 1, т. е. пока отсутствует обращение к накопителю 1, счетчик 9 устанавливается в режим хранения.

В режиме считывания в соответствии с сигналами на входах 15 и 16 накопителя 1 35 задается счетчику 9 режим «Обратный счет».

В каждом такте обращения соответствую- ° щее коду адреса число извлекается из накопителя 1 и поступает через регистр 3 на вы- ° ход устройства. Код адреса и код.считанных 4 данных подаются соответственно на блок 6 и через элементы ИЛИ 5 на блок 7, которые (как и при записи) вырабатывают биты четности адреса и считанных данных. При этом во всех разрядах регистра 2 хранится код «Все нули». Биты четности объединяют- 4 ся сумматором 8 в результирующий бит, который в случае единичного значения поступает через элемент И 13, элемент И вЂ” НЕ 12 в счетчик 9 и уменьшает его содержимое на единицу.

Если во время записи, хранения или считывания в запоминающем устройстве возникли ошибки, искажающие адресную или числовую информацию, то при считывании количество результирующих битов четности, принимающих единичное значение, будет меньшим или большим, чем при записи. Если число единичных результирующих битов четности при считывании меньше, чем при записи, то после окончания считывания всего массива данных в счетчике 9 будет находиться двоичный код, соответствующий суммарному количеству возникших ошибок.

Если же число единичных результирующих битов четности при считывании будет больше, чем при записи, то в момент обнуления счетчика 9 на его выходе обратного переноса появится импульс, который поступит в триггер 14 и через элемент И вЂ” ИЛИ—

НЕ 11 задает счетчику 9 режим «Прямой счет».

Таким образом, независимо от количества результирующих единичных битов четности в режимах записи и считывания счетчик 9 после завершения считывания всего массива данных содержит абсолютную разность результирующих единичных битов четности, которая равйа суммарному количеству возникших ошибок, и выдает информацию о количестве ошибок на выходы 10 устройства в прямом двоичном коде. С целью удобства считывания информации о количестве ошибок в том случае, когда число результирующих единичных битов при считывании больше, чем при записи, счетчик 9 переводится в режим «Прямой счет». Это происходит в момент обнуления счетчика 9, когда на его выходе обратного переноса появляется импульс, который переводит триггер 14 в единицу. После этого блокируется прохождение сигналов на вход «-1» счетчика 9 и разрешается прохождение через элемент И вЂ” ИЛИ вЂ” НЕ 11 на вход «+ 1» счетчика 9. Поэтому суммарное количество ошибок соответствует содержимому счетчика 9 и в любом случае подается на выходы 10 устройства в прямом коде.

В режиме хранения, когда отсутствует обращение к накопителю 1; входы 15 «Запись» и 16 «Считывание» накопителя 1 находятся в состоянии логического «О». Это приводит к тому, что на тактовых входах

«+ 1», «-1» счетчика 9 находятся уровни логической «1», что соответствует режиму хранения.

Аппаратурные затраты на реализацию вновь введенных триггеров 14, элемента И

13, элемента И вЂ” НЕ 12, элемента И вЂ” ИЛИ—

HE 11 не зависят от информационной емкости накопителя 1, и по стоимости и потребляемой мощности на порядок ниже, чем на реализацию регистра и блока вычитания в прототипе, например для накопителя емкостью 4К слов.

Технико-экономическое преимущество предлагаемого устройства по сравнению с прототипом состоит в его упрощении за счет сокращения объема оборудования примерно на 12 — 15% и, вследствие этого, в повышении надежности работы.

1129655

Редактор М. Келемеш

Заказ 8975/41

Составитель Т. Зайцева

Техред И. Верес Корректор А. Тяско

Тираж 574 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и оз крытий

l 13035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4